以FPGA机载为核心的实时视频图形处理系统设计

可编程逻辑

描述

随着科技的高速发展,飞机对机载电子系统提出了越来越高的要求,飞机性能的改善在很大程度上依赖于机载电子系统性能的提升。在飞行器机载电子系统中,显示系统是飞机与飞行员进行人机交互的桥梁,它将各种飞行参数转换为视觉信息,显示在显示器上。飞行员可以实时读取这些信息,从而做出判断。

文中设计了某机载视频图形处理系统的硬件电路部分,视频图形处理系统是机载显示系统的子系统,用于在机载显示器上显示高像素的图形与外部输入视频叠加形成的视频信号。系统以Xilinx公司的Virtex-5XC5VFX70T FPGA为核心处理器,搭配多种外围视频处理芯片,实现了对高清视频的缩放、格式转换和叠加高像素图形符号等多种处理功能,并且具有较高的实时性。

1 系统概况

1.1 系统需求

机载视频图形处理系统的主要功能是接收多种格式的外部视频信号,生成点阵式字符信号,进行视频格式的转换,并可输出生成字符与外视频叠加的视频信号。

系统接收PAL(Phase Alternating Line,逐行倒相)、DVI(Digital Visual Interface,数字视频接口)制式的视频信号和。PCI-E(Peri pheral Component Interconnect-Express,扩展外设部件互连标准)视频信号,对视频进行缩放、格式转换等处理后,叠加上高像素的图形,并按要求输出合成的视频信号。

1.2 总体方案设计

结合系统需求,确定系统的总体设计方案为:以Xilinx公司的Virtex-5 XC5VFX70T FPGA为核心处理器,利用其强大逻辑资源和丰富的IP核,配以相应的外部电路,构建出一个灵活、简洁、可靠的机载视频图形处理系统的嵌入式硬件模块。利用XC5VFX707T中内嵌的Power PC 440硬核处理器,在该处理器上移植美国风河公司的Vxworks操作系统,通过操作系统管理网络和PCI-E等接口,并在操作系统的基础上,实现相应的图形操作及视频处理API(Application Programming Interface,应用程序编程接口)函数,用户的应用程序通过调用API函数来构建最终的视频输出。

2 系统硬件模块设计

2.1 硬件整体架构

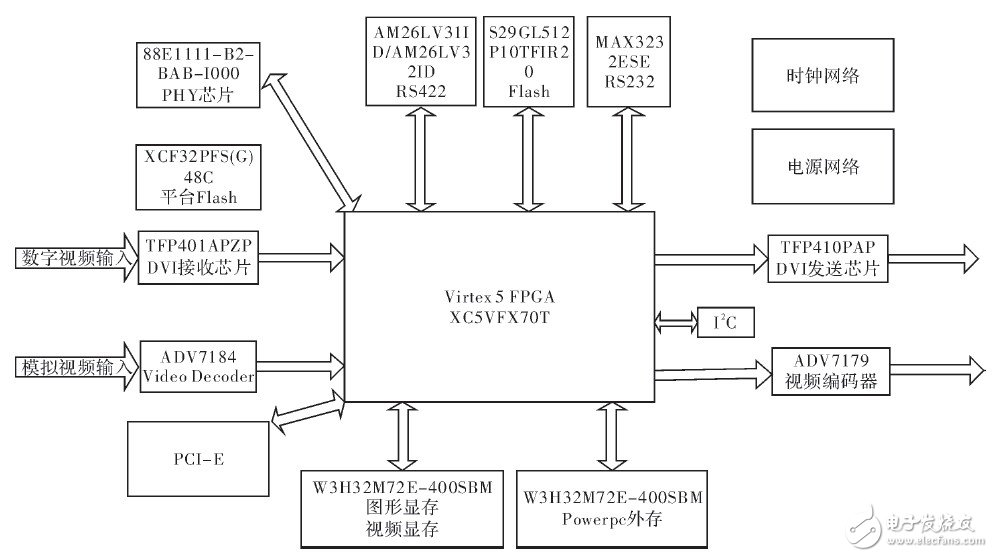

根据设计要求,选择XC5VFX70T FPGA作为核心处理器,该处理器采用65 nm工艺制造,是专为嵌入式应用而开发的。处理器内置主频550 MHz的PowerPC440内核、PCI-E端点和以太网等模块。系统硬件部分还包括视频编解码芯片,DDR2视频缓存,PowerPC外存等外围电路,整个系统的硬件框图如图1所示。

图1 系统硬件框图

2.2 视频流图

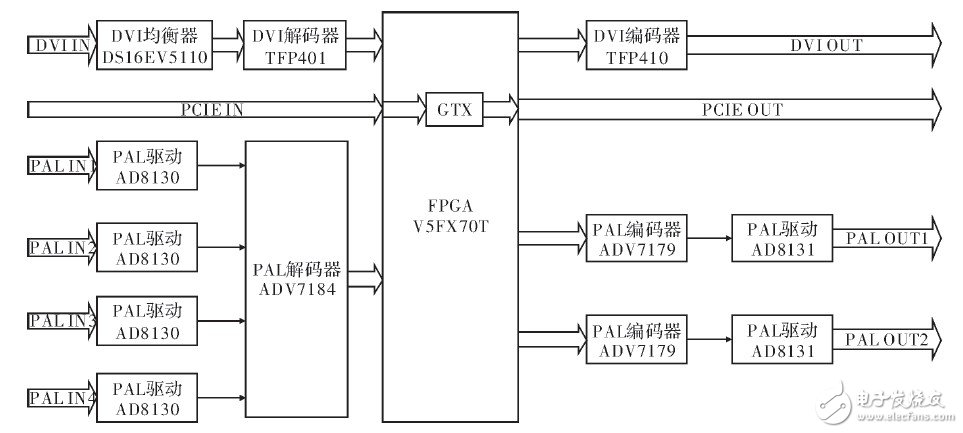

系统主要用于接收、处理并发送各种视频信号,系统中视频的流图如图2所示。由图中可知,系统能接收1路DVI视频,4路PAL视频和1路PCI-E视频,视频经过专门的解码器后,由FPGA对它们进行处理,然后通过相应的视频编码器输出视频信号。

图2 系统视频流向图

2.3 DVI视频编解码模块设计

系统的DVI视频解码采用TI公司的DVI解码芯片TFP401实现,该芯片满足DVI1.0规范,最高支持1 600×1 200分辨率,支持24位真彩色视频。另外考虑到机载视频信号源与DVI接收器之间距离较远,长线传输时信号的高频分量比低频分量衰减得更多,因此在DVI输入信号解码前加入均衡器以实现频谱的均衡化,减小信号失真。系统采用美国国家半导体公司的DS16EV5110实现DVI视频信号的频谱均衡化,该芯片可以对DVI视频信号的每一数据通道设定不同的均衡增益,具有高度的灵活性,可以有效减小信号的码间串扰。

系统的DVI视频输出功能采用TI公司的DVI编码芯片TFP410实现,该芯片满足DVI1.0规范,最高支持1 600×1 200分辨率,支持24位真彩色视频。

2.4 PAL视频编解码模块设计

为便于PAL视频信号的长线传输,系统采用差分信号传输PAL视频。由于标准的PAL信号为单端信号,因此系统在PAL信号接收端采用美国AD公司的差分接收放大器AD8130来实现差分PAL信号转换成标准单端PAL信号,而在PAL信号发送端则采用AD公司的高速差分驱动器AD8131实现单端PAL信号转换成差分信号。

系统采用AD公司的PAL解码芯片ADV7184对单端PAL视频信号进行解码,该芯片具有12个模拟输入通道,内置4个10位ADC,实际解码后视频信号支持ITU-R BT.656标准(YCrCb 4:2:2),经色彩空间转换后R、G、B分量均可达到8位分辨率,即PAL视频解码后可达24位真彩色。

系统采用AD公司的PAL编码芯片ADV7179来实现PAL视频信号的输出,该芯片支持ITU-RBT.656标准的标准数字视频输入,与PAL解码芯片ADV7184实现了很好的兼容,使得系统对PAL信号进行处理较为方便。ADV7179内置3个10位DAC,编码后输出视频支持24位真彩色。

2.5 DDR2视频缓存模块设计

由于系统中需要对输入的视频进行叠加字符及帧速率转换等处理,因此需要对输入的视频数据进行缓存。选择美国Mierosemi公司的DD R2 SDRAM芯片W3H32M72E-400作为视频缓存,该芯片存储容量为256 MByte,传输速率为50 MByte·s-1.

系统中需要处理的视频最高分辨率为1 600×1 200,因此一帧视频数据包含1 920 000个数据点,即大约2×106个数据点,而每个数据点占2 Byte存储空间,即一帧视频约占4 MByte存储空间。一片视频缓存芯片最少可存储64帧视频数据,满足一般的帧速率转换算法的存储空间需求。系统所选DDR2芯片的传输速率为50 MByte·s-1,因此视频最高传输速率为50×64/4=800帧·s-1.而系统中视频的最高刷新率为60 Hz,视频的最高传输速率已远大于输出视频的最高显示帧速率,符合系统的实时性要求。

3 测试结果及分析

在系统运行试验中,XC5VFX70T选取时钟频率200 MHz,屏幕分辨率为1 600×1 200,系统分别对图形生成和视频处理等功能进行了测试,并进行了系统联调。

在图形生成测试中,测试结果图如图3所示,图中分别显示了反走样直线、圆弧、圆和天地球,天地球上显示了一个直立字符和一个旋转字符,生成该幅画面共耗时984.6 μs,其中读写DDR2耗时862.7μs.当屏幕刷新率为60 Hz时,一幅画面允许的生成时间为16.7 ms,图形生成满足系统的实时性要求。

图3 图形生成测试结果图

在视频解码、处理、编码测试过程中,一帧视频的处理时间最长不超过3 ms,肉眼观察各种格式的视频输出时无明显时延,符合系统的实时性要求。在系统联调中,系统能输出叠加各种高像素符号图形的高清视频,输出分辨率可达1 600×1 200,输出视频场频可达60帧·s-1,输出视频质量高而流畅,无明显的干扰和延迟。

4 结束语

文中给出了基于FPGA的某机载实时视频图形处理系统的硬件电路总体设计方案,并详细论证了系统中DVI视频编解码模块,PAL视频编解码模块以及DDR2视频缓存模块的硬件实现方法。系统选用了多种新型芯片,构建了一个灵活、简洁、可靠的硬件平台,实现了对DVI、PAL等多种制式的视频的解码,实时处理和编码输出,并且具有较强的扩展性。系统测试结果表明,系统支持1 600×1 200分辨率,60帧·s-1刷新率,24位真彩色高清视频的流畅处理,对1帧视频的处理时间最长不超过3 ms,能够有效提高机载视频图形的处理速度,具有良好的应用价值。

-

基于FPGA多路机载冗余图像处理系统的设计方案2014-01-07 3831

-

基于FPGA的实时视频图像采集处理系统2018-02-10 20452

-

基于fpga的实时视频处理系统2014-04-08 1743

-

基于FPGA与DSP的视频处理系统设计2019-06-19 2112

-

基于FPGA的视频图形显示系统的DDR3多端口存储管理设计2019-06-24 2516

-

一种基于FPGA+DSP的视频处理系统设计2019-07-01 2281

-

FPGA实时视频图像处理系统的原理是什么?2019-08-22 3335

-

请问一下怎么设计一个基于FPGA的实时视频图像处理系统?2021-05-06 1120

-

基于FPGA的小型微光视频图像增强处理系统2009-01-11 578

-

基于FPGA的视频后处理系统2015-10-30 518

-

高效机载SAR实时成像处理系统设计2017-01-07 751

-

基于FPGA的图形生成与视频处理系统的设计与实现2017-11-18 3246

-

基于FPGA的视频图像处理系统的设计2017-11-22 5293

-

以FPGA和TMS320DM642为核心的实时图像采集和处理系统设计详解2018-07-16 3212

-

基于FPGA的机载视频图形显示系统设计2017-11-30 900

全部0条评论

快来发表一下你的评论吧 !