DAC12DL3200 12 位、低延迟、双通道 3.2GSPS 或单通道 6.4GSPS、RF 采样 DAC技术手册

描述

该DAC12DL3200是一款非常低延迟、双通道、射频采样数模转换器 (DAC),在双通道模式下的输入和输出速率高达 3.2 GSPS,在单通道模式下的输入和输出速率高达 6.4 GSPS。当使用多奈奎斯特输出模式时,DAC可以在接近8 GHz的载波频率下传输超过2 GHz的信号带宽。高输出频率范围可通过 C 波段 (8 GHz) 及更高频段进行直接采样。

该DAC12DL3200可用作双通道模式下的I/Q基带DAC。高采样率和输出频率范围也使DAC12DL3200能够进行任意波形生成(AWG)和直接数字合成(DDS)。集成的DDS模块支持片上单音和双音生成。

*附件:dac12dl3200.pdf

该DAC12DL3200具有并行LVDS接口,由多达48个LVDS对和4个DDR LVDS时钟组成。选通信号用于同步接口,该接口可以通过最低有效位 (LSB) 发送,也可以选择通过专用选通 LVDS 通道发送。每个LVDS对的速率高达1.6 Gbps。使用同步信号(SYSREF)支持多器件同步,并与JESD204B/C时钟器件兼容。SYSREF 窗口简化了多设备系统中的同步。

特性

- 12 位分辨率

- 最大输入和输出采样率:

- 单通道高达 6.4 GSPS

- 双通道高达 3.2 GSPS

- 多奈奎斯特工作模式:

- 单通道模式:NRZ、RTZ、RF

- 双通道模式:NRZ、RTZ、RF、2xRF

- 通过器件的低延迟:6 至 8 ns

- 将发射能力与低延迟接收器ADC12DL3200相匹配

- DAC 和 ADC 组合延迟 < 15 ns(不包括 FPGA)

- 并行 DDR LVDS 接口:

- 源同步接口可简化时序:

- 24 或 48 个 LVDS 对,最高可达 1.6 Gbps

- 每个 12 位总线 1 个 LVDS DDR 时钟

- 输出频率范围:> 8 GHz

- 满量程电流:21 mA

- 简化的时钟和同步

- SYSREF 窗口简化了设置和保持时间

- 片上直接数字合成器 (DDS)

- 单音和双音正弦波生成

- 32 个 32 位数控振荡器

- 快速跳频能力(< 500 ns)

- 同步CMOS频率/相位输入

- f 时的性能

外= 4.703 GHz,6.4 GSPS,射频模式- 输出功率:–3 dBm

- 本底噪声(70 MHz 偏移):–147 dBc/Hz

- SFDR:60 dBc

- 电源:1.0 V、1.8 V、–1.8 V

- 功耗:1.49 W(2 通道,射频模式,3.2 GSPS)

- 封装:256 引脚 FCBGA(17x17 mm,1 mm 间距)

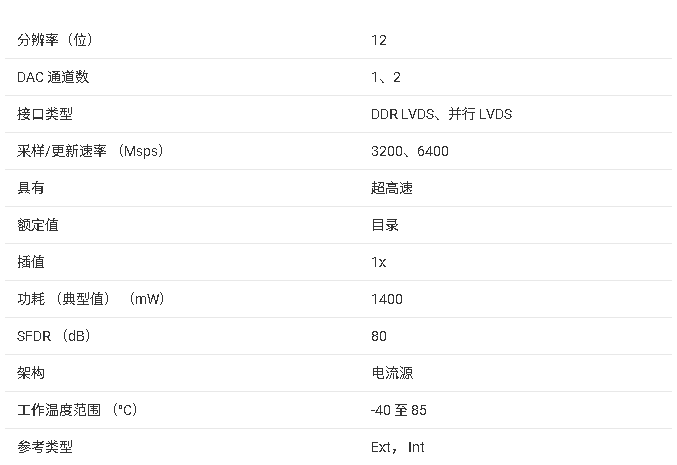

参数

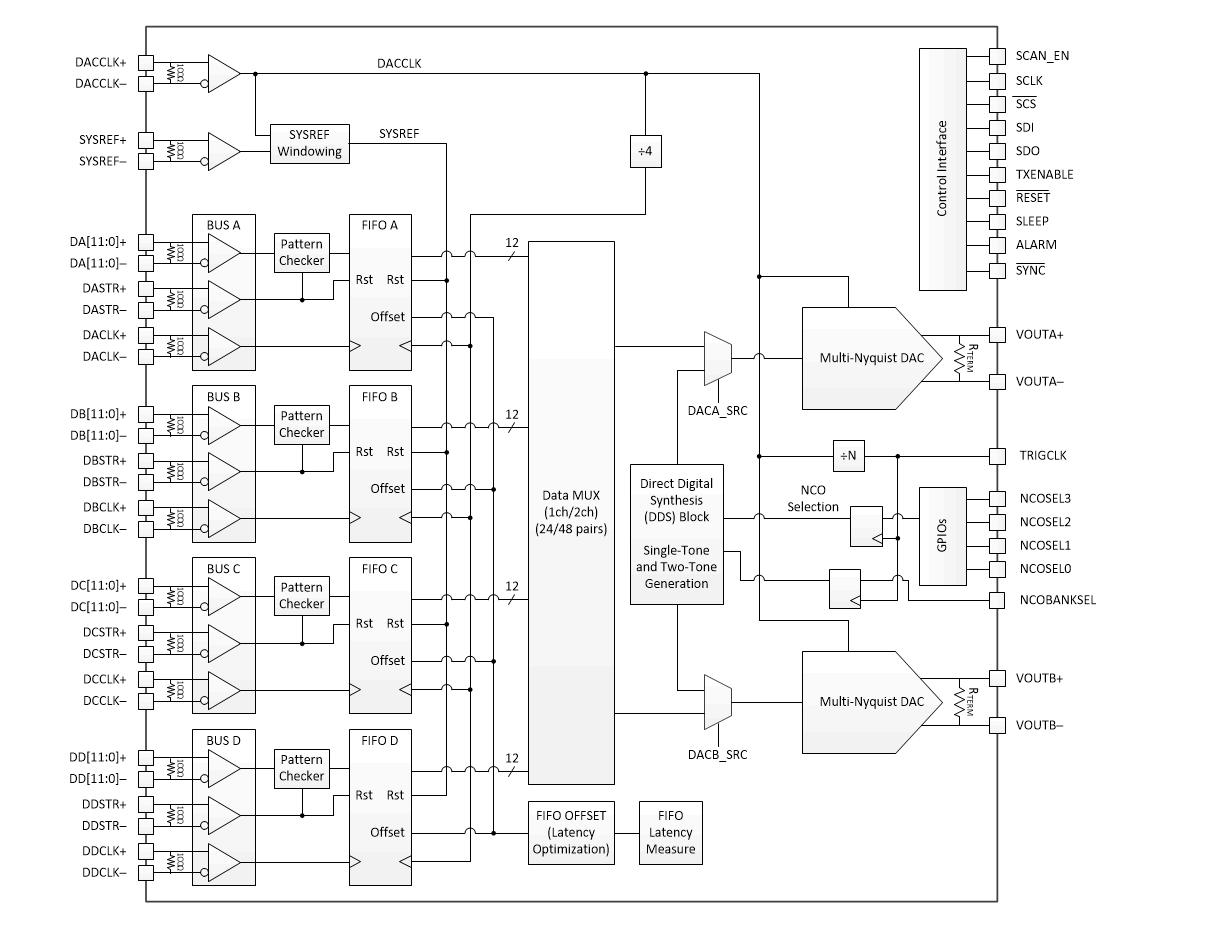

方框图

DAC12DL3200 是德州仪器推出的超高 - speed、低延迟 12 位数模转换器,核心优势为多通道灵活配置、宽输出频率范围与集成 DDS 功能,适配电子战、雷达、卫星通信、任意波形发生器等对高速信号转换与低延迟有严苛需求的场景。

核心参数与特性

- 分辨率与采样率:12 位分辨率,单通道模式最高 6.4 GSPS,双通道模式最高 3.2 GSPS,支持多奈奎斯特工作模式。

- 输出性能:输出频率范围超 8 GHz,满量程输出电流 21 mA,SFDR 最高 79 dBc(NRZ 模式),噪声基底低至 - 165 dBc/Hz(70 MHz 偏移)。

- 工作条件:供电电压涵盖 1.0 V、1.8 V、-1.8 V,工作温度 - 40°C 至 + 85°C,采用 256 引脚 FCBGA 封装(17mm×17mm)。

- 延迟与功耗:器件内延迟 6-8 ns,与 ADC12DL3200 搭配总延迟 < 15 ns;双通道 RF 模式 3.2 GSPS 时功耗 1.49 W。

- 抗干扰与接口:LVDS 接口支持 24/48 对差分信号,单路速率达 1.6 Gbps,集成 100Ω 差分终端,支持多器件同步。

关键功能设计

- 多输出模式:支持 NRZ(普通模式)、RTZ(归零模式)、RF(射频模式)、2xRF(双倍射频模式),适配不同奈奎斯特区间信号输出。

- 集成 DDS 功能:内置 32 个 32 位数控振荡器(NCO),支持单音 / 双音正弦波生成,频率捷变速度 < 500 ns,支持相位连续切换。

- 灵活通道配置:可配置为单通道(4 路 LVDS 总线)或双通道(2 路 LVDS 总线 / 通道),支持 I/Q 基带信号生成。

- 同步与校准:支持 SYSREF 窗口同步,简化多器件时序对齐;内置 FIFO 吸收时序偏差,支持 FIFO 延迟校准与告警功能。

- 接口与控制:SPI 接口支持寄存器配置与流式读写,提供丰富告警功能(FIFO 溢出 / 空、时钟异常等),支持自动静音与温度监测。

典型应用场景

- 电子战与雷达:低延迟脉冲信号生成、干扰信号发射,适配快速信号响应需求。

- 通信系统:卫星通信、软件无线电(SDR)的 I/Q 信号转换,支持宽频带信号传输。

- 测试测量:任意波形发生器(AWG)、通信测试仪,提供高保真高速信号输出。

- 其他场景:医疗设备、电网基础设施中的高速信号转换,适配多通道同步采集与生成需求。

设计与使用建议

- 电源与去耦:各电源域(1.0 V、1.8 V、-1.8 V)需单独供电并就近并联去耦电容,模拟地与数字地单点连接,避免噪声耦合。

- 接口配置:LVDS 信号采用 100Ω 差分走线,时钟与数据对长度匹配;SYSREF 信号需 AC 耦合,通过 SYSREF_POS 寄存器优化采样时序。

- 输出配置:根据应用选择输出模式(NRZ 适配低频,RF/2xRF 适配高频),通过 RBIAS 电阻与寄存器调节满量程电流。

- 初始化与校准:上电后需按顺序配置通道模式、输出模式、FIFO 延迟,启用 SYSREF 同步确保多器件时序一致性;定期监测温度与告警寄存器,保障稳定工作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC12DL3200:高速低延迟数模转换器的技术剖析与应用探索2026-01-26 283

-

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册2025-11-01 1472

-

高速数字模拟转换器DAC12DL3200的技术解析与应用2025-09-24 921

-

DAC12DL3200评估模块2024-11-08 394

-

AD9081四通道、16位、12 GSPS RF DAC和四通道、12位、4 GSPS RF ADC数据表2024-07-31 970

-

ADC08DJ3200 6.4GSPS单通道或3.2GSPS双通道8位射频采样模数转换器数据表2024-07-19 564

-

ADC12DJ3200QML-SP 6.4GSPS单通道或3.2GSPS双通道、12位射频采样模数转换器(ADC)数据表2024-07-16 553

-

ADC12DJ5200-SP 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-15 504

-

DAC38RFxx双通道或单通道、单端或差分输出、14位、9GSPS、射频采样DAC数据表2024-07-12 497

-

ADC12DJ3200AAV 射频采样模数转换器 TI品牌 特性与应用2023-06-16 4857

-

ADC12DJ3200AAV 供应商最新到货2018-10-17 1383

-

ADC12DJ3200EVM订货2018-08-03 1252

全部0条评论

快来发表一下你的评论吧 !