ADC12DJ1600 双通道、12位、1.6GSPS ADC技术手册

描述

ADC12xJ1600 是四通道、双通道和单通道、12 位、1.6GSPS 模数转换器 (ADC) 系列。低功耗、高采样率和 12 位分辨率使 ADC12xJ1600 适用于各种多通道通信和测试系统。

6GHz的全功率输入带宽(−3dB)支持L波段和S波段的直接RF采样。

*附件:adc12dj1600.pdf

包括许多时钟功能以放宽系统硬件要求,例如带有集成压控振荡器 (VCO) 的内部锁相环 (PLL) 以生成采样时钟。提供四个时钟输出,用于对FPGA或ASIC的逻辑和SerDes进行时钟处理。为脉冲系统提供时间戳输入和输出。

JESD204C串行接口通过减少印刷电路板 (PCB) 布线量来减小系统尺寸。接口模式支持 2 至 8 通道(双通道和四通道设备)或 1 至 4 通道(用于单通道设备),SerDes 波特率高达 17.16Gbps,可为每个应用提供最佳配置。

特性

- ADC内核:

- 分辨率:12位

- 最大采样率:1.6GSPS

- 非交错架构

- 内部抖动可减少高阶谐波

- 性能规格 (–1dBFS):

- 信噪比 (100MHz):57.4dBFS

- ENOB (100MHz):9.1 位

- SFDR (100MHz):64dBc

- 本底噪声 (–20dBFS):–147dBFS

- 满量程输入电压:80mVPP-DIFF

- 全功率输入带宽:6GHz

- JESD204C 串行数据接口:

- 支持 2 至 8 个(四通道、双通道)或 1 至 4 个(单通道)总 SerDes 通道

- 最特率:17.16Gbps

- 64B/66B 和 8B/10B 编码模式

- 子类 1 对确定性延迟的支持

- 与JESD204B接收器兼容

- 可选的内部采样时钟生成

- 内部 PLL 和 VCO(7.2 至 8.2GHz)

- SYSREF 窗口简化同步

- 四个时钟输出简化了系统时钟

- FPGA或相邻ADC的参考时钟

- SerDes 收发器的参考时钟

- 脉冲系统的时间戳输入和输出

- 功耗(1GSPS):

- 四通道:477mW/通道

- 双通道:700mW/通道

- 单通道:1000mW

- 电源:1.1V、1.9V

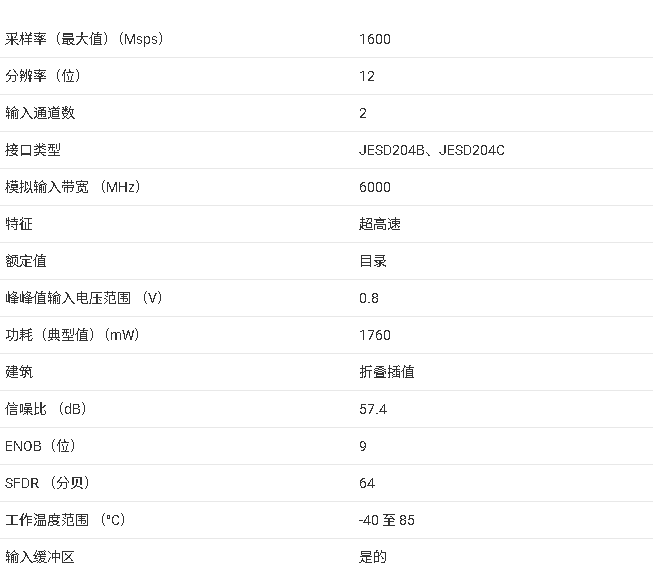

参数

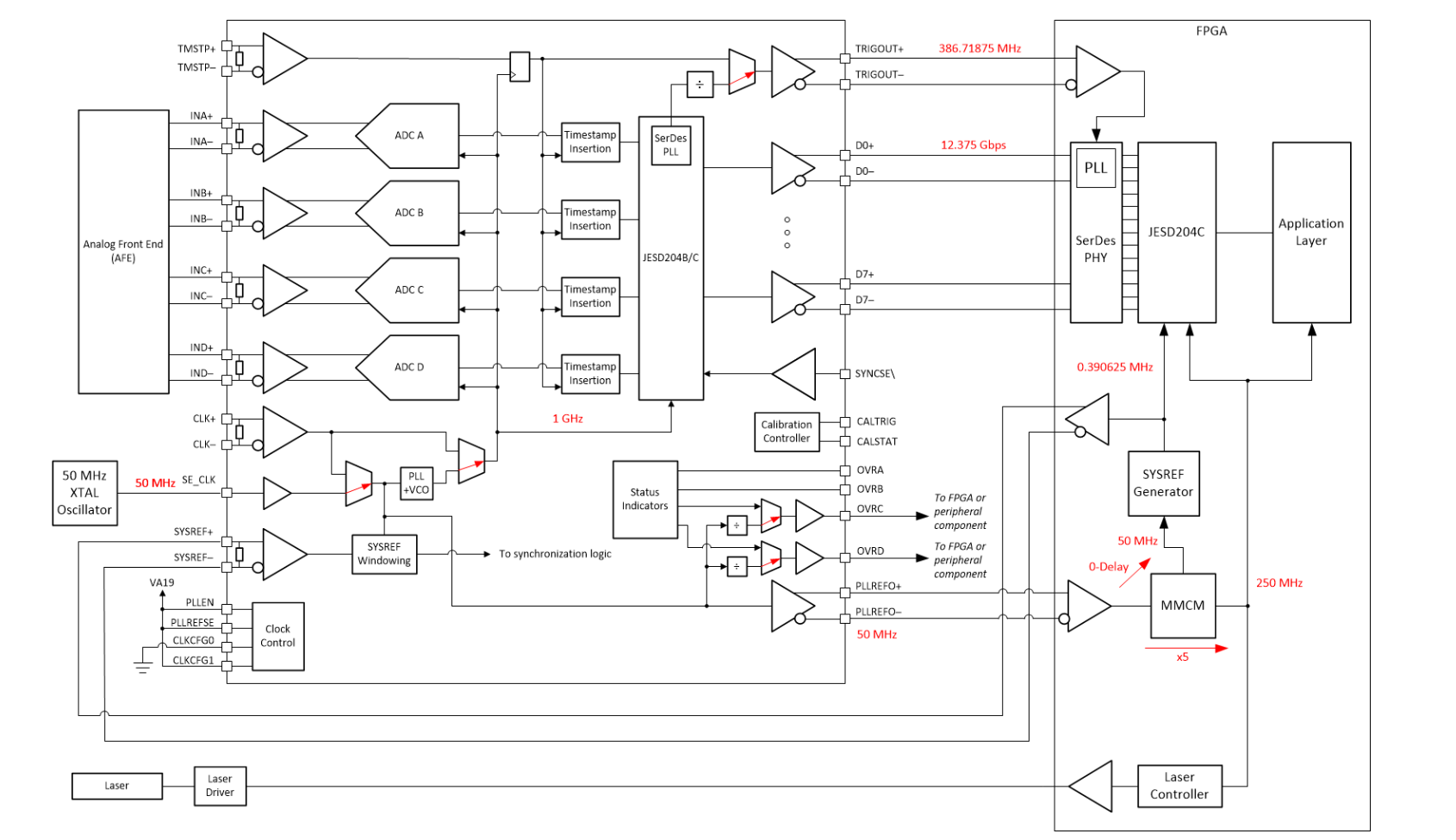

方框图

ADC12xJ1600 系列是德州仪器推出的高速多通道 12 位模数转换器家族,包含四通道(ADC12QJ1600)、双通道(ADC12DJ1600)和单通道(ADC12SJ1600)版本,核心优势为高采样率、宽输入带宽与灵活的 JESD204C 接口,兼具低功耗与高可靠性,适配激光雷达(LiDAR)、测试测量、电子战、卫星通信等高速信号采集场景。

核心参数与特性

- 精度与分辨率:12 位分辨率,无失码,INL 最大 1.9 LSB,偏移漂移低至 0.25 µV/°C,增益漂移 0.000018 %/°C,100MHz 输入时 SNR 达 57.4 dBFS,SFDR 达 64 dBc。

- 采样率与带宽:最高 1.6 GSPS 采样率,全功率输入带宽 6 GHz,支持直接射频采样 L 波段(1-2GHz)和 S 波段(2-4GHz)信号。

- 工作条件:供电电压 1.1V(模拟 / 数字)、1.9V(模拟 / PLL),工作温度 - 40°C 至 + 125°C,采用 144 引脚 FCBGA 封装(10mm×10mm)。

- 功耗表现:1GSPS 时,四通道 477mW / 通道,双通道 700mW / 通道,单通道 1000mW;掉电模式功耗仅 0.15W。

- 抗干扰与接口:CMRR 最高 130dB,支持 JESD204C 接口,SerDes 速率达 17.16Gbps,兼容 8B/10B 与 64B/66B 编码,支持子类 1 确定性延迟。

关键功能设计

- 信号链架构:非交错架构,内置低漂移带隙基准源与 PLL/VCO(7.2-8.2GHz),支持内部振荡器或外部时钟输入,集成输入缓冲器与 50Ω 内部终端电阻。

- 校准与同步:支持前景校准(需离线)、背景校准(无中断)及低功耗背景校准模式,SYSREF 窗口同步功能简化多器件时序对齐,timestamp 输入可标记特定采样点。

- 灵活接口配置:JESD204C 接口支持 1-8 路 SerDes lane,提供 CRC-12 校验与 FEC 前向纠错功能,支持冗余 lanes 配置提升系统可靠性。

- 时钟与触发:内置 C-PLL 生成采样时钟,提供 PLLREFO±、TRIGOUT± 等时钟输出,支持多器件时钟同步,Over-range 检测功能快速响应信号饱和。

典型应用场景

- 激光雷达(LiDAR):脉冲信号采集、FMCW 信号处理,适配车载与工业测距需求。

- 测试测量:手持测试设备、多通道示波器、数字化仪,满足高速信号捕获需求。

- 通信与电子战:卫星通信(SATCOM)、电子情报(ELINT)、信号情报(SIGINT),支持宽频带信号采样。

- 医疗与工业:光学相干断层扫描(OCT)、工厂自动化状态监测、电机控制闭环系统。

设计与使用建议

- 电源与去耦:各电源域(1.1V、1.9V)需单独供电,就近并联去耦电容,模拟地、数字地、PLL 地单点连接至公共地平面。

- 输入与时钟:前端串联 RC 抗混叠滤波器,时钟信号建议 AC 耦合,启用 SYSREF 窗口同步优化时序,避免时钟过冲与毛刺。

- 接口配置:根据需求选择 JMODE 参数定义 JESD204C 编码与 lane 数量,64B/66B 编码提升传输效率,8B/10B 编码兼容 JESD204B 接收器。

- 校准与初始化:上电后优先执行前景校准,温度变化较大时重新校准;启用背景校准需配置 ADC_SRC_DLY 与 MUX_SEL_DLY 以减少切换毛刺,通过 SPI 接口配置寄存器时需先禁用 JESD204C 与校准功能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC12DJ1600-Q1 汽车、2通道、12位、1.6GSPS ADC技术手册2025-11-03 885

-

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册2025-11-01 1584

-

ADC12DJ4000RF RF采样12位ADC技术手册2025-10-31 922

-

ADC12QJ1600-SP 四通道高速模数转换器技术总结2025-10-28 1040

-

ADC12DJ5200SE 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-22 709

-

ADC12DJ3200 6.4GSPS单通道或3.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-19 645

-

ADC12DJ5200-SP 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-15 536

-

ADC12QJ1600-EP具有JESD204C接口的四通道1.6GSPS 12位模数转换器(ADC)数据表2024-07-12 436

-

ADC12DJ3200AAV 射频采样模数转换器 TI品牌 特性与应用2023-06-16 4877

全部0条评论

快来发表一下你的评论吧 !