AFE7950多通道收发器技术手册

描述

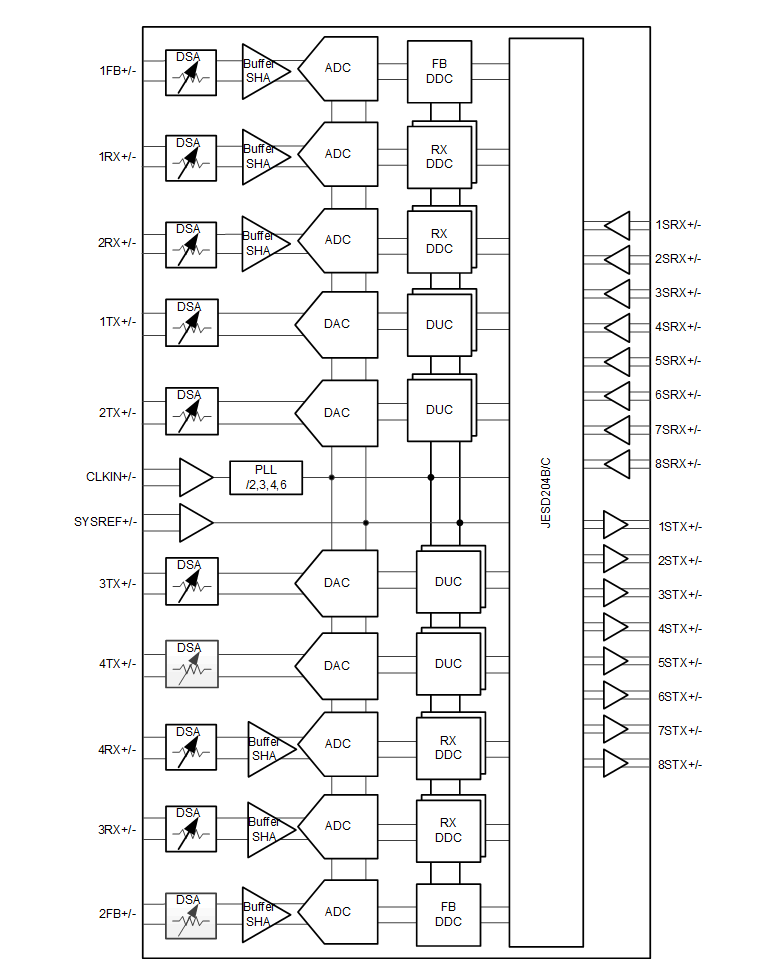

AFE7950是一款高性能、宽带宽的多通道收发器,集成了四个射频采样发射器链、四个射频采样接收器链和两个射频采样反馈链(总共六个射频采样ADC)。该器件的工作频率高达 12 GHz,可在 L、S、C 和 X 波段频率范围内实现直接射频采样,而无需额外的变频级。这种密度和灵活性的提高使高通道数的多任务系统成为可能。

TX 信号路径支持插值和数字上变频选项,可为 4 个 TX 提供高达 1200MHz 的信号带宽,为 2 个 TX 提供高达 2400MHz 的信号带宽。DUC 的输出驱动 12GSPS DAC(数模转换器),具有混合模式输出选项,以增强二次奈奎斯特作。DAC输出包括一个可变增益放大器(TX DSA),具有40 dB范围和1 dB模拟步长和0.125 dB数字步长。

*附件:afe7950.pdf

每个接收器链包括一个 25dB 范围的 DSA(数字步进衰减器),然后是一个 3GSPS ADC(模数转换器)。每个接收器通道都有一个模拟峰值功率检测器和各种数字功率检测器,以辅助外部或内部自主自动增益控制器,以及用于器件可靠性保护的射频过载检测器。灵活的抽取选项可优化数据带宽,适用于四个不带 FB 路径的 RX 高达 1200MHz,对于两个 FB 路径(每个 1200MHz 带宽)的数据带宽,可优化高达 600MHz。

特性

- 四通道射频采样12GSPS发射DAC

- 四通道射频采样3GSPS接收ADC

- 双射频采样 3GSPS 反馈(辅助 RX)ADC

- 最大射频信号带宽:

- 4TX 或 2FB:1200MHz 或 2TX:2400MHz

- 接收:1200MHz(无 FB)、600MHz(带 FB)

- 射频频率范围:

- 发射:600MHz - 12GHz

- 接收/FB:600MHz -12GHz

- 数字步进衰减器 (DSA):

- TX:40dB范围,0.125dB步长

- RX 或 FB:25dB 范围,0.5dB 步长

- 用于 TX 和 RX 的单频或双频 DUC 或 DDC

- 每个 TX 或 RX 和 FB 16 个 NCO

- 可选内部PLL或VCO,用于DAC或ADC时钟,或DAC或ADC采样率的外部时钟

- SerDes 数据接口:

- JESD204B和JESD204C兼容

- 8 个高达 29.5Gbps 的 SerDes 收发器

- 子类 1 多设备同步

- 封装:17mm × 17mm FCBGA,0.8mm 间距

参数

方框图

AFE7950 是德州仪器推出的高性能多通道射频采样收发器,核心优势为高集成度、宽频率范围与灵活配置,兼具优异的信号转换性能与抗干扰能力,适配雷达、战术通信、无线通信测试等对高频宽、多通道同步采样有严苛需求的场景。

核心参数与特性

- 通道与采样率:集成 4 路发射通道(12GSPS DAC)、4 路接收通道与 2 路反馈通道(均为 3GSPS ADC),总计 6 路射频采样 ADC。

- 频率与带宽:射频工作频率 600MHz-12GHz,支持 L、S、C、X 波段直接采样;4 发射 / 2 反馈通道时带宽 1200MHz,2 发射通道时带宽 2400MHz,接收通道带宽最高 1200MHz(无反馈时)。

- 衰减器性能:发射通道 DSA 衰减范围 40dB、步长 0.125dB;接收 / 反馈通道 DSA 衰减范围 25dB、步长 0.5dB,校准后相位精度优异。

- 工作条件:供电电压涵盖 0.9V、1.2V、1.8V 等多档位,工作温度 - 40°C 至 + 110°C(结温),采用 17mm×17mm FCBGA 封装。

- 接口与同步:支持 JESD204B/C 接口,8 路 SerDes 收发器速率最高 29.5Gbps,支持子类 1 多器件同步与 SYSREF 窗口同步。

关键功能设计

- 信号链架构:发射通道集成数字上变频器(DUC)与可变增益放大器,接收通道含峰值功率检测器与数字功率检测器,支持自主自动增益控制。

- 时钟与校准:内置 PLL/VCO(7.2-12.08GHz),支持内部或外部时钟输入;各通道支持偏移与增益校准,DSA 校准后可优化增益与相位误差。

- 灵活工作模式:支持 FDD/TDD 双工模式,多档插值 / 抽取系数配置,适配不同带宽需求;具备睡眠模式,功耗低至 956.8mW。

- 可靠性设计:集成 RF 过载检测器、CRC 校验功能,通道间隔离度高,抗干扰能力强,保障信号完整性与设备稳定性。

典型应用场景

- 国防与航天:雷达系统、导引头前端、电子战设备、战术通信基础设施,满足高频宽、低延迟信号收发需求。

- 通信测试:无线通信测试仪,适配 LTE、NR 等标准的多载波信号生成与采集。

- 其他场景:卫星通信、储能系统高频监测、工业自动化中的高精度射频信号转换。

设计与使用建议

- 电源与去耦:各电源域单独供电,就近并联去耦电容,模拟地、数字地、PLL 地单点连接,降低噪声耦合。

- 射频与时钟:射频输入 / 输出需匹配 50Ω 阻抗,前端串联 RC 抗混叠滤波器;时钟信号建议 AC 耦合,启用 SYSREF 同步优化时序。

- 接口配置:根据需求选择 JESD204 编码方式(8B/10B 或 64B/66B)与 SerDes lane 数量,确保高速数据传输稳定性。

- 初始化与校准:上电后配置通道模式、插值 / 抽取系数及 DSA 衰减值,执行校准流程优化增益与相位一致性;定期监测温度与告警寄存器,保障长期稳定工作。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AFE7950-x:高性能多通道收发器的卓越之选2026-01-26 461

-

AFE7958:高性能多通道收发器的卓越之选2026-01-25 1101

-

AFE8004射频采样收发器技术文档总结2025-10-29 699

-

AFE8092八通道RF收发器技术解析与应用指南2025-09-12 1161

-

德州仪器AFE80xx系列RF采样收发器技术解析与应用设计指南2025-09-08 1683

-

TRF1208-AFE7950射频采样收发器评估模块技术解析2025-08-27 1009

-

适用于K频带的 AFE7950 超外差解决方案应用说明2024-09-12 542

-

AFE8092IABJ 宽带宽多通道收发器的中文资料2021-12-16 2149

全部0条评论

快来发表一下你的评论吧 !