AFE58JD32LP 32通道超声AFE技术手册

描述

该AFE58JD32LP是一种高度集成的模拟前端 (AFE) 解决方案,专为需要高性能、低功耗和小尺寸的便携式超声系统而设计。

该器件通过具有两个芯片的多芯片模块 (MCM) 实现:1 个 VCA 芯片和 1 个 ADC 芯片。VCA芯片有32个通道,与ADC芯片的16个通道连接。每个ADC通道交替转换奇数和偶数VCA通道。

*附件:afe58jd32lp.pdf

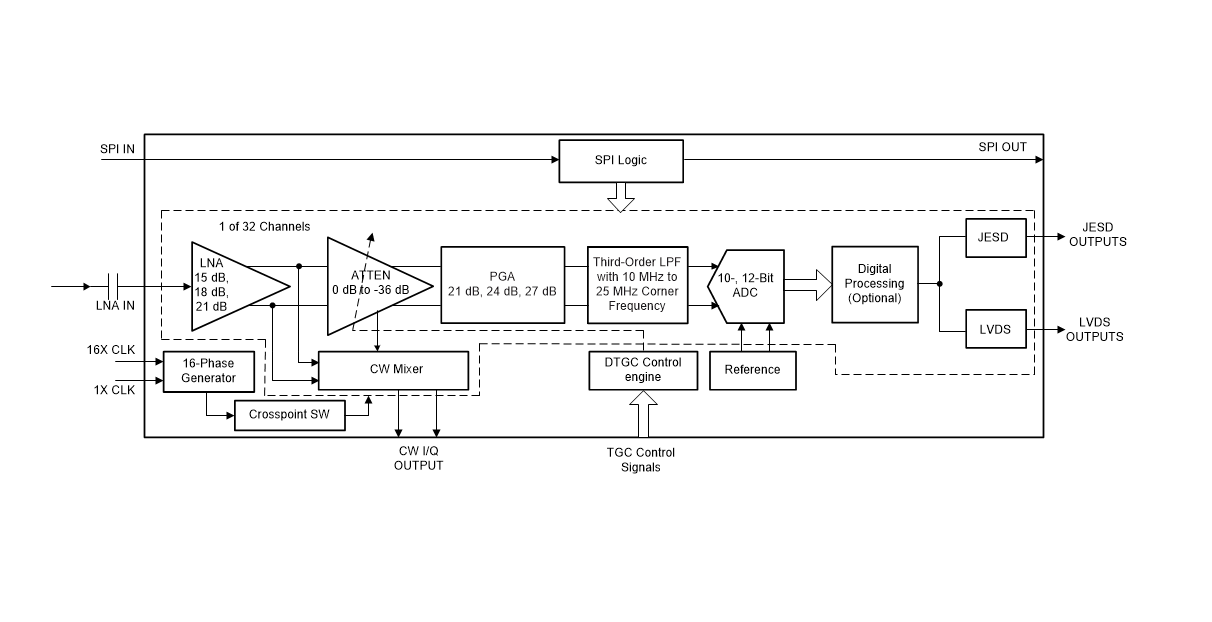

VCA芯片中的每个通道都可以配置为两种模式之一:时间增益补偿(TGC)模式或连续波(CW)模式。在TGC模式下,每个通道包括一个低噪声放大器(LNA)、一个可编程衰减器(ATTEN)、一个可编程增益放大器和一个三阶低通滤波器(LPF)。LNA增益可编程为21 dB、18 dB或15 dB。ATTEN支持0 dB至36 dB的衰减范围,衰减具有数字控制。PGA 提供 21 dB 至 27 dB 的增益选项,步长为 3 dB。LPF 截止频率可以设置为 10 MHz 和 25 MHz 之间,以支持不同频率的超声应用。在CW模式下,LNA的输出进入具有16个可选相位延迟的低功耗无源混频器。可以对每个模拟输入信号施加不同的相位延迟,以执行片内波束成形作。CW 混频器中的谐波滤波器抑制三次和五次谐波,以提高 CW 多普勒测量的灵敏度。

ADC芯片的16个通道可以配置为以12位或10位的分辨率运行。ADC分辨率可以与转换速率进行权衡,在12位和10位分辨率下,最高可分别以80 MSPS和100 MSPS的速度运行。由于每个ADC交替转换两个VCA通道,因此AFE的32个通道中每个通道在12位和10位模式下的最大采样率分别为40 MSPS和50 MSPS。ADC设计用于随采样率缩放其功率。ADC的输出接口通过低压差分信号(LVDS)输出,可以轻松与低成本的现场可编程门阵列(FPGA)连接。

极低功耗的 AFE 解决方案使其适用于具有严格电池寿命要求的系统。

AFE 采用 15 mm × 15 mm 289 引脚 NFBGA 封装,并与 AFE5832 系列引脚兼容。

特性

- 用于超声应用的 32 通道 AFE:

- LNA、衰减器、LPF、ADC、CW 混频器和数字 I/Q 解调器

- 数字时间增益补偿 (DTGC)

- 总增益范围:0 dB至48 dB

- 具有可编程增益的低噪声放大器 (LNA):

- 1pA/rtHz 的低电流噪声

- 增益:21 dB、18 dB 和 15 dB

- 线性输入范围:高达 700 mV

聚丙烯

- 可编程衰减器 (ATTEN):

- 衰减范围(0.125 dB 步长):

0 至 36 dB - 数字TGC引擎

- 衰减范围(0.125 dB 步长):

- 可编程增益放大器 (PGA):

- 增益:21 dB、24 dB 和 27 dB

- 三阶、线性相位、低通滤波器 (LPF):

- 截止频率范围为 10 MHz 至 25 MHz

- 16 个 ADC,以 12 位、80 MSPS 或 10 位、100 MSPS 进行转换:

- 每个ADC以半速率转换两组输入

- 12位模式:72dBFS SNR

- 10位模式:61dBFS SNR

- TGC 模式电源,不带数字 I/Q 解调器:

- 低功耗模式下最低功耗为 18.5 mW/Ch,4 nV/rtHz,10 位,20 MSPS,LVDS(2 倍速率)

- 27.8 mW/Ch,3 nV/rtHz,低噪声模式,12位,40 MSPS

- 24.4 mW/Ch,4 nV/rtHz,低功耗模式,12位,40 MSPS

- 出色的器件间增益匹配:

- ±0.5 dB(典型值)

- 谐波失真:–55 dBc 电平

- 快速一致的过载恢复

- 连续波 (CW) 路径具有:

- 在5 MHz载波的1 kHz频率偏移下,接近相位噪声低至–148 dBc/Hz

- 无信号功耗:10 mW/通道

- 相位分辨率:λ/16

- 12 dB三次和五次谐波抑制

- 数字 I/Q 解调器:

- 抽取滤波器 M = 1 至 63

- 抽取后数据吞吐量降低

- 片上 RAM,具有 32 个预设配置文件

- LVDS接口,速度高达1 Gbps

- 小封装:15 mm × 15 mm NFBGA-289

参数

方框图

AFE58JD32LP 是德州仪器专为超声应用设计的 32 通道模拟前端(AFE),核心优势为低功耗、低噪声、高集成度及灵活接口,适配便携式医疗超声成像、无损检测等对功耗和尺寸敏感的场景。

核心参数与特性

- 通道与信号链配置:集成 32 个完整信号链,每个通道包含低噪声放大器(LNA)、可编程衰减器、可编程增益放大器(PGA)、低通滤波器(LPF)、ADC 及数字 I/Q 解调器,支持时间增益补偿(TGC)和连续波(CW)两种工作模式。

- 增益与噪声性能:总增益范围 0 dB-48 dB,LNA 增益可选 15 dB/18 dB/21 dB,PGA 增益可选 21 dB/24 dB/27 dB;LNA 电流噪声低至 1 pA/√Hz,低功耗模式下噪声 4 nV/√Hz,低噪声模式下 3 nV/√Hz,信号完整性优异。

- ADC 性能:16 个 ADC 芯片分时处理 32 通道信号,12 位模式下最高采样率 40 MSPS(单通道)、总采样率 80 MSPS,SNR 72 dBFS;10 位模式下最高采样率 50 MSPS(单通道)、总采样率 100 MSPS,SNR 61 dBFS。

- 功耗与封装:低功耗模式下每通道功耗仅 18.5 mW(10 位、20 MSPS、LVDS 接口),兼顾性能与续航;采用 15mm×15mm 289 引脚 NFBGA 封装,尺寸紧凑,与 AFE5832 系列引脚兼容。

- 附加特性:CW 模式支持 16 档相位延迟调节,三阶 / 五阶谐波抑制达 12 dB;片内集成 32 组预设配置的 RAM,数字解调支持 1-63 倍抽取滤波,数据吞吐量可灵活调整。

核心功能模块

- 信号调理链路:LNA 提供低噪声放大,可编程衰减器支持 0 dB-36 dB 精细调节(0.125 dB 步进),PGA 进一步提升信号幅度;三阶线性相位 LPF 截止频率可在 10 MHz-25 MHz 配置,适配不同频率超声信号。

- 采样与解调模块:ADC 支持分辨率、采样率灵活权衡,输出接口兼容 LVDS(最高 1 Gbps)和 JESD204B,可直接对接 FPGA 等控制器;数字 I/Q 解调器支持相干解调,简化后端信号处理流程。

- CW 专用路径:内置低功耗无源混频器,近载频相位噪声低至 -148 dBc/Hz(5 MHz 载波、1 kHz 偏移),相位分辨率达 λ/16,支持片上波束成形,适配 CW 多普勒测量场景。

- 系统辅助功能:具备快速过载恢复能力,通道间增益匹配误差典型值 ±0.5 dB,谐波失真低至 -55 dBc,保障多通道一致性;集成数字 TGC 引擎,适配超声成像深度补偿需求。

应用场景

适用于医疗超声成像设备、无损检测设备、声纳成像设备及探头内置电子系统,尤其适合对功耗、尺寸和噪声性能有严格要求的便携式产品。

设计要点

- 接口配置:LVDS 接口需匹配 1 Gbps 速率的阻抗和时序要求,JESD204B 接口需遵循协议规范,确保高速数据传输稳定;通过 SPI 接口配置设备参数,需提前规划寄存器配置流程。

- 电源与时钟:需提供低噪声供电,减少电源噪声对低噪声放大器的干扰;时钟源需保证低抖动,避免影响 ADC 采样精度。

- 布局规范:NFBGA 封装引脚密度高,需严格区分模拟、数字信号布线,避免串扰;超声信号输入端口需做好阻抗匹配,电源引脚就近放置去耦电容。

- 模式选择:根据应用场景切换 TGC 模式(成像)或 CW 模式(多普勒测量),通过配置 LPF 截止频率、ADC 分辨率和采样率,平衡性能与功耗。

-

AFE58JD16 16 通道超声模拟前端技术文档总结2025-11-11 1510

-

AFE58JD28 技术文档核心内容总结2025-11-07 786

-

AFE5832 32 通道超声 AFE技术手册2025-11-06 1050

-

AFE58JD48 12.8 GB JESD204B超声 AFE技术手册2025-11-04 712

-

AFE5832LP 32通道超声波AFE数据表2024-07-31 594

-

AFE58JD32 32通道超声波AFE数据表2024-07-29 472

-

AD9670: 集成数字解调器的8通道超声AFE2021-03-22 907

-

AD9674:集成数字解调器的8通道超声AFE2021-03-21 1126

全部0条评论

快来发表一下你的评论吧 !