新思科技VIP全面支持超以太网与UALink协议

描述

主要亮点

为了高效处理海量数据并支持并行计算,人工智能(AI)和高性能计算(HPC)工作任务需依赖高速、高带宽、低延迟通信能力

相关要求包括:

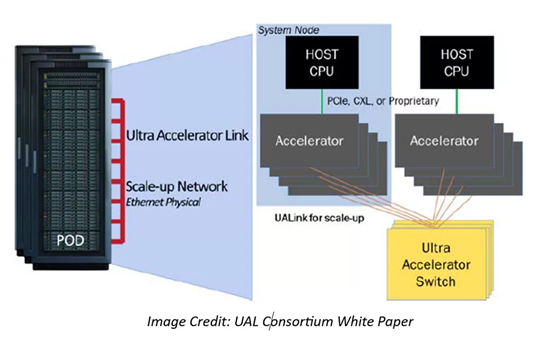

○ 横向扩展(跨服务器)通过超以太网等高性能网络技术实现节点互联

○ 纵向扩展(服务器内)通过UALink等协议连接多个加速器(如GPU)

超以太网和UALink互连确保快速、同步、可扩展的AI模型训练和推理

新思科技为超以太网和UALink提供完整的设计、验证、确认和合规解决方案

引言

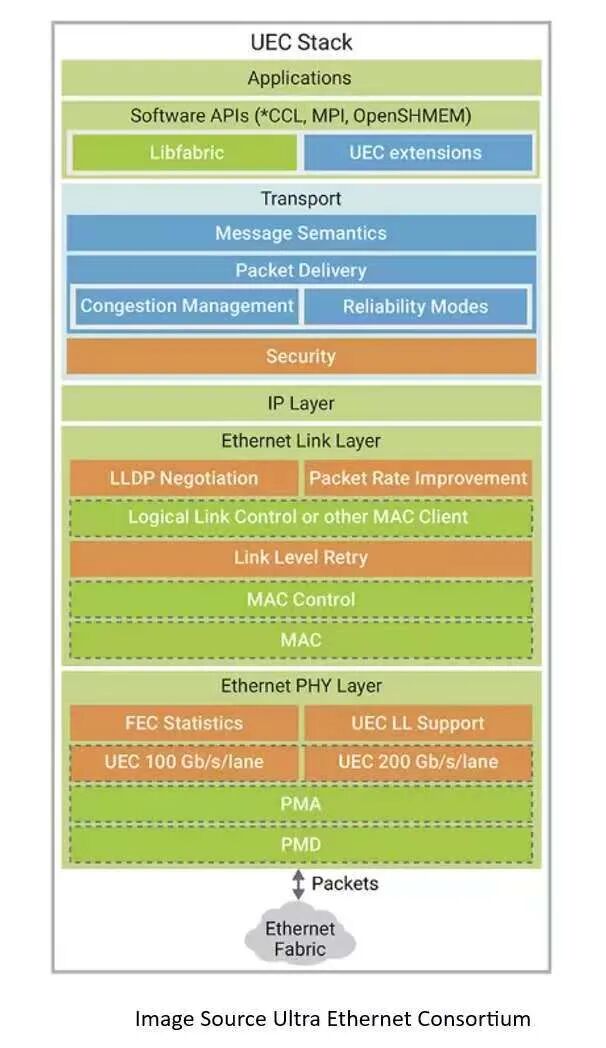

超以太网针对横向扩展架构设计,是一种专为AI量身定制的开放、可互操作、高性能协议解决方案,得到了交换机、网络、半导体和系统供应等领域的知名企业及超大规模用户的支持。

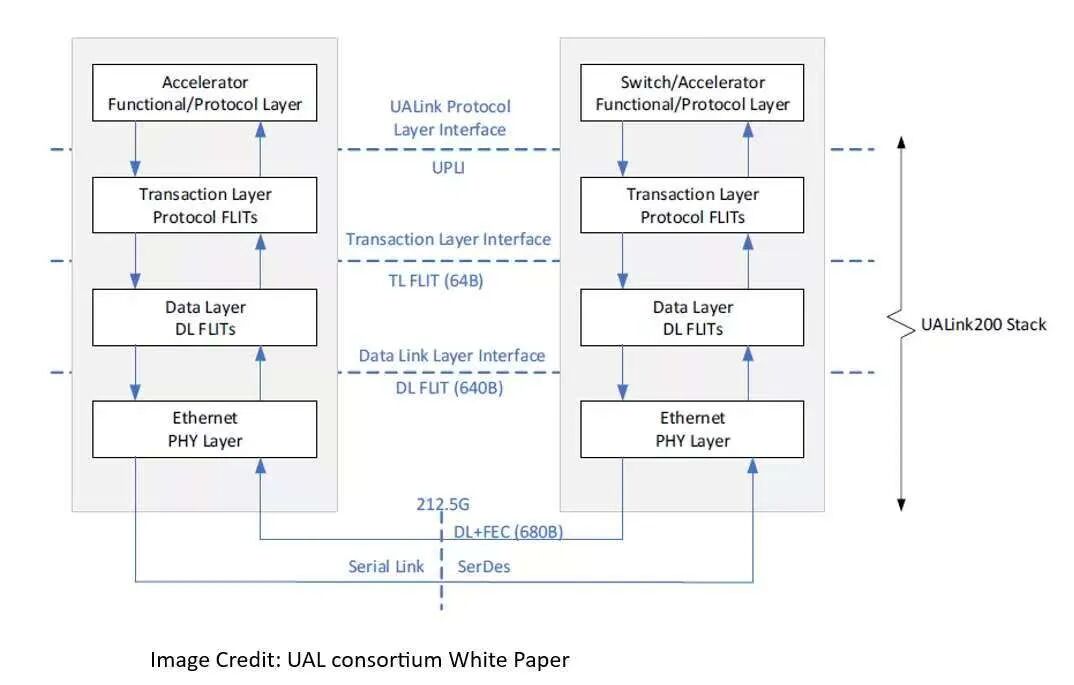

UALink针对纵向扩展架构设计,用于具有大内存共享能力的加速器之间的高速通信,也得到了半导体行业重要厂商的支持。

新思科技去年宣布推出针对UEL和UAL的完整设计与验证解决方案(详见新思科技率先发布超以太网和UALink IP解决方案,实现大规模AI加速器集群高速互联)。

新思科技推出超以太网验证IP(VIP)和超加速器链路(UALink)VIP解决方案,以满足高带宽、低延迟互连的验证需求。这些解决方案提供了扩展当今和未来AI和HPC架构所需的接口。

新思科技UEC VIP特性

超以太网VIP基于LLR(链路层重试)和CBFC(基于信用的流程)规范对设计实现方案进行验证,可用于SoC和系统级设计,以加速AI和HPC应用的验证收敛。

新思科技UEC VIP解决方案支持链路级重试和基于信用的流控等超以太网特性,功能全面;可以灵活地分别启用/禁用 LLR 和 CBFC 协议栈,也可以同时启用/禁用。

生成混合流量*及所有可能的控制有序集。 (混合流量是指符合LLR条件的帧、不符合LLR条件的帧与CBFC流量的组合)

重用现有以太网协议栈,规避了迁移和交互方面的挑战

支持从100G到1.6T的接口速度,适用于“X”MII和PHY接口

在LLR和CBFC功能场景下支持Pause/PFC的功能(按优先级流控)。

通过事务属性实现流量配置文件的不同组合(例如合格、不合格帧、FCS注错等)的广泛灵活性,从而灵活地模拟异常场景、对设计进行压力测试并观察不同刺激配置文件下的设计行为。

新思科技UAL VIP特性

UAL VIP基于UAL_200规范对设计实现方案进行验证,可用于SoC和系统级设计,以加速验证收敛。

新思科技UAL解决方案支持所有5层,即协议层、事务层、数据层、RS层和物理层,并具备如下功能:

灵活地验证各个层。

物理层符合IEEE 802.3 dj标准草案

基于VIP实例/Pod实现多端口的灵活使用

每层支持调试总线,用于观察关键协议指标。

灵活地模拟异常场景,对设计进行压力测试,观察设计在不同激励配置文件下的行为。

多种拓扑结构,适应不同的设计类型。

以上两个VIP均通过以下特性解决了设计验证的复杂性:

原生System/Verilog UVM架构,有助于轻松集成到仿真环境中并加快测试平台开发。

集成验证计划、测试套件和功能覆盖,可加快验证过程并赢取竞争优势。

丰富的可配置选项和内置的协议检查,有助于在已采用协议开发的市场中保持竞争力。

结语

新思科技正在与早期客户和伙伴合作,整合最新规范中提供的新功能,助力增强下一代设计的标准架构。

新思科技VIP原生集成了新思科技Verdi协议分析器调试解决方案及Verdi性能分析器。

要在SoC上运行系统级有效载荷,速度更快且基于硬件的硅前解决方案必不可少。基于新思科技IP的新思科技事务处理器、内存模型、混合和虚拟解决方案可在速度超快的验证硬件、新思科技ZeBu硬件加速解决方案和新思科技HAPS原型系统上实现各种验证和确认用例。运行系统级有效载荷,速度更快且基于硬件的硅前解决方案必不可少。基于新思科技IP的新思科技事务处理器、内存模型、混合和虚拟解决方案可在速度超快的验证硬件、新思科技ZeBu硬件加速解决方案和新思科技HAPS原型系统上实现各种验证和确认用例。

-

新思科技推出超以太网与UALink IP解决方案2024-12-25 1130

-

新思科技推出业界首款连接大规模AI加速器集群的超以太网和UALink IP 解决方案2024-12-20 770

-

以太网协议的种类和特点2024-11-08 4874

-

请问XMC以太网CAN支持RTP协议?2024-01-30 412

-

工业以太网是什么意思_工业以太网和普通以太网区别2023-03-13 6440

-

工业以太网协议的历史及其优势说明2020-10-31 1410

-

以太网的拓扑结构_以太网的通信协议2020-03-20 10207

-

以太网协议的模型有哪些2018-12-26 2870

-

以太网和工业以太网的不同2018-10-23 2671

-

以太网协议及应用方案2017-01-21 753

-

以太网协议2012-08-13 3326

全部0条评论

快来发表一下你的评论吧 !