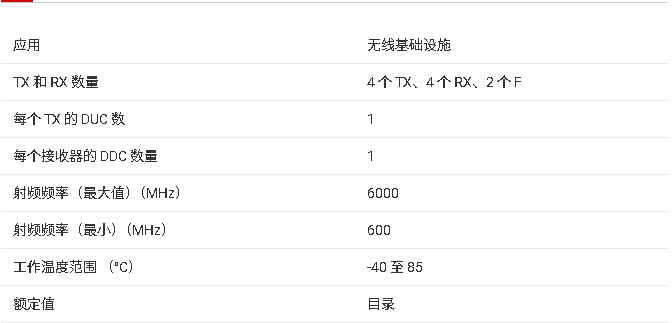

AFE7799 4 个发射、4 个接收、2 个反馈射频收发器技术手册

描述

该AFE7799是一款高性能、多通道收发器,集成了四个直接上变频发射器链、四个直接下变频接收器链和两个宽带射频采样数字化辅助链(反馈路径)。发射器和接收器链的高动态范围允许为无线基站生成和接收 2G、3G、4G 和 5G 信号。低功耗和大通道集成使该AFE7799适用于功率和尺寸受限的 4G 和 5G 大规模 MIMO 基站。宽带和高动态范围反馈路径可以辅助发射器链中功率放大器的数字预失真 (DPD)。快速的 SerDes 速度有助于减少传入和传出数据所需的通道数量。

*附件:afe7799.pdf

该AFE7799的每个接收器链包括一个 28 dB 范围数字步进衰减器 (DSA),然后是一个宽带无源 IQ 解调器,以及一个带有集成可编程抗混叠低通滤波器的基带放大器,驱动连续时间 Σ-Δ ADC。RX 链可以接收高达 200 MHz 的瞬时带宽 (IBW)。每个接收器通道都有两个模拟峰值功率检测器和各种数字功率检测器,以协助接收器通道的外部或内部自主 AGC 控制,以及一个用于器件可靠性保护的射频过载检测器。集成的 QMC(正交失配补偿)算法能够连续监控和校正 rx 链 I 和 Q 不平衡失配,而无需注入任何特定信号或执行离线校准。

每个发射器链包括两个 14 位、3 Gsps IQ DAC,然后是一个可编程重建和 DAC 镜像抑制滤波器,一个 IQ 调制器驱动具有 39 dB 范围增益控制的宽带 RF 放大器。TX 链集成了 QMC 和 LO 泄漏消除算法,利用 FB 路径可以持续跟踪和校正 TX 链 IQ 失配和 LO 泄漏。

FB路径基于RF采样架构,包括一个驱动14位、3Gsps RF ADC的输入RF DSA。直接采样架构提供了固有的宽带接收器链,并简化了TX链损伤的校准。每个FB路径集成了两个独立的NCO,允许在两个观察到的RF输入频段之间快速切换。

特性

- 基于直接上变频架构的四通道发射器:

- 每条链高达 600 MHz 的射频传输带宽

- 基于0-IF下变频架构的四路接收器:

- 每条链高达 200 MHz 的射频接收带宽

- 基于射频采样ADC的反馈链:

- 高达 600 MHz 的射频接收带宽

- 射频频率范围:600 MHz 至 6 GHz

- 用于TX和RX LO的宽带小数N PLL、VCO

- 专用整数 N PLL、VCO,用于数据转换器时钟生成

- JESD204B和JESD204C SerDes 接口支持:

- 8 个高达 29.5 Gbps 的 SerDes 收发器

- 8b/10b 和 64b/66b 编码

- 16 位、12 位、24 位和 32 位格式化

- 子类 1 多设备同步

- 封装:17mm x 17mm BGA,0.8mm 间距

参数

ADS9224R 是德州仪器推出的引脚兼容型双通道同步采样 SAR ADC(含 16 位 ADS9224R、14 位 ADS9234R),核心优势是高分辨率、低延迟及丰富接口选项,专为高精度高速数据采集场景设计。

核心参数与特性

- 分辨率与性能 :ADS9224R 为 16 位分辨率(无失码),INL 最大 ±2 LSB,DNL 最大 ±0.5 LSB;1 MHz 输入时 SNR 达 88 dB、THD 低至 - 109 dB,通道隔离度 - 120 dB。

- 采样与延迟 :最高采样率 3 MSPS,转换延迟仅 333 ns;支持两通道同步采样,模拟输入带宽 52 MHz,适配宽频信号采集。

- 输入与参考 :支持单极性全差分输入,满量程范围 ±4.096 V;集成 2.5 V 精密基准电压源(温漂 15 ppm/°C)及参考缓冲器,含 REFby2 缓冲器用于设置共模电压。

- 接口与功能 :增强型 SPI 接口支持 SDR/DDR 模式、并行字节模式及时钟重定时器功能,适配 MCU/FPGA;支持 2/4 路 SDO 输出,SCLK 频率最高 60 MHz;具备数据平均(2/4 样本)功能,提升噪声环境下性能。

- 供电与功耗 :模拟电源 4.5 V-5.5 V,数字电源 1.65 V-5.5 V;3 MSPS 采样率下模拟功耗典型值 24.3 mA,掉电模式仅 1 µA。

应用场景

适用于光学编码器、声纳接收器、光网络(EDFA 增益控制)、电能质量监测、数字电源、I/Q 解调器、医疗成像(CT/MRI)及阻抗分析仪等场景。

封装与订购信息

- 采用 5mm×5mm 32 引脚 VQFN 封装,带裸露热焊盘。

- 量产型号包括大卷带(3000 片 / 卷)和小卷带(250 片 / 卷)版本,符合 RoHS 标准。

- 引脚镀层为 NIPDAUAG,MSL 等级 2,峰值回流温度 260°C,工作温度 - 40°C 至 125°C。

设计与支持

- 电源去耦需在 AVDD/DVDD 引脚就近放置 1 µF 电容,REFP_x 引脚需接 10 µF 滤波电容;模拟地与数字地独立布局,减少串扰。

- 输入需配置 RC 抗混叠滤波器(推荐 C0G/NP0 电容),未使用引脚需合理端接;支持零周期延迟或宽读周期数据传输模式。

-

AFE7684 2 个发射、4 个接收 RF 采样收发器技术手册2025-11-05 721

-

AFE7989 4 个发射、4 个接收、1 个反馈的射频采样收发器技术手册2025-11-04 1447

-

AFE7921 4 个发射、4 个接收、2 个反馈的射频采样收发器技术手册2025-11-03 708

-

AFE7950多通道收发器技术手册2025-10-31 844

-

AFE77xxD 系列射频收发器技术总结2025-10-28 1070

-

AFE8190 16 通道射频收发器技术文档总结2025-10-24 1089

全部0条评论

快来发表一下你的评论吧 !