3nm芯片设计成本超10亿美元,存在哪些不确定因素?

制造/封装

描述

有些公司已经宣布了3nm工艺的具体计划,但向3nm节点的过渡预计将是一个漫长而坎坷的过程,充满了一系列技术和成本方面的挑战。例如,3nm芯片的设计成本可能会超过10亿美元之巨!此外,3nm也存在一些不确定因素,这些不确定因素可能在一夜之间改变一切。

随着芯片制造商开始在市场上推进10nm/7nm技术,供应商也在为下一代3nm晶体管类型的开发做准备。

有些公司已经宣布了3nm工艺的具体计划,但向3nm节点的过渡预计将是一个漫长而坎坷的过程,充满了一系列技术和成本方面的挑战。例如,3nm芯片的设计成本可能会超过10亿美元之巨!此外,3nm也存在一些不确定因素,这些不确定因素可能在一夜之间改变一切。

然而,这并未让任何厂商缺席。三星和GlobalFoundries分别宣布计划开发一种新的晶体管技术,称为nanosheet FET,即所谓3nm的可变栅宽度技术。例如,三星希望在2019年之前推出PDK(V0.01版),并计划在2021年投入生产。与此同时,台积电正在研发3nm的nanosheet FET及其相关技术——nanowire FET,但台积电尚未公布最终计划。与此同时,英特尔尚未谈到它的计划。

晶体管在芯片中起开关的作用。目前最前沿的晶体管工艺——finFET已经发展到了16nm/14nm和10nm/7nm。2020年前后,预计5nm finFET将会出现,但是除非有新的突破,否则finFET可能会止步于3nm。

图1:FinFET vs 平面

这就是为什么行业正在研发nanosheet FET和nanowire FET,它们被认为是当今finFET的前进之路。在finFET中,对电流的控制是通过在鳍片的三个面上施加栅极来实现的。

nanosheet FET和nanowire FET都被归为环栅技术(gate-all-around)。它们在结构的四个面施加栅极,从而能够更好地控制电流。在nanosheet和nanowire中,finFET被放置在它的一侧,然后被分割成分离的水平片,组成沟道。栅极环绕着沟道。

与nanowire FET相比,nanosheet FET具有更宽的沟道,这意味着器件具有更强的性能和更大的驱动电流。这就是为什么nanosheet在市场上越来越受欢迎。

图2 (a)finFET(b)nanowire(c)nanosheet 的横截面图。

但是迁移到nanosheet FET或nanowire FET并非易事。首先,环栅器件的性能和微缩效益值得商榷。国际商业战略公司(IBS)首席执行官Handel Jones表示:“行业需要大幅增强功能,小幅提高晶体管成本,以此证明使用3nm技术是合理的。问题在于3nm工艺节点的定义,以及理解环栅技术真正的优点所在。”。

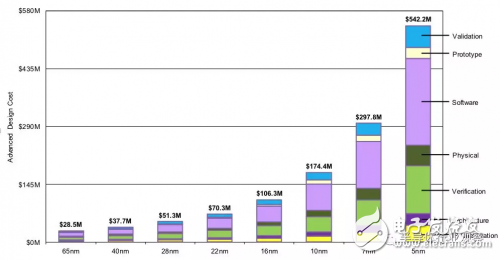

设计成本也是问题之一。据IBS称,一般而言,IC设计成本已从28nm平面器件的5130万美元上涨到7nm的2.97亿美元和5nm的5.422亿美元。但是3nm的IC设计成本从5亿—15亿美元不等。15亿美元这个数字涉及到英伟达的复杂GPU。

图3:IC设计成本攀升

因此,客户在考虑迁移到3nm之前,可能会在某些节点停留更长时间,比如16nm/14nm和7nm。有些客户可能永远不会迁移到3nm。如果环栅技术出现,那么3nm可能会在2021年的目标日期之后推出。

还有一些客户可能转向nanosheet,但这将是一项艰巨的任务。为了帮助行业占得先机,Semiconductor Engineering已全面分析了环栅技术及其制造所面临的挑战。

-

芯片工艺从目前的7nm升级到3nm后,到底有多大提升呢?2021-06-18 0

-

开发成本过高,7nm将是一个长期存在的节点2018-06-25 1529

-

芯片制造进入10nm以内后,该如何面临现实的困难2018-07-11 1169

-

麒麟980研发耗资3亿美元 3nm制程工艺研发资金将达到40-50亿美元2018-08-29 1230

-

台积电3nm工艺试产延期到10月份2020-03-31 1637

-

台积电支出200亿美元打造3nm成熟工艺2021-01-05 2099

-

台积电3nm产能建设资本开支将超过200亿美元2021-01-05 1775

-

浅析台积电3nm工艺存在的两大难关2021-01-11 3371

-

台积电今年砸150亿美元开发3nm工艺:2022下半年量产2021-01-15 2109

-

Intel将部分芯片外包给台积电 看上后者3nm工艺2021-01-27 2154

-

报道称芯片代工商台积电将从2022年开始量产3nm芯片2021-03-08 1966

-

2nm、3nm制程什么意思2022-07-01 31128

-

3nm芯片什么时候出 3nm芯片有多少个晶体管2022-07-07 10754

-

三星即将公布首颗3nm芯片,或将扭转订单数量2022-07-25 1836

-

流片成本达10亿美元!苹果和Arm强强联合的芯片是成功的吗?2023-11-06 1203

全部0条评论

快来发表一下你的评论吧 !