ADC12DL3200 技术规格与应用总结

描述

该ADC12DL3200是一款RF采样、千兆采样、模数转换器(ADC),可直接对从DC到10 GHz以上的输入频率进行采样。在双通道模式下,ADC12DL3200可以采样高达3200 MSPS,在单通道模式下采样高达6400 MSPS。通道数(双通道模式)和奈奎斯特带宽(单通道模式)的可编程权衡允许开发灵活的硬件,以满足高通道数或宽瞬时信号带宽应用的需求。8.0 GHz的全功率输入带宽(–3 dB)和可用的频率范围允许对频率捷变系统进行L波段、S波段、C波段和X波段的直接RF采样。

*附件:adc12dl3200.pdf

该ADC12DL3200使用低延迟、低压差分信号 (LVDS) 接口,适用于延迟敏感应用或首选 LVDS 的简单性。该接口使用多达 48 个数据对、四个双倍数据速率 (DDR) 时钟和四个选通信号,排列在四个 12 位数据总线中。该接口支持高达 1.6 Gbps 的信令速率。选通信号简化了总线之间和多个设备之间的同步。选通在内部生成,可以通过 SYSREF 输入在确定性时间复位。创新的同步功能(例如无噪声孔径延迟 (T AD) 调整和 SYSREF 窗口化)进一步简化了多器件同步。

特性

- ADC内核:

- 12 位分辨率

- 单通道模式下高达 6.4 GSPS

- 双通道模式下高达 3.2 GSPS

- 用于低幅度、高阶谐波的内部抖动

- 低延迟 LVDS 接口:

- 总延迟:< 10 ns

- 多达 48 个数据对,速度为 1.6 Gbps

- 四个DDR数据时钟

- 频闪信号简化同步

- 本底噪声(无输入,V FS = 1.0 V PP-DIFF):

- 双通道模式:–151.1 dBFS/Hz

- 单通道模式:–154.3 dBFS/Hz

- V CMI 为 0 V 的缓冲模拟输入:

- 模拟输入带宽 (–3 dB):8.0 GHz

- 可用输入频率范围:> 10 GHz

- 满量程输入电压(V FS,默认):0.8 V PP

- 无噪声光圈延迟 (T AD) 调整:

- 精确采样控制:19-fs 步长

- 简化同步和交错

- 温度和电压不变延迟

- 易于使用的同步功能:

- 自动 SYSREF 时序校准

- 样品标记的时间戳

- 功耗:3.15 W

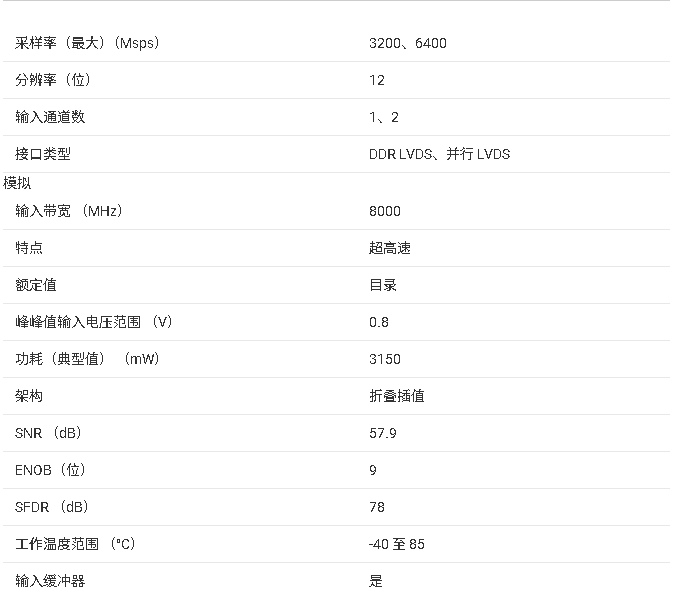

参数

方框图

ADC12DL3200 是德州仪器推出的高速射频采样模数转换器(ADC),核心优势为高采样速率、宽输入带宽与低延迟 LVDS 接口,支持单 / 双通道灵活配置,集成多种校准与同步功能,适用于示波器、电子战、雷达、宽带数字化等高频信号采集场景。

一、核心产品特性与参数

1. 分辨率与采样性能

- 分辨率为 12 位,无丢失码,积分非线性误差(INL)最大 ±2 LSB,微分非线性误差(DNL)最大 ±1 LSB,线性度优异。

- 采样速率:单通道模式最高 6.4 GSPS(双沿采样),双通道模式最高 3.2 GSPS(单沿采样),时钟频率支持 800 MHz~3.2 GHz。

- 噪声性能:单通道模式噪声谱密度低至 - 154.3 dBFS/Hz,双通道模式为 - 151.1 dBFS/Hz,信号保真度高。

2. 输入与射频性能

- 输入带宽:全功率带宽(-3 dB)8 GHz,可用频率范围超 10 GHz,支持 DC 至 X 波段直接射频采样。

- 输入配置:双差分模拟输入(INA±/INB±),内置 50 Ω 单端 termination 电阻,共模电压 0 V,全量程输入电压可在 480 mVpp~1000 mVpp 间调节。

- 抗干扰能力:通道间串扰低,三阶交调失真(IMD3)性能优异,大信号无杂散动态范围(SFDR)最高可达 78 dBFS。

3. 接口与延迟

- 高速 LVDS 接口:支持 48 路数据对、4 路 DDR 时钟与 4 路选通信号,单路速率最高 1.6 Gbps,总延迟小于 10 ns,适配低延迟需求。

- 同步接口:支持 SYSREF 信号同步,内置 TMSTP± 时间戳输入,便于多器件级联与采样标记。

4. 电源与环境

- 电源配置:模拟电源 1.1 V(VA11)、1.9 V(VA19),数字电源 1.1 V(VD11),LVDS 接口电源 1.1 V~1.9 V,典型功耗 3.15 W(单通道模式)。

- 工作温度范围 - 40°C~+85°C,采用 17mm×17mm 256 引脚 FCBGA 封装,焊球材质 SNAGCU 或 SNPB,符合 RoHS 标准,MSL 等级 3(260°C 峰值回流,168 小时存储)。

二、关键功能与优势

1. 灵活工作模式

- 通道配置:通过 DES_EN 引脚切换单 / 双通道,单通道模式可选择 INA± 或 INB± 作为输入,双通道支持输入互换。

- LVDS 输出模式:支持 2/4 路 LVDS 总线配置,可选择交错或对齐输出,采样宽度支持 8/10/11/12 位可调,支持数据加扰功能降低频谱峰值。

- 校准功能:提供前景校准、背景校准与低功耗背景校准(LPBG),支持偏移校准、增益校准与孔径延迟校准,保障宽温范围内性能稳定。

2. 同步与时序控制

- 无噪声孔径延迟调整:支持 19 fs 精细步长与 1.13 ps 粗调步长,可精准对齐多器件采样时序,适配外部交织扩展采样速率。

- SYSREF 同步:支持自动 SYSREF 校准与窗口选择,简化多器件同步流程,确保确定性延迟。

- 时间戳与过范围检测:TMSTP± 引脚可标记特定采样点,内置双阈值过范围检测(OVR_T0/OVR_T1),响应时间快。

3. 辅助功能

- 内置 6 个 ADC 核心,支持核心轮换校准,背景校准模式下无数据中断。

- 集成温度监测二极管、带隙基准源(BG 引脚输出 1.1 V),支持 SPI 串行编程(时钟最高 15.625 MHz),支持流式读写寄存器。

三、典型应用场景

1. 核心应用领域

- 宽带射频采样接收机:直接采样 L/S/C/X 波段信号,适配电子战、卫星通信系统。

- 示波器与宽频数字化仪:支持单通道 5 GSPS / 双通道 2.5 GSPS 可重构配置,满足高带宽信号时域 / 频域分析。

- 雷达与测试仪器:高采样速率与低延迟特性适配雷达目标探测、汽车雷达测试仪等实时信号处理场景。

2. 典型应用配置

- 宽带射频接收机 :通过巴伦变压器将单端射频信号转换为差分信号,搭配 LMK04832 时钟芯片提供低抖动时钟与 SYSREF 同步信号,LVDS 接口直连 FPGA 进行数据处理。

- 可重构示波器 :采用 LMH5401 差分放大器实现单端 - 差分转换,通过 DAC8560 提供 DC 偏移调整,支持 1 GHz 模拟带宽与数字滤波重构。

四、设计与使用建议

1. 电源与布局

- 电源需采用低噪声方案,模拟电源与数字电源单独布线,就近放置去耦电容,建议使用 LDO 或纹波滤波器降低电源噪声。

- 高频信号路径(输入、时钟、LVDS)采用 100 Ω 差分布线,避免 90° 弯折,保证阻抗匹配,减少串扰与反射。

2. 校准与同步

- 上电后建议执行前景校准,环境温度变化较大时启用背景校准,偏移校准需确保输入无 DC 或近 DC 信号。

- 多器件同步时,SYSREF 信号需等长布线,启用自动 SYSREF 校准功能,通过 TAD 寄存器保存校准后的孔径延迟参数。

3. 输入与接口

- 模拟输入建议 AC 耦合(时钟信号强制 AC 耦合),长距离引线需添加屏蔽层,避免电磁干扰。

- LVDS 接口需匹配传输线长度,选通信号可选择专用引脚或 LSB 替换模式,根据接收端需求配置数据加扰功能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC12DL3200:高速低延迟数模转换器的技术剖析与应用探索2026-01-26 290

-

ADC12DJ3200 技术文档核心内容总结2025-11-07 985

-

ADC12DL2500技术文档总结2025-10-27 903

-

求助,关于ADC12DL3200EVM时间交织采样的问题求解2024-11-26 432

-

通过spi对ADC12DL3200进行寄存器配置,当0x200的值为0x01时没有数据,为什么?2024-11-25 191

-

ADC12DL3200EVM评估板lvds接口是标准的FMC接口吗?2024-11-22 420

-

求助,关于ADC12DL3200的UserPattern问题求解答2024-11-13 338

-

DAC12DL3200评估模块2024-11-08 396

-

ADC12DJ3200原理图2024-08-19 436

-

ADC12DL3200 6.4GSPS单通道或3.2GSPS双通道12位模数转换器(ADC)数据表2024-07-15 542

-

ADC12DJ3200EVM2021-12-22 1802

-

ADC12DL3200ALJ详细参数2020-07-13 1849

-

ADC12DJ3200EVM订货2018-08-03 1256

全部0条评论

快来发表一下你的评论吧 !