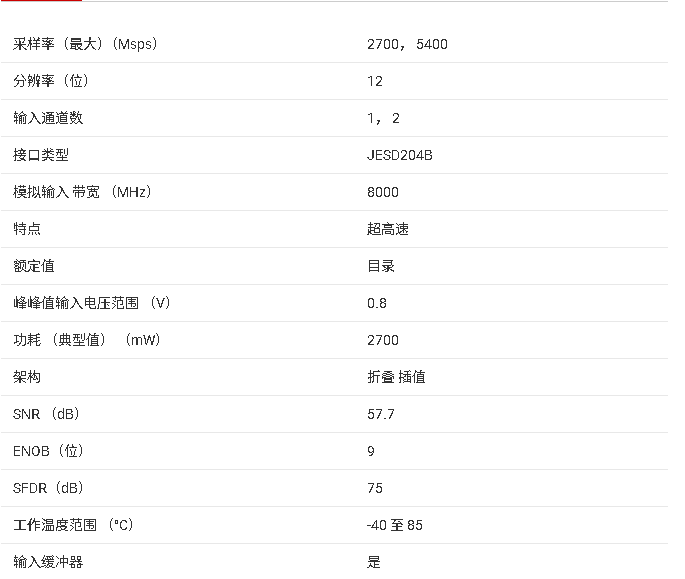

ADC12DJ2700 12位、双通道2.7GSPS或单通道5.4GSPS、RF采样模数转换器技术手册

描述

ADC12DJ2700器件是一款射频采样、千兆采样、模数转换器 (ADC),可直接对从 DC 到 10 GHz 以上的输入频率进行采样。在双通道模式下,ADC12DJ2700可以采样高达 2700 MSPS,在单通道模式下可以采样高达 5400 MSPS。通道数(双通道模式)和奈奎斯特带宽(单通道模式)的可编程权衡允许开发灵活的硬件,以满足高通道数或宽瞬时信号带宽应用的需求。8.0 GHz 的全功率输入带宽 (–3 dB),在双通道和单通道模式下的可用频率都超过 –3 dB 点,允许对 L 波段、S 波段、C 波段和 X 波段进行直接射频采样,适用于频率捷变系统。

*附件:adc12dj2700.pdf

该ADC12DJ2700使用高速JESD204B输出接口,具有多达 16 个串行通道和子类 1 合规性,可实现确定性延迟和多器件同步。串行输出通道支持高达 12.8 Gbps,并可配置为权衡比特率和通道数。创新的同步功能,包括无噪声孔径延迟(T 广告 )调整和SYSREF窗口,简化相控阵雷达和MIMO通信的系统设计。双通道模式下的可选数字下变频器(DDC)可降低接口速率(实抽取模式和复抽取模式)和信号的数字混合(仅限复抽取模式)。

特性

- ADC内核:

- 12 位分辨率

- 单通道模式下高达 5.4 GSPS

- 双通道模式下高达 2.7 GSPS

- 性能规格:

- 本底噪声(无信号,V

司 司长= 1.0 伏PP-差分器):- 双通道模式:–151.6 dBFS/Hz

- 单通道模式:–153.8 dBFS/Hz

- HD2、HD3:–65 dBc,最高 3 GHz

- 本底噪声(无信号,V

- 带 V 的缓冲模拟输入

CMI的0 V 的:- 模拟输入带宽 (–3 dB):8.0 GHz

- 可用输入频率范围:>10 GHz

- 满量程输入电压 (V

司 司长,默认):0.8 V聚丙烯 - 模拟输入共模 (V

ICM的):0 伏

- 无噪声孔径延迟 (T

广告)调整:- 精确采样控制:19-fs 步长

- 简化同步和交错

- 温度和电压不变延迟

- 易于使用的同步功能:

- 自动 SYSREF 定时校准

- 样品标记的时间戳

- JESD204B串行数据接口:

- 支持子类 0 和 1

- 最大通道速率:12.8 Gbps

- 多达 16 个通道可降低通道速率

- 双通道模式下的数字下变频器:

- 实际输出:DDC 旁路或 2 倍抽取

- 复数输出:4 倍、8 倍或 16 倍抽取

- 每个DDC有四个独立的32位NCO

- 功耗:2.7 W

- 电源:1.1 V、1.9 V

参数

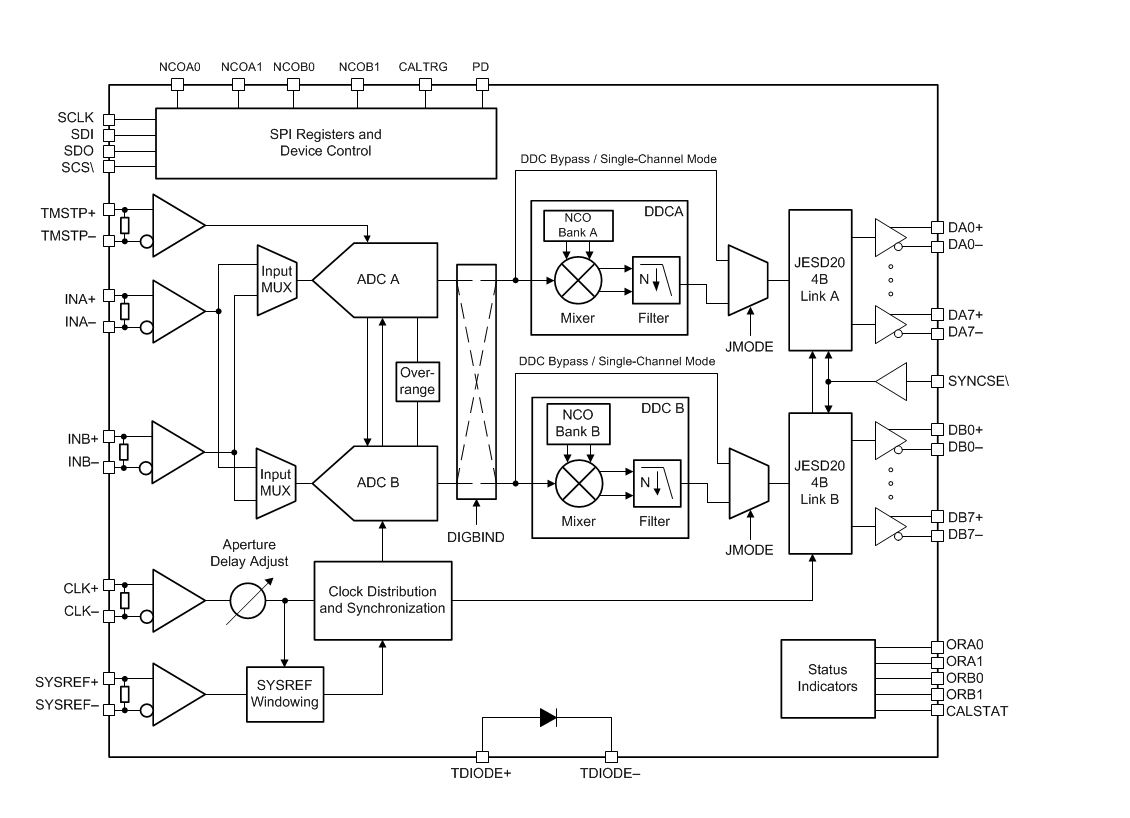

方框图

ADC12DJ2700 是一款 12 位 RF 采样模数转换器(ADC),单通道模式最高 5.4 GSPS 采样率、双通道模式最高 2.7 GSPS 采样率,具备 8GHz 全功率输入带宽与 JESD204B 高速串行接口,适用于宽带射频信号采集场景,兼顾高分辨率与高速采样性能。

核心参数与特性

- 采样与分辨率 :12 位无失码分辨率,单通道 5.4 GSPS、双通道 2.7 GSPS 采样率,支持 8/16 路 JESD204B 串行 lanes。

- 信号性能 :双通道模式噪声基底 -151.6 dBFS/Hz,单通道模式 -153.8 dBFS/Hz;3GHz 以下 HD2、HD3 均达 -65 dBc;8GHz(-3dB)全功率输入带宽,可用频率超 10GHz。

- 供电与功耗 :需 1.1V(VA11/VD11)和 1.9V(VA19)双电源,典型功耗 2.7W,支持低功耗背景校准(LPBG)模式优化功耗。

- 接口与控制 :JESD204B 串行接口(支持子类 0/1),最高 12.8 Gbps 通道速率;SPI 接口用于配置,支持 timestamp 采样标记、自动 SYSREF 时序校准。

- 封装与环境 :144 引脚 FCBGA 封装(10.00mm×10.00mm),工作温度范围 -40°C 至 +85°C,结温最高 150°C。

关键功能说明

- 工作模式 :支持单通道(双沿采样)和双通道模式切换,通过 JMODE 寄存器配置通道数、采样率及数据格式;双通道模式可选数字下变频器(DDC),支持 2x/4x/8x/16x 抽取。

- 校准功能 :提供前景校准(离线)和背景校准(在线),支持偏移、增益及线性度校准;LPBG 模式可平衡性能与功耗,减少校准功耗开销。

- 同步特性 :19 fs 步长无噪声孔径延迟调整,简化多器件同步;SYSREF 窗口 ing 功能优化时序匹配,确保确定性延迟;支持 JESD204B 子类 1 确定性 latency。

- 输入与保护 :模拟输入采用 50Ω 单端终端,支持 AC/DC 耦合,内置过压保护二极管;全量程输入电压可通过寄存器调整(默认 0.8Vpp,范围 0.5Vpp-1.0Vpp)。

- 测试与诊断 :支持 PRBS、斜坡、K28.5 等多种测试模式,内置过范围检测(双阈值)和温度监测二极管,提供报警状态寄存器。

典型应用场景

适用于通信测试仪(802.11ad、5G)、卫星通信(SATCOM)、相控阵雷达、信号情报(SIGINT)与电子情报(ELINT)、合成孔径雷达(SAR)、激光雷达(LIDAR)测距、示波器与宽带数字化仪、微波回传及射频采样软件无线电(SDR)等场景。

应用设计要点

- 电源设计 :推荐 “开关电源 + LDO” 架构,严格遵循电源时序(VA19 先于 1.1V 电源使能),电源端需配置去耦电容,降低噪声耦合。

- 布局要求 :高速信号(CLK/SYSREF/JESD204B)采用 100Ω 差分走线,减少串扰;模拟与数字地分开布局,通过过孔密集连接接地平面;避免直角走线和阻抗突变。

- 时钟与同步 :时钟源需低抖动(推荐 LMX2594/LMK04832),CLK± 建议 AC 耦合;多器件同步需匹配 SYSREF 走线长度,启用自动 SYSREF 校准。

- 寄存器配置 :初始化需按顺序配置 JMODE、校准模式、DDC 参数等,通过 SPI 接口读写配置与转换数据;支持流式读写提高配置效率。

-

ADC12J2700 12位、2.7GSPS、RF采样模数转换器(ADC)技术手册2025-11-12 832

-

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册2025-11-01 1584

-

ADC12DJ1600 双通道、12位、1.6GSPS ADC技术手册2025-10-31 1419

-

ADC12DJ5200SE 射频采样模数转换器(ADC)技术文档总结2025-10-29 1073

-

ADC12DJ5200SE 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-22 709

-

ADC08DJ3200 6.4GSPS单通道或3.2GSPS双通道8位射频采样模数转换器数据表2024-07-19 587

-

ADC12DJ3200QML-SP 6.4GSPS单通道或3.2GSPS双通道、12位射频采样模数转换器(ADC)数据表2024-07-16 590

-

ADC12DJ5200-SP 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-15 536

-

ADC12DJ3200AAV 射频采样模数转换器 TI品牌 特性与应用2023-06-16 4877

全部0条评论

快来发表一下你的评论吧 !