DAC8740H/DAC8741H 产品核心信息总结

描述

DAC8740H和DAC8741H (DAC874xH) 是兼容 HART、FOUNDATION 现场总线™和 PROFIBUS PA 的低功耗调制解调器,专为工业过程控制和工业自动化应用而设计。^®^

在HART模式下,DAC874xH集成了作为半双工HART物理层调制解调器运行所需的所有电路,在从配置或主配置中,具有最少的外部滤波组件。在FOUNDATION现场总线模式下,DAC874xH集成了所有必需的电路,以作为半双工FOUNDATION现场总线兼容H1控制器和MAU运行。

*附件:dac8740h.pdf

HART、FOUNDATION 现场总线或 PROFIBUS PA 数据流可以通过 UART 接口或由 SPI 接口访问的集成 FIFO 从微控制器传输。SPI接口包括一个SDO引脚,用于菊花链支持、各种中断和其他扩展功能。

特性

- 符合 HART 标准的物理层调制解调器

- 1200Hz、2200Hz HART FSK 正弦波

- 寄存TX信号的可编程幅度(仅限DAC8741H)

- 集成 RX 解调器和带通滤波器,外部元件最少

- FOUNDATION 现场总线兼容 H1 控制器和介质连接单元 (MAU)

- 基于曼彻斯特编码总线供电 (MBP) 的 31.25 kbit/s 通信

- 集成曼彻斯特编码器和解码器

- 与 PROFIBUS PA 兼容

- 低静态电流:在典型工业工作温度范围(–40°C 至 +85°C)下最大 180 μA。

- 集成1.5V基准电压源

- 灵活的时钟选项

- 内部振荡器

- 外部晶体振荡器

- 外部CMOS时钟

- 数字接口

- DAC8740H:UART

- DAC8741H:SPI

- 可靠性:CRC误码检查、看门狗定时器(仅限DAC8741H)

- 宽工作温度:–55°C 至 +125°C

- 4mm × 4mm QFN 封装

参数

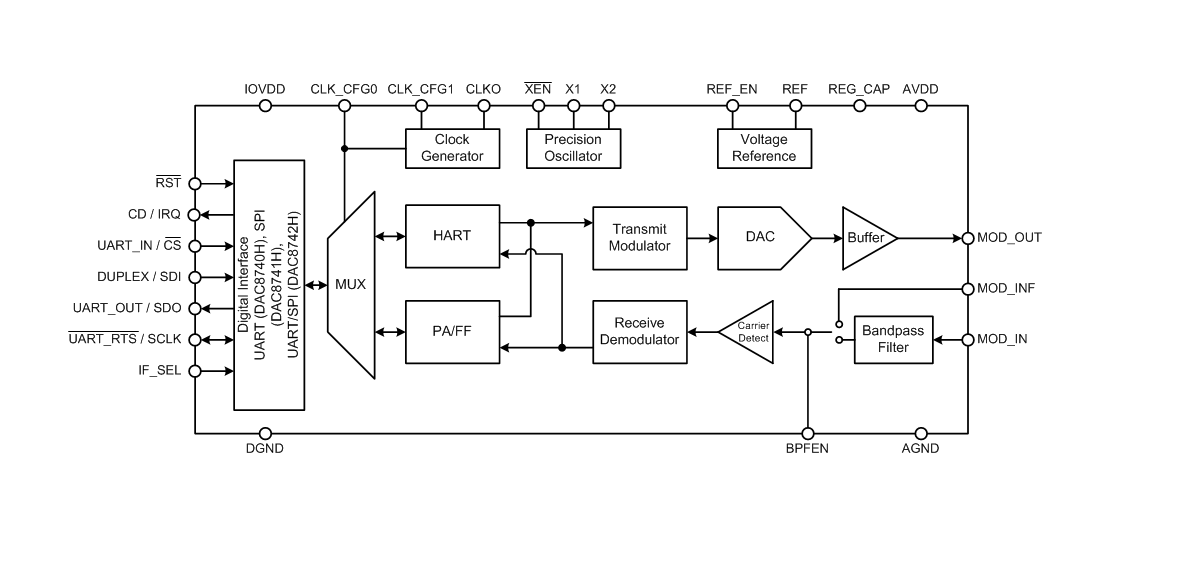

方框图

DAC8740H 和 DAC8741H 是兼容 HART®、FOUNDATION Fieldbus™ 及 PROFIBUS PA 协议的低功耗调制解调器,适用于工业过程控制与自动化场景,核心差异在于数字接口(DAC8740H 为 UART,DAC8741H 为 SPI),集成丰富功能以减少外部元件需求。

核心参数与特性

- 通信协议支持 :HART 模式支持 1200Hz/2200Hz FSK 正弦波信号,FOUNDATION Fieldbus/ PROFIBUS PA 模式支持 31.25 kbit/s 曼彻斯特编码通信。

- 供电与功耗 :模拟供电 2.7V-5.5V,数字供电 1.71V-5.5V,典型静态电流最高 180µA(工业温度范围 -40°C 至 +85°C),掉电模式最低 30µA。

- 集成功能 :内置 1.5V 参考电压(典型漂移低)、带通滤波器、曼彻斯特编解码器、载波检测电路;DAC8741H 额外支持 CRC 校验和看门狗定时器。

- 时钟与接口 :支持内部振荡器、外部晶体振荡器、外部 CMOS 时钟三种时钟模式;UART 接口波特率 1200Hz(HART)/57.6kHz(FF/PA),SPI 接口速率最高 12.5MHz。

- 封装与环境 :24 引脚 4mm×4mm VQFN 封装,工作温度范围 -55°C 至 +125°C,ESD 防护等级 HBM ±8000V、CDM ±1500V。

关键功能说明

- 工作模式 :支持半双工通信,HART 模式实现 FSK 调制解调,FF/PA 模式实现曼彻斯特编码解码;支持全双工自测模式,可验证收发信号链功能。

- 载波检测与 Jabber 抑制 :HART 模式通过 CD 引脚检测有效载波,FF/PA 模式具备 Jabber 抑制功能,防止长时间持续传输,超时可通过寄存器编程(2.048ms 步进)。

- 参考电压配置 :可通过 REF_EN 引脚或寄存器选择内置 1.5V 参考或外部 2.375V-2.625V 参考,满足不同精度需求。

- 数据缓冲与中断 :SPI 接口配备 16 字节深的收发 FIFO,支持阈值中断;UART 接口通过 FIFO 缓冲数据,避免溢出。

- 复位与掉电 :RST 引脚兼具硬件复位和掉电功能,掉电时禁用内部参考与调制解调电路,保留时钟配置以缩短唤醒时间。

典型应用场景

适用于工业过程控制与自动化系统、PLC 或 DCS I/O 模块、现场传感器变送器(如 4mA-20mA 两线制变送器),支持 HART 数字通信与模拟信号并行传输,可实现设备校准、诊断数据交互。

应用设计要点

- 电源与去耦 :模拟电源(AVDD)和数字电源(IOVDD)需分别配置 0.1µF-1µF 低 ESR 陶瓷去耦电容,且靠近引脚放置,减少噪声耦合。

- 布局建议 :分离模拟与数字电路区域,参考电压和电源的去耦电容尽量贴近引脚;XTAL 线路优化长度以降低寄生电容,减少电流消耗。

- 滤波器配置 :通过 BPF_EN 引脚选择内置或外部带通滤波器,HART 模式需在 MOD_OUT 引脚并联 5nF-22nF 电容,FF/PA 模式为 0pF-100pF。

- 寄存器配置 :通过寄存器设置时钟模式、参考电压、FIFO 阈值、Jabber 超时时间等参数;SPI 接口支持 24 位 / 32 位(带 CRC)帧格式,可通过寄存器屏蔽特定中断事件。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高性能音频利器:WM8740立体声DAC全解析2026-03-27 332

-

深度解析DAC8740H和DAC8741H:工业通信调制解调器的卓越之选2026-03-18 611

-

DAC3174 产品核心信息总结2025-11-14 815

-

DAC8162-Q1 产品核心信息总结2025-11-12 887

-

DAC8741H 技术规格与应用总结2025-11-05 680

-

DAC3484和DAC34h84的区别是什么?2025-02-14 719

-

DAC161P997电路板8pcs并联后输出信号电平异常如何解决?2024-12-13 517

-

DAC8740H配合DAC8750使用,连续工作几分钟后DAC8740损坏,怎么回事?2024-11-13 572

-

STM32H7的DAC基础知识和HAL库API2021-08-06 1971

-

dac配置程序调用dac.h报错2018-09-12 2519

-

双MW8740音频dac原理图2016-01-08 1227

-

DAC3484,DAC34H84输出功率定标2013-03-14 1370

全部0条评论

快来发表一下你的评论吧 !