AMC1305L25-Q1 汽车、±250mV输入、电流检测增强隔离调制器技术手册

描述

AMC1305-Q1 器件是一款精密的 δ-σ (ΔΣ) 调制器,其输出通过具有很强抗磁干扰能力的电容式双隔离栅与输入电路隔开。该屏障经认证可提供高达 7000 V 的增强隔离峰符合 DIN V VDE V 0884-10、UL1577 和 CSA 标准。该器件与隔离式电源结合使用,可防止高共模电压线上的噪声电流进入本地系统接地并干扰或损坏低压电路。

*附件:amc1305l25-q1.pdf

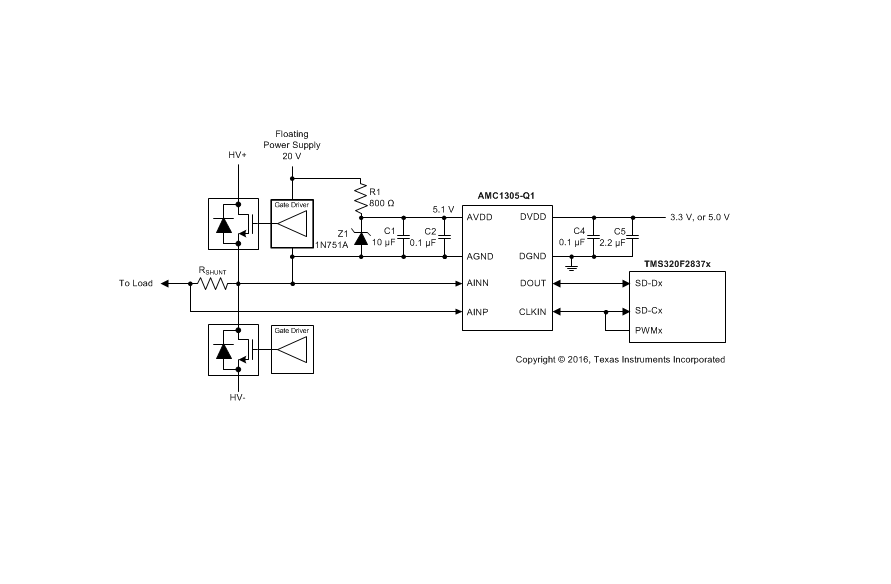

AMC1305-Q1 针对直接连接到分流电阻器或其他低压电平信号源进行了优化,并支持出色的直流和交流性能。分流电阻器通常用于检测牵引逆变器、车载充电器或其他此类汽车应用中的电流。通过使用适当的数字滤波器(即集成在 TMS320F2837x 上)对比特流进行抽取,该器件可以在 78 kSPS 的数据速率下实现 16 位分辨率,动态范围为 85 dB (13.8 ENOB)。

在高侧,调制器提供5 V (AVDD)的标称电压,而隔离式数字接口则采用3.3 V或5 V电源(DVDD)供电。

AMC1305-Q1 采用宽体 SOIC-16 (DW) 封装。

特性

- 符合汽车应用标准

- AEC-Q100 符合以下标准:

- 温度等级 1:–40°C 至 +125°C

- HBM ESD 分类 2 级

- CDM ESD 分类 C6 级

- 引脚兼容系列,具有:

- ±50mV或±250mV输入电压范围

- CMOS 或 LVDS 数字接口选项

- 优异的直流性能:

- 失调误差:±50 μV 或 ±150 μV(最大值)

- 失调漂移:1.3 μV/°C(最大值)

- 增益误差:±0.3%(最大值)

- 增益漂移:±40 ppm/°C(最大值)

- 安全相关认证:

- 7000伏

PK根据 DIN V VDE V 0884-10 (VDE V 0884-10): 2006-12 的增强隔离 - 5000伏

有效值隔离 1 分钟,符合 UL1577 标准 - CAN/CSA 第 5A 号组件验收服务通知

- 7000伏

- 瞬态抗扰度:15 kV/μs(最小值)

- 高电磁场抗扰度

(参见应用笔记 SLLA181A) - 外部5 MHz至20 MHz时钟输入

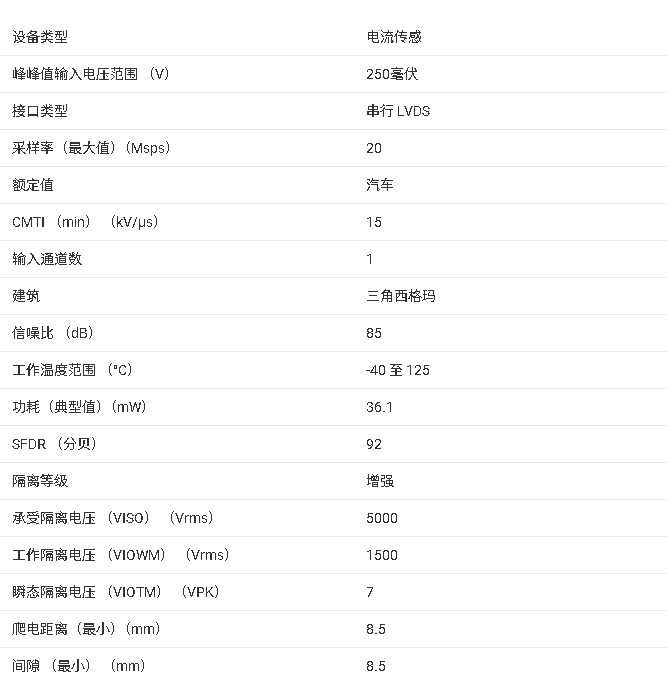

参数

方框图

AMC1305x-Q1 系列(AMC1305L25-Q1、AMC1305M05-Q1、AMC1305M25-Q1)是 AEC-Q100 认证的高精度增强型隔离 ΔΣ 调制器,专为汽车高压应用设计,具备高隔离等级、优异的交直流性能与抗干扰能力,适用于牵引逆变器、车载充电器等场景的电流 / 电压检测。

核心参数与特性

- 性能规格 :16 位分辨率,微分非线性(DNL)±0.99 LSB,积分非线性(INL)±5 LSB;偏移误差最大 ±150 µV,偏移漂移最大 1.3 µV/°C,增益误差最大 ±0.3%。

- 输入范围与接口 :支持 ±50 mV(AMC1305M05-Q1)或 ±250 mV(AMC1305L25/Q1、AMC1305M25-Q1)差分输入;提供 CMOS 或 LVDS 数字接口,外部时钟输入范围 5 MHz-20.1 MHz。

- 隔离与抗干扰 :增强型隔离等级,峰值隔离电压 7000 VPK,1 分钟耐压 5000 VRMS;共模瞬态抗扰度(CMTI)最小 15 kV/µs,电磁干扰免疫力强。

- 供电与功耗 :高压侧供电(AVDD)4.5V-5.5V,控制器侧供电(DVDD)3.0V-5.5V;高压侧工作电流典型值 6.5 mA,控制器侧电流 2.7 mA-8.0 mA(视接口类型而定)。

- 封装与环境 :16 引脚 SOIC(DW)封装(10.3mm×7.5mm),工作温度范围 -40°C 至 +125°C,ESD 防护等级 HBM ±2500V、CDM ±1000V。

关键功能说明

- 调制与滤波 :二阶 ΔΣ 调制器输出 1 位比特流,需搭配外部数字滤波器(如 sinc³ 滤波器) decimation 处理;支持过采样率(OSR)配置,最高可实现 85 dB 动态范围。

- 隔离特性 :采用电容式双隔离屏障,抗磁干扰能力强,符合 DIN V VDE V 0884-10、UL1577 等安全标准,适用于高压与低压侧隔离场景。

- 故障安全与过范围输出 :高压侧供电缺失时输出保持稳定,避免系统误动作;输入超量程时,每 128 个时钟周期输出一个特定比特,区分供电故障与满量程输入。

- 抗干扰性能 :共模抑制比(CMRR)最高 -104 dB(直流),输入带宽 800 kHz-1 MHz,能有效抑制高压环境中的噪声与瞬态干扰。

典型应用场景

适用于汽车牵引逆变器、车载充电器(OBC)、DC-DC 转换器、电池管理系统(BMS)等高压场景,可通过分流电阻实现电流检测,或通过电阻分压器实现电压检测,适配 TMS320F2837x 等 MCU 的 sigma-delta 滤波器模块(SDFM)。

应用设计要点

- 电源与去耦 :AVDD 和 DVDD 引脚需分别配置 0.1 µF 低 ESR 陶瓷去耦电容,靠近引脚放置;高压侧供电可采用齐纳二极管或 LDO 稳压,建议增加 10 µF 滤波电容。

- 布局建议 :严格保持引脚间爬电距离与电气间隙≥8 mm;模拟输入走线远离数字电路,LVDS 接口需在靠近器件处放置 100 Ω 终端电阻,确保信号完整性。

- 输入配置 :电流检测时直接连接分流电阻,电压检测需通过高精度电阻分压器衰减高压;为抵消偏置电流影响,建议在 AINN 引脚串联与检测电阻等值的匹配电阻。

- 时钟与同步 :多通道应用时,需同步外部时钟(CLKIN)以保证采样一致性;时钟占空比建议保持在 40%-60%,确保调制器稳定工作。

-

高精度隔离式Δ-Σ调制器AMC1305x的技术解析与应用2026-04-18 119

-

高精度隔离式Δ - Σ调制器AMC1305x:设计指南与应用解析2026-01-23 386

-

AMC1305x-Q1:高精度隔离式Δ-Σ调制器的技术剖析与应用指南2026-01-22 317

-

AMC1306M25-Q1:汽车应用中的高精度隔离调制器2026-01-21 534

-

AMC3306M25-Q1:汽车级精密隔离调制器的卓越之选2026-01-20 304

-

AMC0x06M25-Q1:汽车级精密隔离Delta-Sigma调制器的深度剖析2026-01-19 297

-

AMC1305M25 ±250mV输入、精密电流检测增强型隔离式调制器技术手册2025-11-12 702

-

AMC1305x-Q1高精度、增强隔离式 Δ-Σ调制器数据表2024-08-20 430

-

AMC1306M25-Q1汽车类高精度±250mV 输入增强型隔离式Δ-Σ调制器数据表2024-08-19 470

-

AMC1300B-Q1汽车类±250mV输入、精密增强型隔离放大器数据表2024-08-16 728

全部0条评论

快来发表一下你的评论吧 !