ADS7046 产品核心信息总结

描述

该ADS7046器件属于引脚对引脚兼容、高速、低功耗、单通道逐次逼近寄存器 (SAR) 型模数转换器 (ADC) 系列。该器件系列包括多种分辨率、吞吐量和模拟输入变体(器件列表见表 1)。

该ADS7046是一款12位、3MSPS SAR ADC,支持0 V至AVDD范围内的单端输入,适用于2.35 V至3.6 V范围内的AVDD。

*附件:ads7046.pdf

内部失调校准功能可在整个 AVDD 和温度工作范围内保持出色的失调规格。

该器件支持由CS和SCLK信号控制的SPI兼容串行接口。输入信号使用 CS 下降沿进行采样,SCLK 用于转换和串行数据输出。该器件支持宽数字电源范围(1.65 V 至 3.6 V),可直接连接到各种主机控制器。该ADS7046符合正常 DVDD 范围(1.65 V 至 1.95 V)的 JESD8-7A 标准。

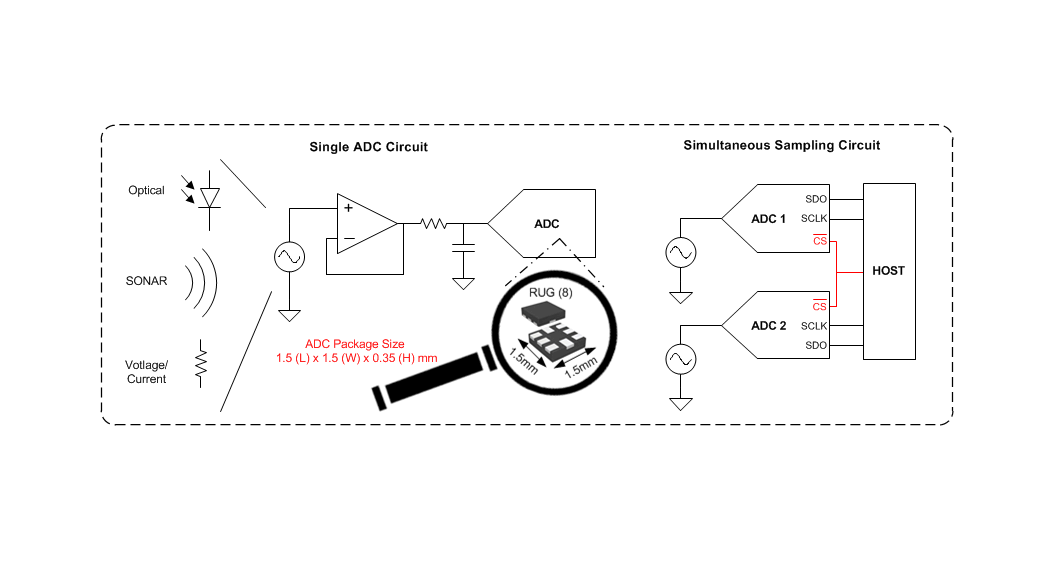

该ADS7046采用8引脚、小型X2QFN封装,额定工作范围为扩展工业温度范围(–40°C至+125°C)。该器件外形小巧,功耗极低,适用于空间受限且需要高速、高分辨率数据采集的电池供电应用。

特性

- 3-MSPS 吞吐量

- 小包装尺寸:

- X2QFN-8 封装(1.5 mm × 1.5 mm)

- 单极性输入范围:0 V 至 AVDD

- 工作范围广:

- AVDD:2.35 V 至 3.6 V

- DVDD:1.65 V 至 3.6 V(独立于 AVDD)

- 温度范围:–40°C 至 +125°C

- 卓越的性能:

- 12 位 NMC DNL,±0.3LSB INL

- 2 kHz时为71.2 dB SINAD

- 69.5 dB SINAD(1 MHz时)

- 低功耗:

- 3.8 mW(3 MSPS),3.3V AVDD

- 100 kSPS 时为 115 μW,采用 3.3V AVDD

- 67 μW(100 kSPS),2.5V AVDD

- 集成偏移校准

- SPI 兼容串行接口:60 MHz

- 符合 JESD8-7A 标准的数字 I/O

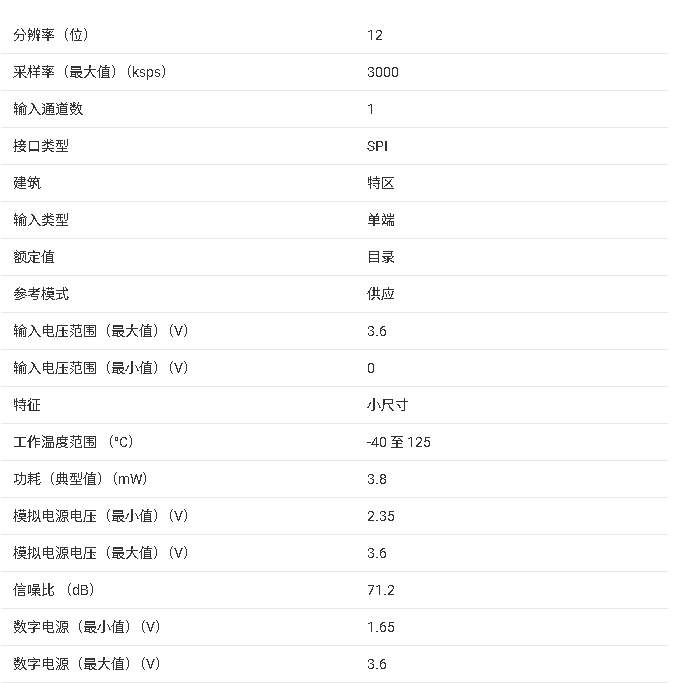

参数

方框图

ADS7046 是一款 12 位、3 MSPS 高速低功耗 SAR ADC,支持单端输入,采用超小封装,兼具高速度与低功耗特性,适用于对尺寸、功耗和采样速率有严格要求的工业与通信数据采集应用。

核心参数与特性

- 性能规格 :12 位无失码分辨率,微分非线性(DNL)±0.15 LSB,积分非线性(INL)±0.3 LSB;信号噪声失真比(SINAD)典型值 71.1 dB(2kHz 时),无杂散动态范围(SFDR)90 dB,全功率带宽 200 MHz。

- 供电与功耗 :模拟供电(AVDD)2.35V-3.6V,数字供电(DVDD)1.65V-3.6V(独立供电);3 MSPS 时功耗 3.8 mW(3.3V AVDD),100 kSPS 时低至 115 µW,静态电流仅 0.02 µA。

- 输入与参考 :单端输入范围 0V 至 AVDD,采样电容 16 pF,输入阻抗典型值 50 Ω;以 AVDD 为参考电压,简化外围设计。

- 接口与时序 :SPI 兼容串行接口,SCLK 最高 60 MHz;CS 下降沿触发采样,15 个 SCLK 完成转换,转换时间 15×tSCLK,采集时间 80 ns。

- 封装与环境 :8 引脚 1.5mm×1.5mm X2QFN 超小封装,工作温度范围 -40°C 至 +125°C,ESD 防护等级 HBM ±2000V、CDM ±1000V。

关键功能说明

- 工作模式 :支持采集(ACQ)、转换(CNV)、偏移校准(OFFCAL)三种状态;上电后自动进入采集状态,CS 下降沿触发转换,转换后返回采集状态。

- 偏移校准 :内置偏移校准功能,上电时需提供 24 个 SCLK 启动校准,正常工作时需 64 个 SCLK,校准后可补偿温漂与电源漂移带来的误差。

- 数据格式与传输 :输出数据为二进制格式,12 位数据随 SCLK 上升沿逐位输出,MSB 先行;CS 高电平时 SDO 引脚呈高阻态。

- 输入特性 :模拟输入引脚具备 ESD 保护,AINM 引脚接地(0V 参考),采样阶段开关闭合充电采样电容,转换阶段断开输入以保证信号稳定。

典型应用场景

适用于光学编码器、声纳接收器、鱼探仪、I-Q 解调器、光线路卡与模块、热成像相机、超声波流量计、手持无线电等高速数据采集场景,可直接对接传感器或经前端放大器驱动,适配单电源或双电源系统。

应用设计要点

- 电源与去耦 :AVDD 引脚需外接 3.3µF 低 ESR 陶瓷去耦电容,DVDD 引脚配置 1µF 电容,均靠近引脚放置,减少电源噪声耦合。

- 布局建议 :采用独立接地平面,分离模拟与数字信号区域;模拟输入走线远离数字电路与噪声源,电荷回踢滤波器组件需贴近器件放置。

- 输入驱动 :高速或高阻抗信号源场景推荐搭配高带宽运放(如 OPA836、THS4031);单端输入需注意共模电压匹配,低速率场景可直接对接传感器(输出阻抗需适配)。

- 校准与时序 :上电后必须完成偏移校准以保证精度;严格遵循时序要求,CS 下降沿至 SCLK 下降沿 setup 时间≥7 ns,SCLK 高低电平时间均不低于 0.45×tSCLK。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS8860 产品核心信息总结2025-11-14 897

-

ADS7042 产品核心信息总结2025-11-13 761

-

ADS1262/ADS1263 产品核心信息总结2025-11-12 1217

-

ADS866x 系列产品核心信息总结2025-11-10 852

-

ADS7142 产品核心信息总结2025-11-06 851

-

ADS7046 12位,3MSPS,单端输入,小型低功耗SAR ADC数据表2024-07-30 658

全部0条评论

快来发表一下你的评论吧 !