大功率PCB设计 (二):电流需求与分配

大功率PCB设计 (二):电流需求与分配

描述

“ 本系列将从电压需求与隔离、电流需求与分配、功率需求与热管理三个章节来介绍大功率 PCB 设计。本章节会通过设计一个 100A PCB 的示例进行讲解。 ”

处理大电流是高功率 PCB 设计的核心挑战。不当的电流管理会导致过热、压降过大,甚至使铜皮熔断。本文将重点介绍如何根据电流需求设计导体、过孔,并应对电流分配的挑战。

1. 计算载流量:IPC-2152 标准

设计的出发点是确定最大负载电流。如果只知道最大功率,请使用最低工作电压来计算最大电流,以评估最坏情况。

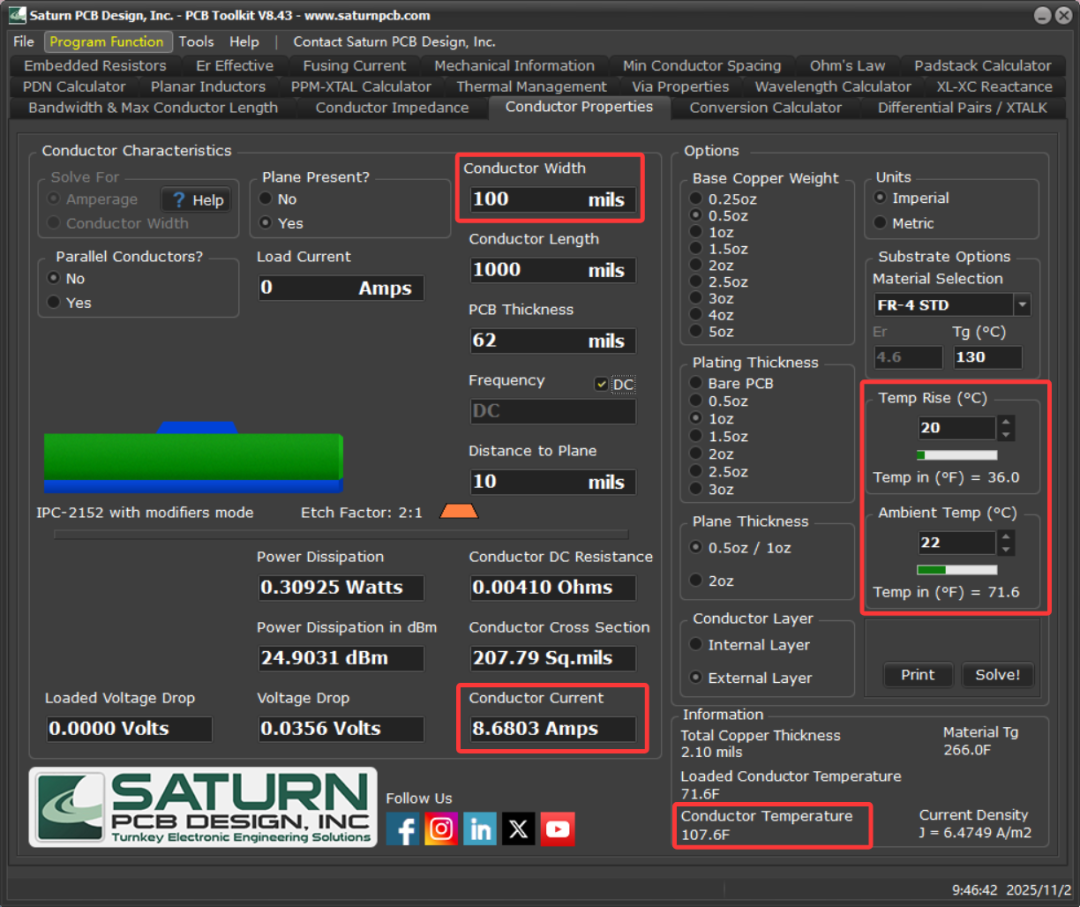

IPC-2152(印制电路板载流量标准)是计算导体宽度和温升关系的权威指南。使用 Saturn PCB Toolkit,通过输入走线宽度、铜箔厚度等核心参数,可以计算出走线允许的最大电流。以下是几个值得关注的参数:

-

走线(导体)宽度:最核心参数,与最大电流密切相关

-

铜厚: 如1oz (35µm) 或 2oz (70µm)。

-

允许温升 (Temp Rise): 您允许铜皮比环境温度高多少度(例如20°C)。

-

环境温度 (Ambient Temp): PCB的工作环境温度。

注意以下几点:

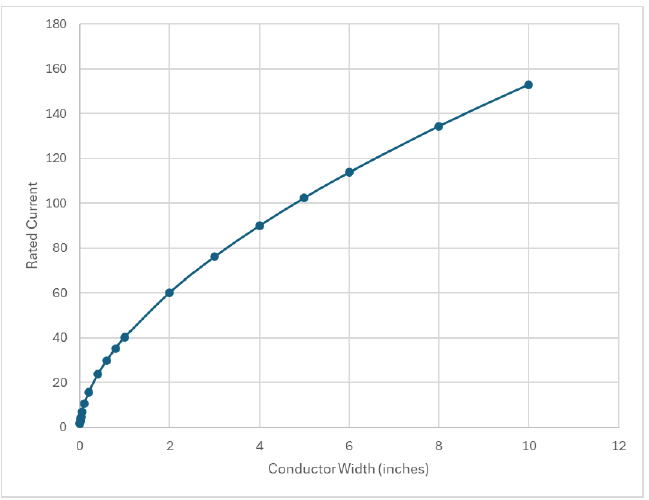

-

最大导体电流并不会随着导体宽度的增加而线性增加。

-

需要考虑邻近铜箔布局及其对大电流路径的影响。

-

随着导体宽度增加,它看起来更像一个铜面(或铜皮),而不再像一条走线。

-

由于系统设计中散热损耗的多样性(或可变性),IPC-2152 标准无法准确计算大面积铜箔的热行为。

-

需要通过仿真来准确预测大面积铜箔的温升。

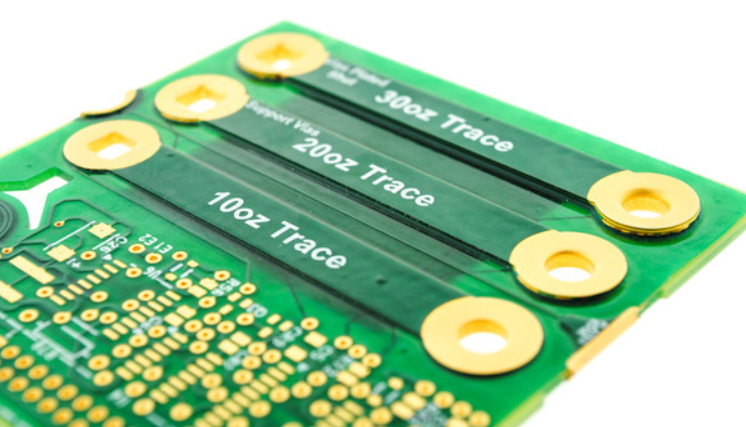

2. 铜厚的选择

-

常见的铜厚(铜箔厚度)范围为 0.5 oz/ft² 到 3 oz/ft²。

-

在内层使用超过 2 盎司的铜会显著增加层压(或压合)问题的风险。

-

外层可以通过选择性电镀达到远超 2 盎司的铜厚。

-

仅保留在供应商资质非常好的情况下,或当 2 盎司铜厚因走线宽度限制而无法满足设计要求时,才使用超过 2 盎司的铜。

3. 100A PCB 设计实例

让我们通过一个实例来演示如何设计承载 100A 电流的路径。

以下为设计的基本原则:

-

考虑所有的电路和设计约束。

-

确定源端和负载端接的位置。

-

避免将敏感电路放置在大电流区域附近。

-

尽可能对栅极驱动等信号进行屏蔽,使其免受高 di/dt(高电流变化率)的影响。

-

确定电路板上可用于大电流路径和大电流元器件的区域。

-

在层叠设计中,避免将大电流路径放置在除其回流路径或屏蔽层之外的任何其他层的旁边。

-

如果由于连接(例如电池设计)的机械结构限制,大电流路径无法与其回流路径紧密耦合,则需要有策略来减轻高 di/dt 期间磁场扩散带来的影响。

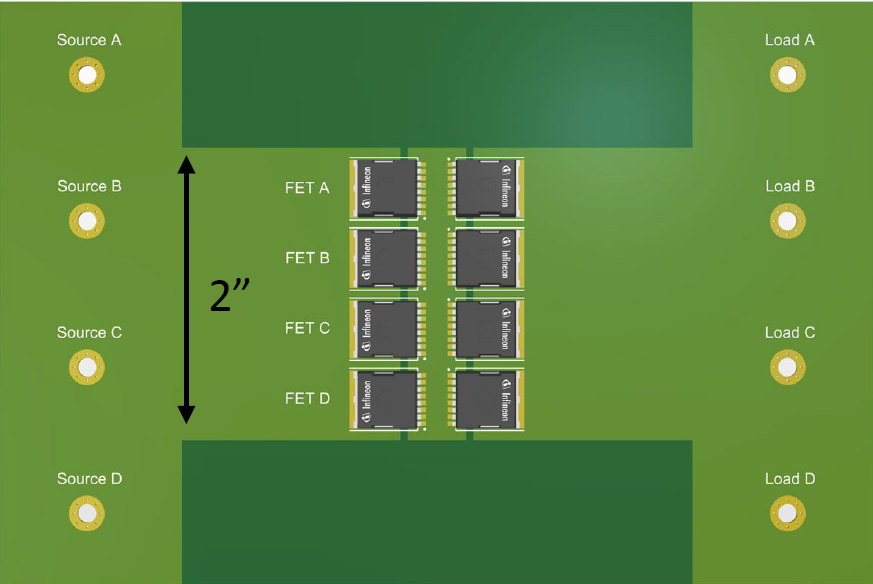

场景: 2英寸宽的可用铜皮路径,环境温度22°C,允许温升20°C。

一旦确定了(布线)可用空间有多大,就要决定所需的铜厚以及层数。

在本例中,假设大电流路径平均分配在所有层上,且没有相邻的回流路径。

注意:

-

内层(铜)厚度等于基铜(Base Copper)的厚度。

-

外层(铜)厚度等于基铜重量加上电镀(Plating)的厚度。

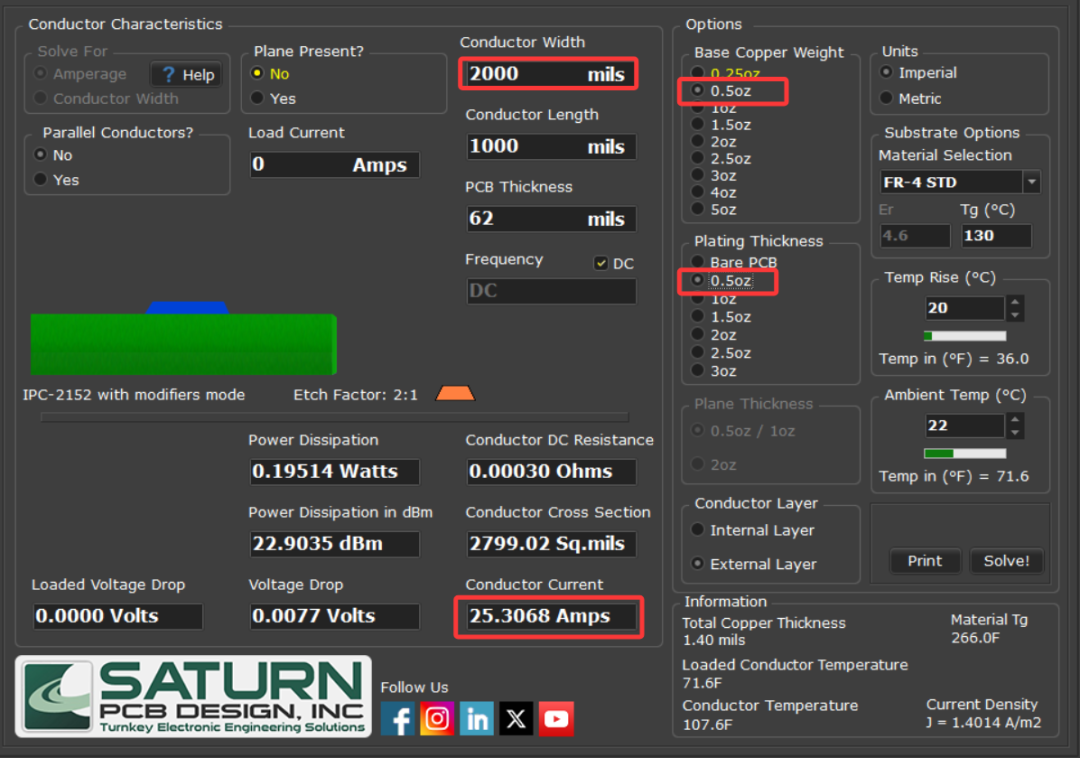

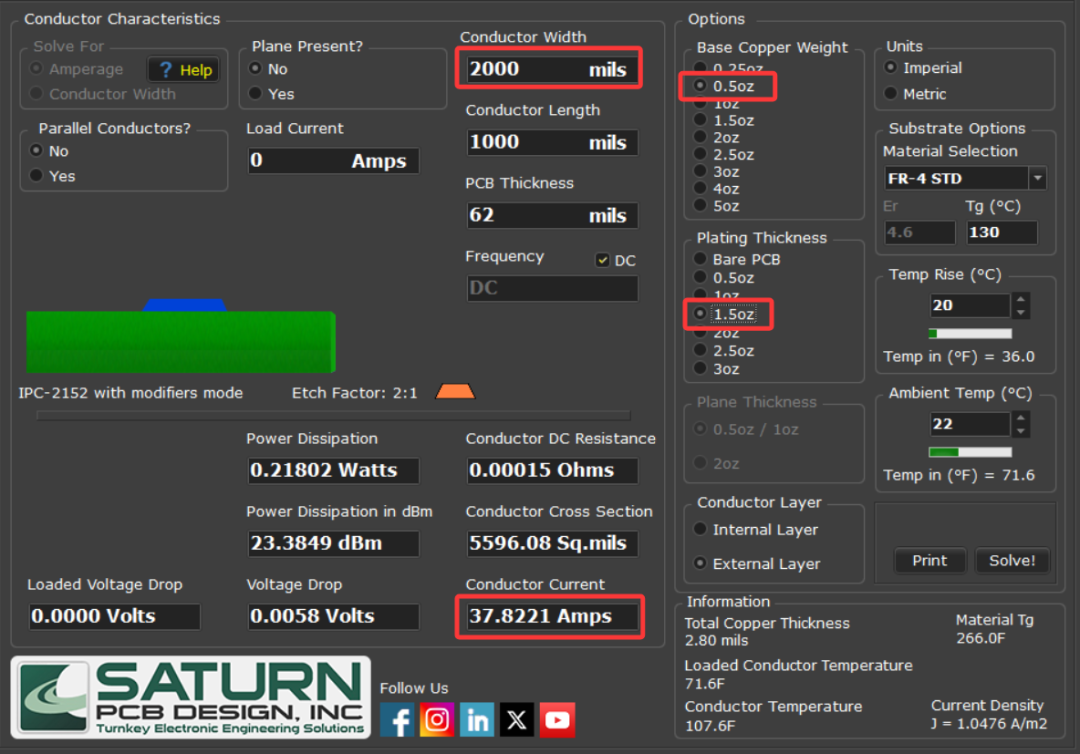

以下为铜厚为分别为外层铜箔为 0.5 oz,1 oz,2 oz 时的额定电流及相关分析:

-

0.5 盎司 (oz) 铜厚 - 2 英寸 (inch) 宽度,每层额定电流 16.9A。

-

(在此条件下)承载 25A 电流时,导体温度为 158.9°F (70.5°C)

-

-

1 盎司 (oz) 铜厚 - 2 英寸 (inch) 宽度,每层额定电流 25.3A。

-

(在此条件下)承载 25A 电流时,导体温度为 106.6°F (41.4°C)。

-

温升 19.4°C

-

没有为 de-rating 或负载分布不均留出余量

-

-

2 盎司 (oz) 铜厚 - 2 英寸 (inch) 宽度,每层额定电流 37.8A。

-

(在此条件下)承载 25A 电流时,导体温度为 85.6°F (29.8°C)

-

温升 7.8°C

-

66% 的电流 de-rating (25A / 37.8A x 100% = 66%)

-

通常来说,温度每升高 10°C,可靠性就会降低 50%

-

结论: 在空间允许的情况下,使用更厚的铜并进行 de-rating 设计,是提高可靠性的关键策略。

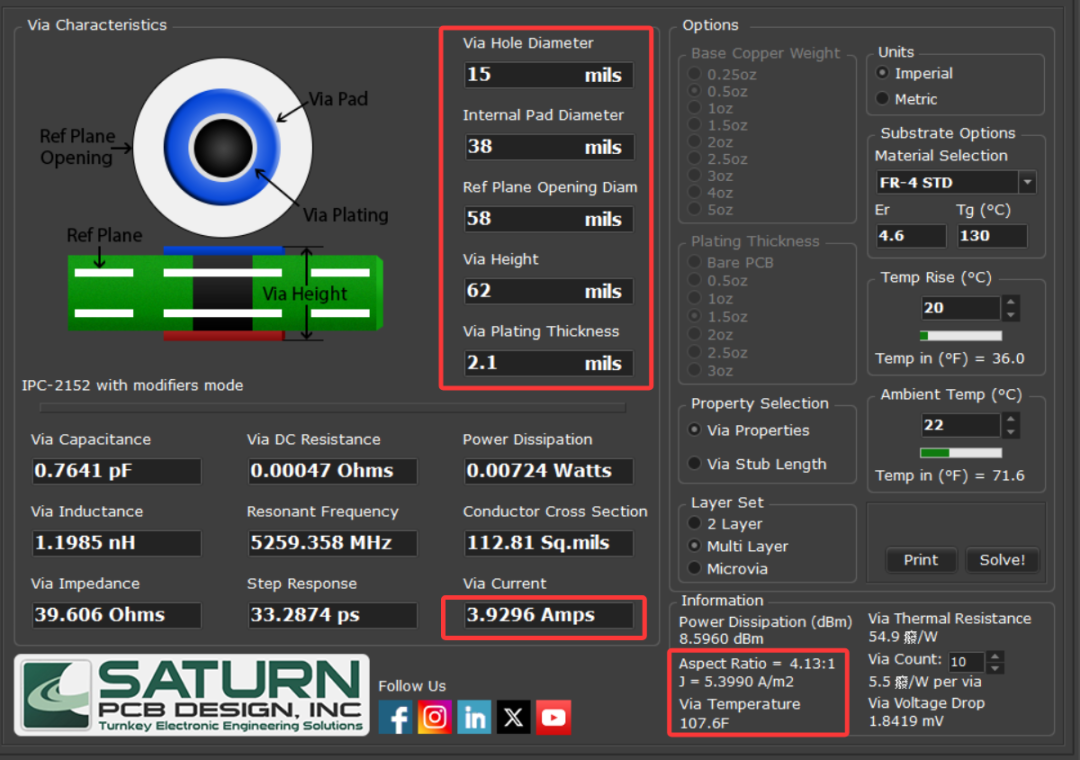

4. 过孔 (Via) 载流量

电流需要在不同层之间传输,这依赖于过孔。当使用多个层时,在源端和负载连接处设计的均流过孔(或负载分配过孔),应至少能承载 100% 的负载。

单个过孔的载流量同样可以使用 IPC-2152 计算器(如Saturn PCB Toolkit)得出。例如,一个 15mil 钻孔、2.1mil 镀层厚度的过孔,在 20°C 温升下约承载 3.9A。

假设 100A 负载,理论上需要 100A / 3.9A = 26 个过孔。

为了提高可靠性,永远不要只使用理论最小值。为了提高可靠性并应对不均匀的电流分布,至少使用 50% 的 de-rating,26 个过孔 / 0.5 = 52 个过孔。

过孔的成本很低,因此在空间合理允许的前提下,应尽可能多地使用过孔。

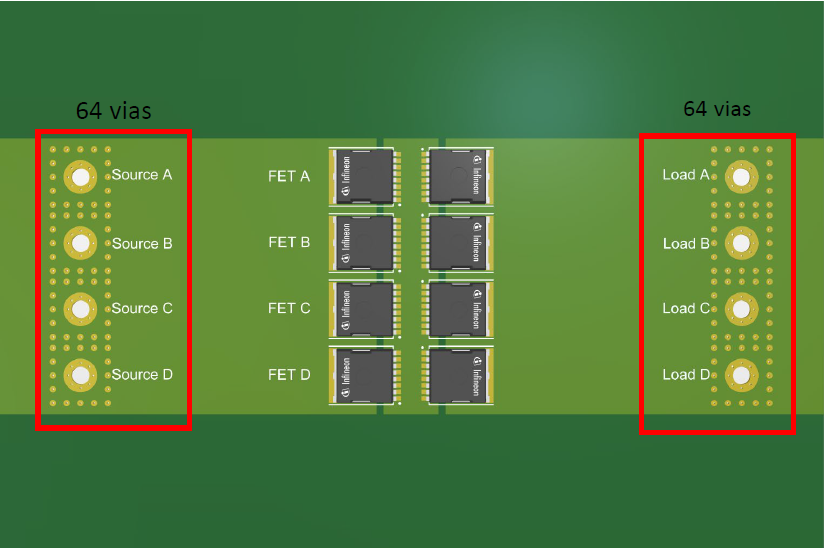

在所有源端和负载连接处均匀地分布过孔。如果空间允许,可以多放些过孔,下图中放了 64 个过孔,de-rating 超过了 50%,提供了更高的可靠性。

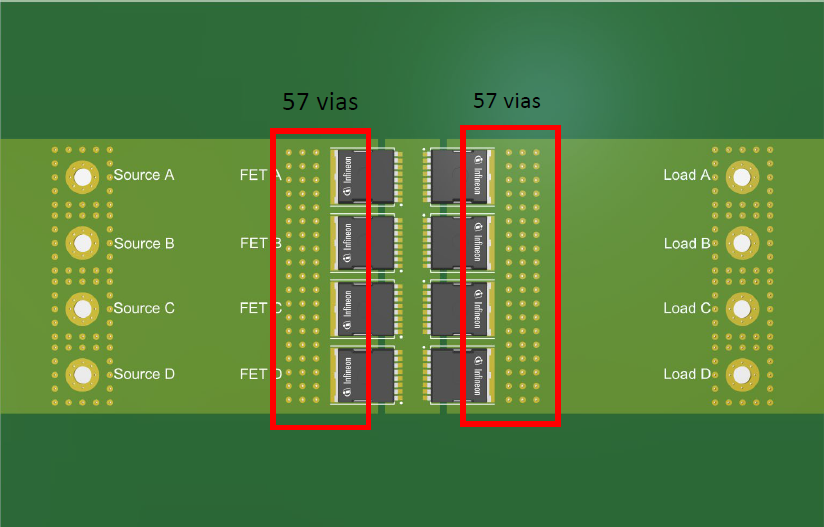

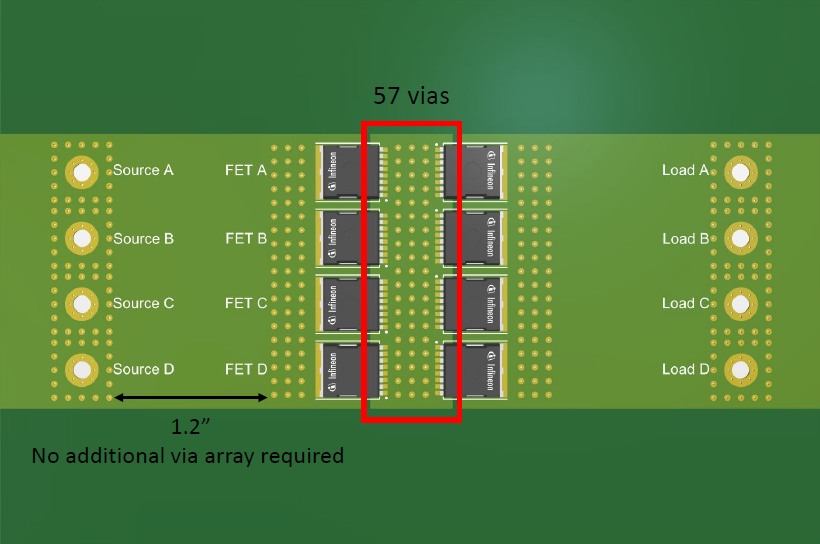

需要使用负载分配过孔(或:均流过孔)将电流传输至贴片 FET。在贴片 FET 周围均匀地分布过孔。采用 100% 负载(计算)和 50% 的 de-rating。为了提高可靠性,最少需要 52 个过孔。

如果顶层和底层都安装了大电流 FET 阵列时,确保所有的大功率节点都连接在一起。在本例中,共源极节点 (common-source node) 也需要设置负载分配过孔 。如果不同过孔阵列之间的距离超过 3 英寸,应考虑增加额外的过孔阵列,以平衡各层之间可能出现的电流分布不均。过孔阵列有助于最小化各层之间的阻抗差异,且有助于分散局部积聚的热量。

5. 电流分配的挑战

在实际布局中,电流并不会“智能地”平均分配。电流会优先选择阻抗最低的路径,这会导致严重的“热点”问题。我们来挑战一把。

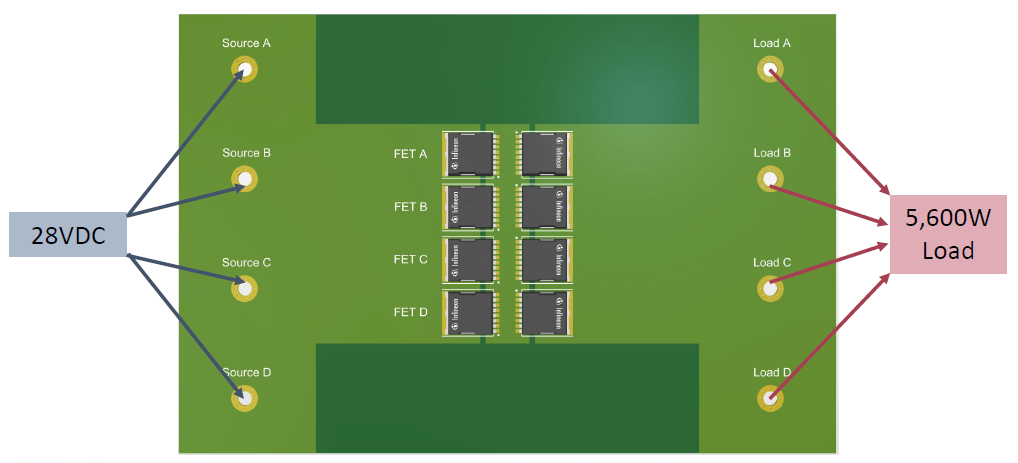

设计要求:

-

电源 为 28V 直流。

-

持续最大负载 为 5,600W。

设计练习:

-

确定电路大功率路径的最大负载条件。

-

5600W / 28VDC = 200A(安培)最大负载。

-

评估最大负载在整个设计中将如何分布。

-

优化布局 ,以避免产生热点 (hotspots) 或使元器件功率过载 。

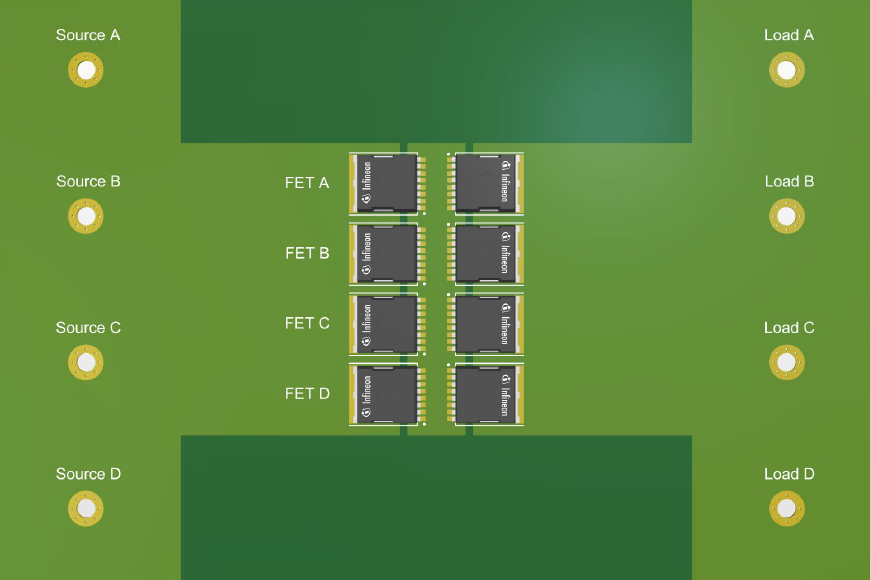

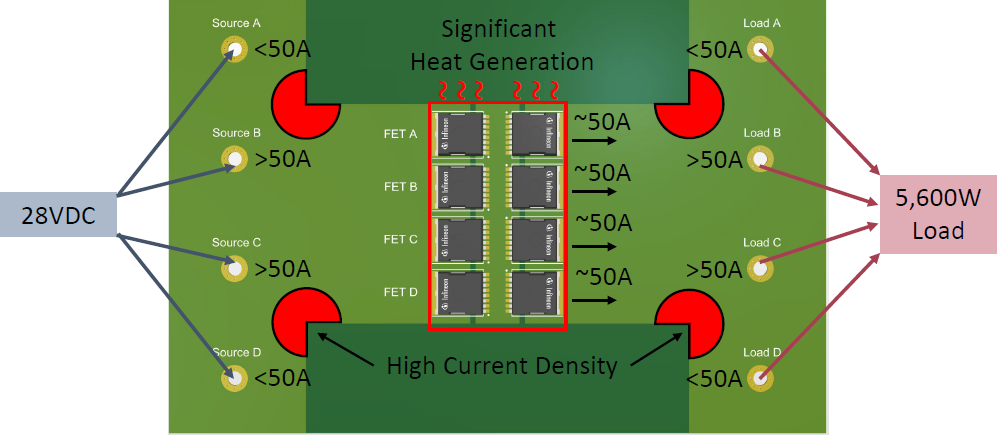

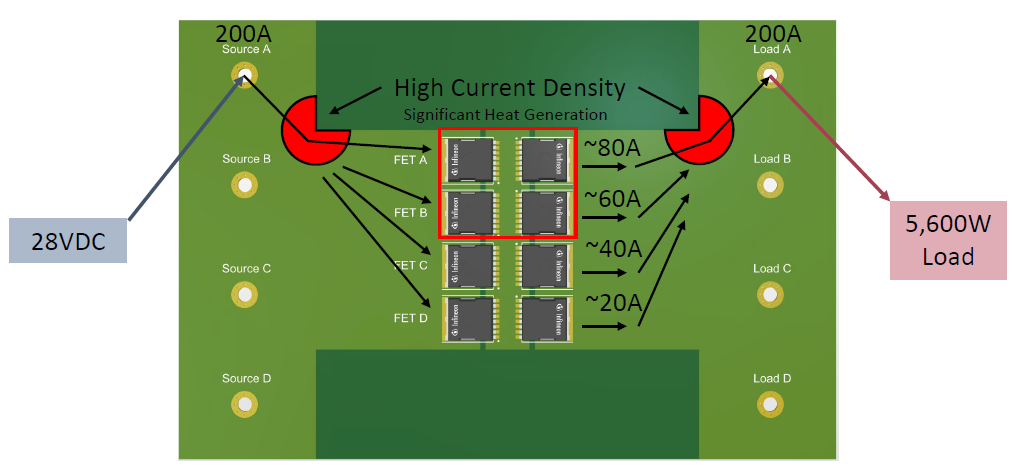

挑战1:布局不平衡

负载 A-D 承受 5,600W 功率。电源 A-D 提供 28VDC 电压。在最大负载下,大功率路径将承载 200A 电流。负载如何在元器件之间分配?负载如何在电源和负载路径上分配?是否存在高电流密度的区域?

以上布局可能产生的问题:

以上布局可能产生的问题:-

如果源和负载连接点位于电路板的内侧(如Source B, C和Load B, C),电流会集中涌向这些低阻抗路径。

-

而外侧路径(Source A, D和Load A, D)承载的电流远小于50A。

-

同时,电流在拐角处会产生“拥塞”,形成高电流密度区域,导致局部过热。

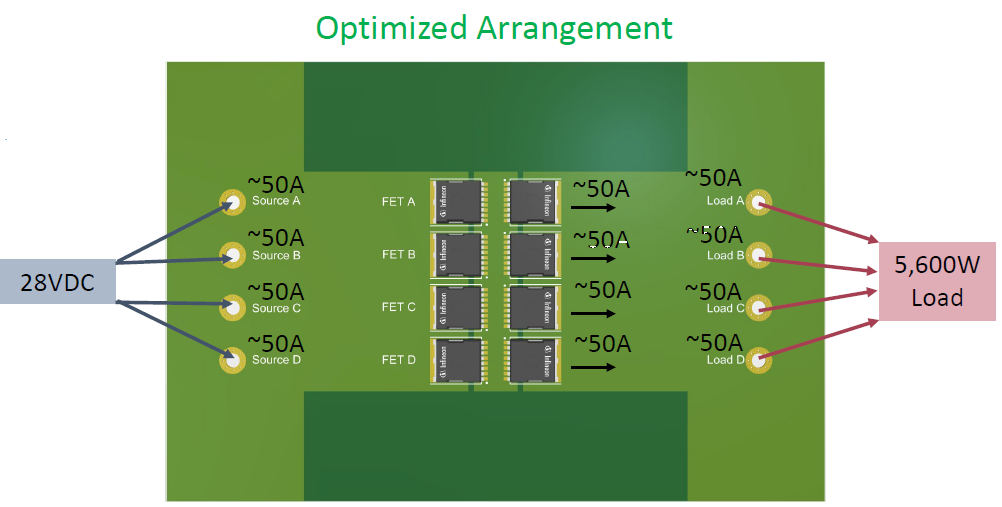

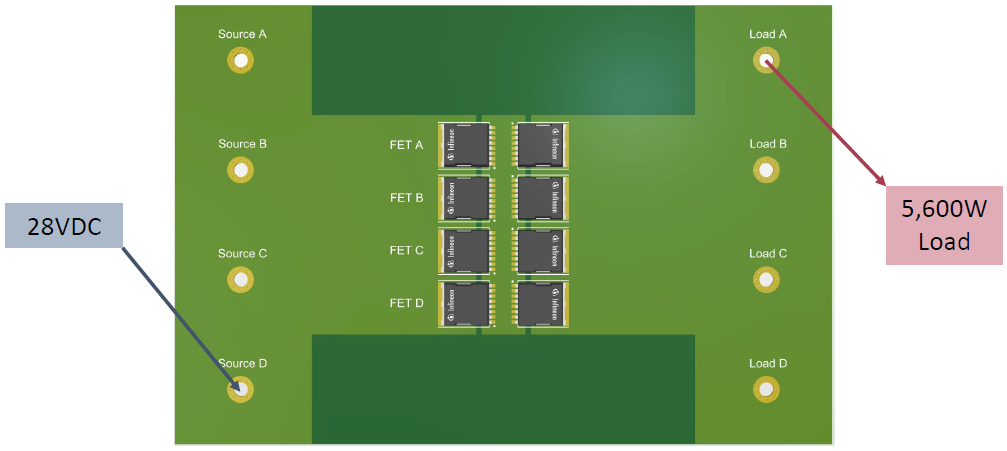

更好的解决方案如下:

-

通过平衡电源到负载路径的阻抗,来优化电流分布。

-

负载均匀分配到各个元器件上。

-

负载均匀分配到电源和负载的各个连接点上。

-

当电流不必绕过拐角时,高电流密度的区域即被消除。

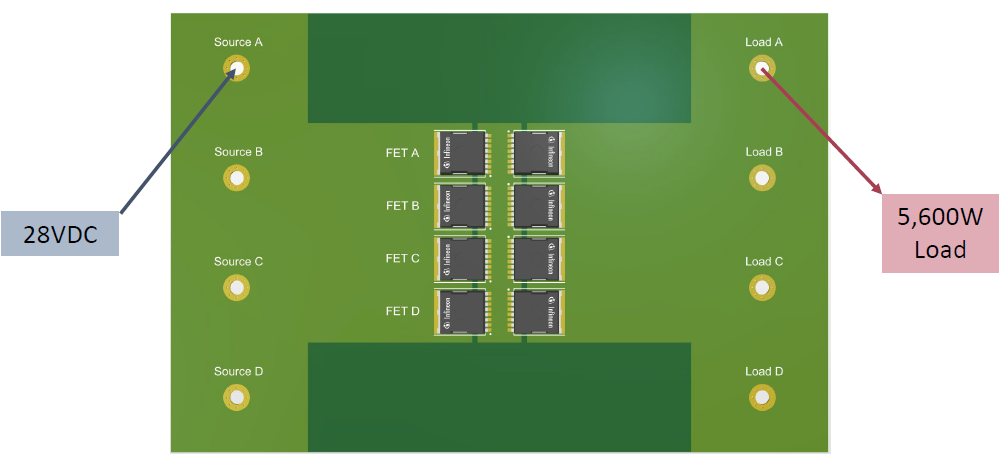

挑战2:单点负载

负载 A (Load A) 承受 5,600W 功率。电源 A (Source A) 提供 28VDC 电压。在最大负载下,大功率路径将承载 200A 电流。负载如何在元器件之间分配?负载如何在电源和负载路径(或:源荷路径)上分配?是否存在高电流密度的区域?

如果 200A 全部由 Source A 供电,并由 Load A 消耗,分析下电流的情况:

-

负载在元器件之间的分配不均衡。

-

由于 FET A 和 FET B 距离路径最近,它们将承载绝大部分电流(例如~80A和~60A),而 FET D 可能只承载 ~20A。

-

这种极不均匀的分配会导致 FET A 和 B 迅速过热失效。

-

在电流拐弯的区域存在高电流密度

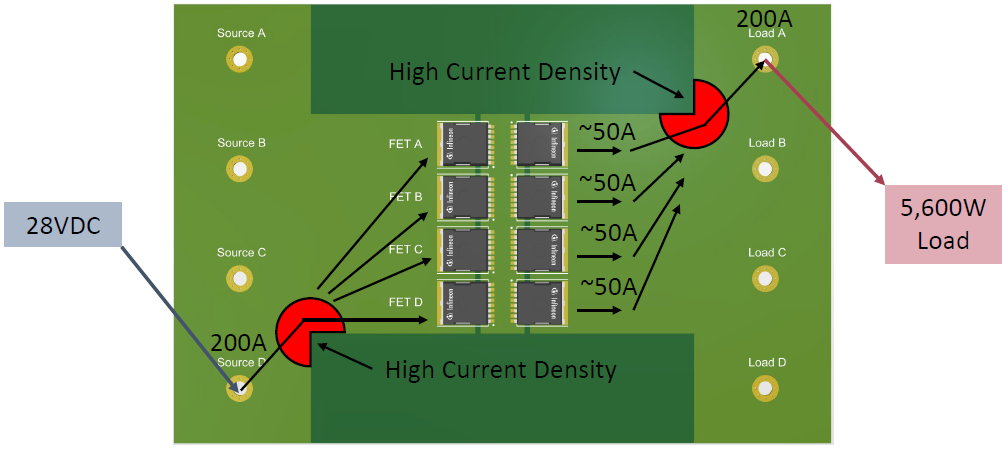

挑战3:对角线负载

负载 A (Load A) 承受 5,600W 功率。电源 D (Source D) 提供 28VDC 电压。在最大负载下,大功率路径将承载 200A 电流。负载如何在元器件之间分配?负载如何在电源和负载路径(或:源荷路径)上分配?是否存在高电流密度的区域?

如果 200A 由Source D供电,由 Load A 消耗,分析下电流的情况:

-

电流会相对均匀地流过所有FET(~50A),因为它们与主路径的阻抗大致相同。

-

FET A 和 FET B 上产生显著的热量。

-

但是,电流在Source D和Load A的入口/出口处仍会形成高电流密度的拐角,引发热点。

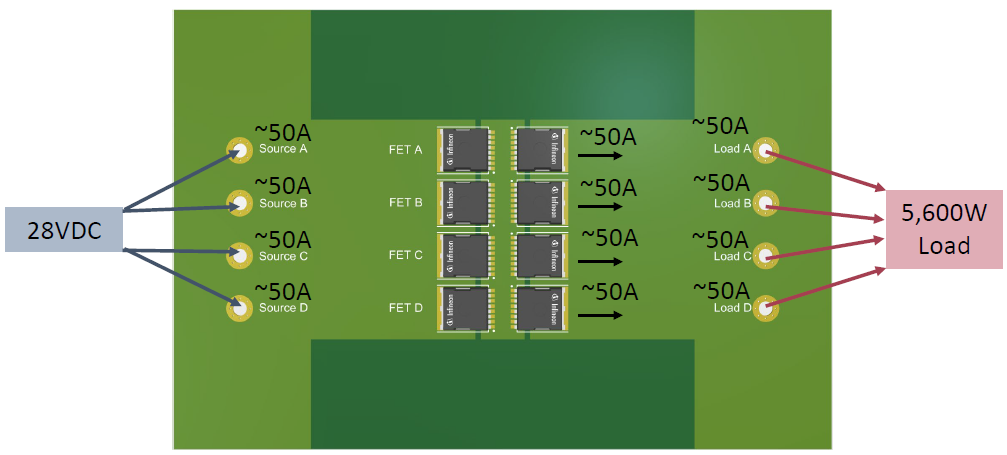

优化策略:通过对称布局,平衡从每个源到每个负载的路径阻抗,可以实现最均匀的电流分配(每个路径~50A),并消除高密度的拐角。

然而,即使布局优化了,也必须进行进一步的热分析(如热仿真)来验证FET的结温和PCB的温升是否在安全范围内。

-

Tips:大功率电源PCB绘制注意事项2024-12-11 924

-

大功率开关电源EMI设计2010-06-04 4625

-

大功率LED PCB板图2012-06-21 8617

-

大功率PCB2016-08-19 6301

-

大功率二总线技术2017-09-16 4608

-

大功率应用的PCB设计的要求及要点2022-08-22 3543

-

满足大功率系统不断增长的故障检测需求2022-10-28 482

-

大功率肖特基二极管都有什么型号?2023-08-28 6593

-

大功率光伏逆变器的PCB设计要点2024-01-18 4074

-

满足大功率部件小尺寸 高功率密度设计需求的大电流电感2024-05-31 1134

-

6kW大功率逆变器PCB设计2024-08-06 2832

-

找到精通大功率PCB设计的工程师真的很难吗2024-11-18 1309

-

大功率PCB设计思路与技巧2025-01-27 1662

-

大功率PCB设计 (一):电压需求与隔离2025-11-04 6268

-

大功率PCB设计 (三):功率需求与热管理2025-11-10 6295

全部0条评论

快来发表一下你的评论吧 !