AMC1106E05 具有±50mV输入和曼彻斯特编码CMOS接口的小型基本隔离式Δ-Σ调制器技术手册

描述

AMC1106是一种精密的 δ-Σ (ΔΣ) 调制器,其输出通过具有很强抗磁干扰能力的电容隔离栅与输入电路隔开。

AMC1106的输入级经过优化,可直接连接到多相电表中常用的分流电阻器或其他低压电平信号源,以实现出色的交流和直流性能。该器件的低输入电压范围为±50 mV,允许使用较小的分流电阻值来最大限度地降低功耗。使用适当的数字滤波器对AMC1106的输出比特流进行灭绝。MSP430F67x、TMS320F2807x 和 TMS320F2837x 微控制器以及 AMC1210 集成了这些数字滤波器,可与AMC1106无缝运行。

*附件:amc1106e05.pdf

在高侧,调制器由

3.3 V或5 V电源(AVDD)供电。隔离式数字接口采用3.0V、3.3V或5V电源(DVDD)供电。

该AMC1106额定在–40°C至+125°C的扩展工业温度范围内。

特性

- ±50mV 输入电压范围经过优化,适用于使用分流电阻器的电流测量

- 曼彻斯特编码或未编码比特流选项

- 出色的直流性能,可在系统级进行高精度传感:

- 失调误差和漂移:±50 μV,±1 μV/°C(最大值)

- 增益误差和漂移:±0.2%,±40 ppm/°C(最大值)

- 3.3V 工作电压,可降低隔离栅两侧的功耗

- 系统级诊断功能

- 高电磁场抗扰度(参见 ISO72x 数字隔离器磁场抗扰度应用报告)

- 安全相关认证:

- 5657-V

PK基本隔离符合 DIN VDE V 0884-11:2017-01 - 4000伏

有效值根据 UL1577 隔离 1 分钟 - CAN/CSA No. 5A-组件验收服务通知

和 DIN EN 61010-1 终端设备标准

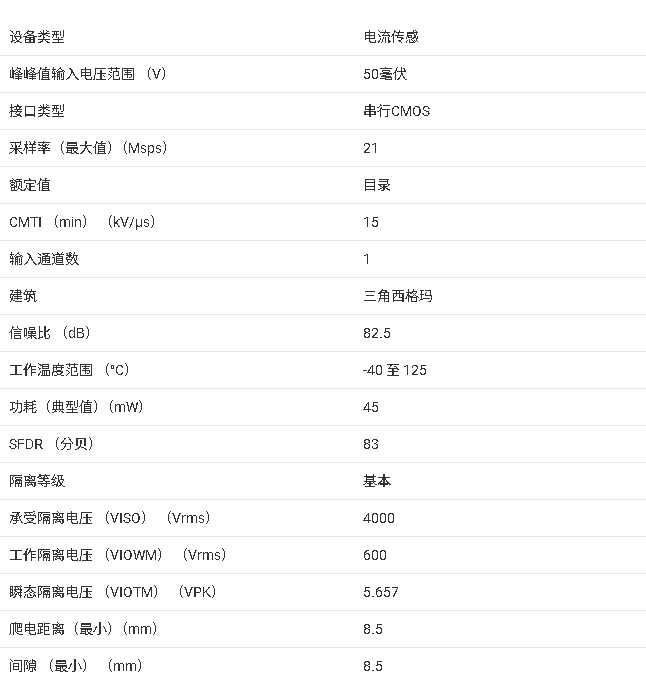

参数

方框图

- 5657-V

AMC1106x 系列(AMC1106E05、AMC1106M05)是小尺寸高精度基础隔离 ΔΣ 调制器,专为三相电表等场景的分流电阻式电流检测设计,具备 ±50 mV 输入范围、CMOS 数字接口(支持曼彻斯特编码 / 非编码输出)与高电磁干扰免疫力,适用于对尺寸和精度有严格要求的工业计量应用。

核心参数与特性

- 性能规格 :16 位分辨率,微分非线性(DNL)±0.99 LSB,积分非线性(INL)±5 LSB;偏移误差最大 ±50 µV,偏移漂移最大 1 µV/°C,增益误差最大 ±0.2%。

- 输入与接口 :差分输入范围 ±50 mV(最大钳位电压 ±64 mV),输入阻抗 4.9 kΩ;AMC1106E05 支持曼彻斯特编码输出,AMC1106M05 支持非编码输出,外部时钟输入范围 5 MHz-21 MHz(AVDD 4.5V-5.5V 时)。

- 隔离与抗干扰 :基础隔离等级,峰值隔离电压 5657 VPK,1 分钟耐压 4000 VRMS;共模瞬态抗扰度(CMTI)最小 15 kV/µs,共模抑制比(CMRR)直流时达 -99 dB,电磁干扰免疫力强。

- 供电与功耗 :模拟侧供电(AVDD)3.0V-5.5V,数字侧供电(DVDD)2.7V-5.5V;AVDD 3.0V-3.6V 时高侧电流典型值 6.3 mA,DVDD 3.3V 时数字侧电流典型值 3.3 mA-4.1 mA(视型号而定)。

- 封装与环境 :8 引脚 SOIC(DWV)封装(5.85mm×7.50mm),工作温度范围 -40°C 至 +125°C,ESD 防护等级 HBM ±2000V、CDM ±1000V。

关键功能说明

- 调制与滤波 :二阶 ΔΣ 调制器输出 1 位比特流,需搭配外部数字滤波器(如 sinc³ 滤波器) decimation 处理,过采样率(OSR)256 时可实现优异动态性能。

- 数字输出选项 :曼彻斯特编码输出(AMC1106E05)支持时钟信号从比特流中恢复,无直流分量;非编码输出(AMC1106M05)适用于常规同步通信场景。

- 故障安全与过范围输出 :模拟侧供电(AVDD)缺失时,DOUT 输出稳定低电平;输入超量程时,每 128 个时钟周期输出一个特定比特,区分供电故障与满量程输入。

- 抗干扰与诊断 :具备共模过压检测功能,共模电压超阈值时输出稳定高电平;输入采用斩波稳定差分放大器,降低偏移与漂移,提升长期稳定性。

典型应用场景

适用于三相电表的分流电阻式电流检测,也可用于工业控制系统中的高精度电流采样,适配 MSP430F67x、TMS320F2807x/F2837x 等 MCU 的内置数字滤波器模块(SD24_B/SDFM),支持多通道同步采样。

应用设计要点

- 电源与去耦 :AVDD 和 DVDD 引脚均需外接 0.1 µF 低 ESR 陶瓷去耦电容,可追加 1 µF-10 µF 电容增强滤波,电容需靠近引脚放置。

- 布局建议 :严格保持引脚间爬电距离与电气间隙≥8.5 mm;分流电阻贴近模拟输入引脚(AINP/AINN),且走线对称;模拟区域与数字区域分离,减少干扰。

- 输入配置 :电流检测时直接连接低阻抗分流电阻,确保额定电流下电压降不超过 ±50 mV;建议在输入前端添加 RC 滤波器,提升抗电磁干扰能力。

- 时钟与同步 :多通道应用时需同步外部时钟(CLKIN),占空比保持在 40%-60%;接口启动时间为 32 个 CLKIN 周期,模拟启动时间 0.5 ms,需预留足够启动时间。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析AMC1303x:小型高精度增强型隔离式Δ - Σ调制器2026-04-18 68

-

AMC1106x:小体积、高精度的基本隔离式ΔΣ调制器2026-01-22 444

-

AMC0x06M05-Q1:汽车级高精度隔离Δ-Σ调制器的深度解析2026-01-19 263

-

AMC1303E0510 ±50mV输入、电流检测增强型隔离式调制器技术手册2025-11-07 775

-

AMC1106M05 ±50mV输入,精密电流检测基本隔离调制器技术手册2025-11-06 568

-

AMC0106M05 ±50mV输入功能隔离式δ-Σ调制器技术手册2025-10-22 796

-

AMC3306M05高精度、±50mV输入增强型隔离式Δ-Σ调制器数据表2024-08-19 420

-

AMC1106x小型高精度基本型隔离式Δ-Σ调制器数据表2024-08-16 410

全部0条评论

快来发表一下你的评论吧 !