DAC38RF85 14 位、9GSPS、6x-24x 插值、6 和 9 GHz PLL 数模转换器技术手册

描述

DAC38RFxx 是一系列高性能、双通道/单通道、14 位、9GSPS 射频采样数模转换器 (DAC),能够合成 0 至 4.5 GHz 的宽带信号。高动态范围使 DAC38RFxx 系列能够为各种应用生成信号,包括用于无线基站和雷达的 3G/4G 信号。

这些器件具有低功耗JESD204B接口,具有多达 8 个通道,最大比特率为 12.5 Gbps,允许每通道 1.25 GSPS 复合的输入数据速率。DAC38RFxx 每个通道提供两个数字上变频器,并具有多种插值速率选项。数字正交调制器具有独立的频率灵活 NCO,可支持多频段作。可选的低抖动PLL/VCO允许使用较低频率的基准时钟,从而简化了DAC采样时钟的生成。

*附件:dac38rf85.pdf

特性

- 14 位分辨率

- 最大DAC采样率:9 GSPS

- 主要规格:

- 2.1 GHz 时的射频满量程输出功率:

- DAC38RF80/90/84:0 dBm

- DAC38RF83/93/85:3 dBm(带 2:1 巴伦)

- 频谱性能(片上PLL,DIFF):

- fDAC = 5898.24 MSPS,fOUT = 2.14 GHz

- WCDMA ACLR:75 dBc

- WCDMA alt-ACLR:77 dBc

- fDAC = 8847.36 MSPS,fOUT = 3.7 GHz

- 20 MHz LTE ACLR:63 dBc

- fDAC = 9 GSPS,fOUT = 1.8 GHz

- IMD3 = 70 dBc(–6 dBFS,10 MHz音调间隔)

- NSD = –157 dBc/Hz

- fDAC = 5898.24 MSPS,fOUT = 2.14 GHz

- 2.1 GHz 时的射频满量程输出功率:

- 每个DAC的双频数字上变频器

- 6、8、10、12、16、18、20 或 24 倍插值

- 4 个独立的 NCO,分辨率为 48 位

- JESD204B 接口,子类 1

- 支持多芯片同步

- 最大通道速率:12.5 Gbps

- 单端输出,带集成巴伦 (DAC38RF80/90/84),覆盖 700 MHz 至 3800 MHz

- 带旁路的内部 PLL 和 VCO

- fC(VCO) = 5.9 或 8.9 GHz

- 功耗:1.4 至 2.2 W/ch

- 电源:–1.8 V、1 V、1.8 V

- 封装:10 x 10 mm BGA,0.8 mm 间距,144 个焊球

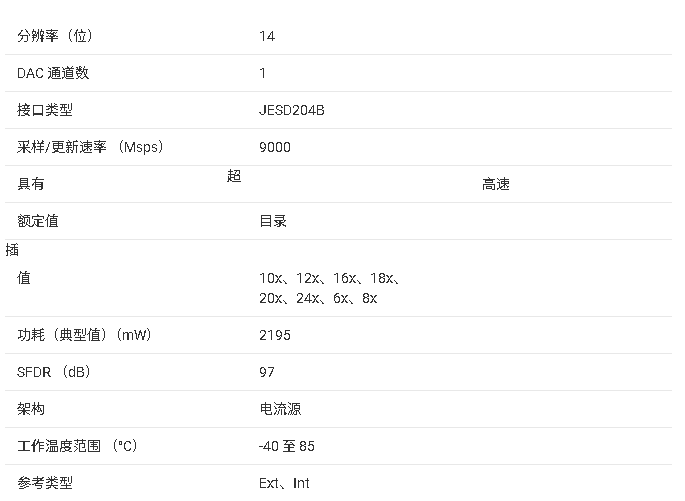

参数

方框图

DAC38RF85 是一款 14 位 9-GSPS 单通道射频采样数模转换器(DAC),集成片内 PLL/VCO 与单频段数字上变频器(DUC),支持 JESD204B 高速接口,采用差分输出设计,专为无线通信、雷达、卫星通信等对带宽、采样速率和动态范围要求严苛的射频应用设计。

核心参数与特性

- 性能规格 :14 位分辨率,微分非线性(DNL)典型值 ±3 LSB,积分非线性(INL)典型值 ±4 LSB;无杂散动态范围(SFDR)最高 97 dBc,噪声谱密度(NSD)低至 -157 dBc/Hz,WCDMA ACLR 达 75 dBc,20 MHz LTE ACLR 达 63 dBc。

- 采样与输出 :最大采样率 9 GSPS,支持 8/12/16 位多模式输入;差分满量程输出功率 3 dBm(2.14 GHz 带 2:1 巴伦),输出阻抗 100 Ω(差分),输出合规范围 1.3-2.3 V,全量程输出电流 10-40 mA 可调。

- 信号处理 :内置单频段 DUC,支持 6-24 倍可编程插值滤波,阻带抑制 ≥90 dB;集成 4 个独立 48 位数控振荡器(NCO),支持复杂基带信号上变频,覆盖 0-4.5 GHz 宽带信号合成。

- 接口与供电 :JESD204B 子类 1 接口,最多 8 通道,单通道速率最高 12.5 Gbps;供电电压包括 -1.8 V(VEE18N)、1.0 V(模拟 / 数字核心)、1.8 V(外设),典型功耗依工作模式为 2195-4894 mW。

- 封装与环境 :144 引脚 FCBGA 封装(10.00mm×10.00mm),工作温度范围 -40°C 至 +85°C,结温最高 150°C,ESD 防护等级 HBM ±1000V。

关键功能说明

- 信号处理能力 :单频段 DUC 支持灵活插值配置,搭配 sin (x)/x 补偿滤波器,可优化信号频率响应;48 位 NCO 支持相位相干跳频,频率与相位可精准编程,适配多载波信号生成需求。

- 高速接口与同步 :JESD204B 接口支持多芯片同步,SYSREF 信号实现确定性延迟;支持单链路配置,链路故障时可独立重启,保障工作稳定性。

- 片内 PLL/VCO :集成低抖动 PLL 与双 VCO(中心频率 5.9 GHz/8.85 GHz),支持外部低频率参考时钟生成高采样率时钟,VCO 频率范围可通过寄存器配置,适配不同射频频段。

- 功耗与保护控制 :支持正常、待机、关断多种工作模式,关断功耗低至 208 mW;集成功率放大器保护(PAP)模块,可监测输入信号功率并自动衰减输出,避免过载;内置温度传感器与完善告警机制,覆盖链路错误、PLL 失锁等场景。

- 测试与校准 :支持 PRBS 图案测试、JESD204B 链路层测试,提供眼图扫描功能;内置偏移补偿电路与 SYSREF 捕获校准机制,可优化多设备同步精度。

典型应用场景

主要用于无线通信系统、通信测试设备、任意波形发生器、军用软件无线电、雷达与卫星通信(SATCOM)、分布式天线系统,适配宽带射频信号生成与高速数据转换需求。

应用设计要点

- 电源配置 :模拟电源(VDDA1/VDDA18 等)与数字电源(VDDIG1/VDDE1 等)需独立供电,各电源引脚就近配置 0.1 µF 去耦电容,VEE18N 建议最后使能,避免影响其他电源启动。

- 时钟与同步 :选用低抖动参考时钟(推荐抖动 < 100 fs rms),时钟输入支持差分模式;多芯片同步时需统一 SYSREF 信号,通过寄存器配置相位容忍窗口,满足 setup/hold 时序要求。

- 布局与布线 :射频输出采用 100 Ω 差分共面波导走线,缩短迹线长度并均匀布置接地过孔;SerDes 高速信号线控制阻抗(50 Ω 单端 / 100 Ω 差分),避免锐角弯曲,相邻迹线间保留足够隔离。

- 配置与校准 :上电后需按 “拉低 TXENABLE → 供电 → 复位 → 配置寄存器 → 启动 SYSREF 同步 → 拉高 TXENABLE” 流程操作;根据应用场景配置插值倍数、NCO 频率与 JESD204B 帧格式,启用 PAP 功能时需设置合理阈值与衰减步长。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

高性能14位2.5 GSPS RF数模转换器AD9739的深度解析2026-04-13 184

-

DAC38RF83技术手册2025-11-10 614

-

DAC38RF86技术手册2025-11-07 814

-

DAC38RF82 双通道、14位、9GSPS、1x-24x插值、6 和 9 GHz PLL 数模转换器技术手册2025-11-06 1097

-

DAC39RFx10-SP/SEP 系列数模转换器技术文档总结2025-10-24 1098

-

AD9161/AD9162 11位、12 GSPS、RF数模转换器技术手册2025-05-02 2168

-

DAC5670-SP 14位2.4 GSPS数模转换器(DAC)数据表2024-07-30 491

-

DAC38RFxx双通道或单通道、单端或差分输出、14位、9GSPS、射频采样DAC数据表2024-07-12 474

-

AD9119/AD9129:11/14位、5.7GSPS、RF数模转换器2021-03-19 909

-

高性能16位数模转换器AD9164怎么样?2019-10-23 3157

-

AD9164BBCZ数模转换器2018-09-07 1993

-

AD9162BBCAZ 数模转换器2018-08-28 2168

全部0条评论

快来发表一下你的评论吧 !