Video Processing Subsystem与HDMI示例设计

描述

本文作者:AMD 工程师 Trevor Rishavy

在撰写本文时,HDMI Transmitter Subsystem IP 核与 Video Processing Subsystem IP 核均有多个示例设计可供使用,但并没有演示将两者功能结合在一起来使用的设计。

如需了解有关这些设计的信息,请参阅 PG235 和 PG231。

PG235:

https://docs.amd.com/access/sources/dita/map?isLatest=true&url=pg235-v-hdmi-tx-ss&ft:locale=en-US

PG231:

https://docs.amd.com/access/sources/dita/map?isLatest=true&url=pg231-v-proc-ss&ft:locale=en-US

本篇博文将侧重于概述如何创建和运行设计以将这两个 IP 结合在一起来实现。

注释:此设计按现状提供,不含任何保证。它是在正常发布/测试流程外构建的,仅用于提供指示信息。

SR 门户不支持本设计。如果您对本设计有疑问,请在此论坛板块上发帖:

https://adaptivesupport.amd.com/s/topic/0TO2E000000YKY8WAO/video?language=zh_CN

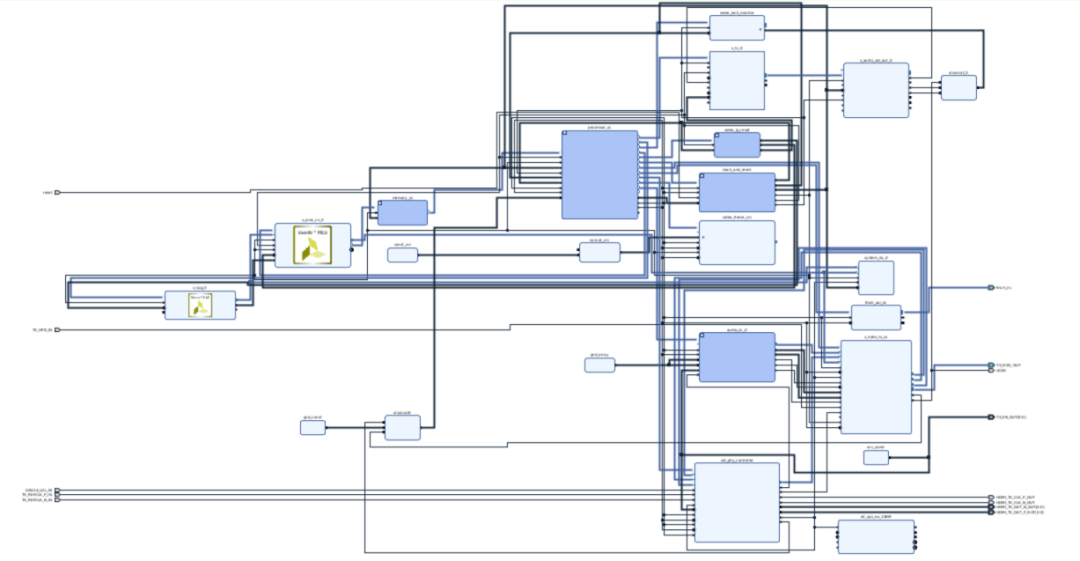

本设计演示了如何在 ZCU102 评估板上使用 AMD Vivado 设计套件 2022.1 来构建和运行 Video Processing Subsystem + HDMI TX 设计。本设计基于产品指南中的 HDMI TX Only 设计创建,随后经过更新,添加了 Video Processing Subsystem 功能。

其目的是为了演示如何将 Video Processing Subsystem 与 HDMI TX Subsystem 结合在一起来运作并快速实现。

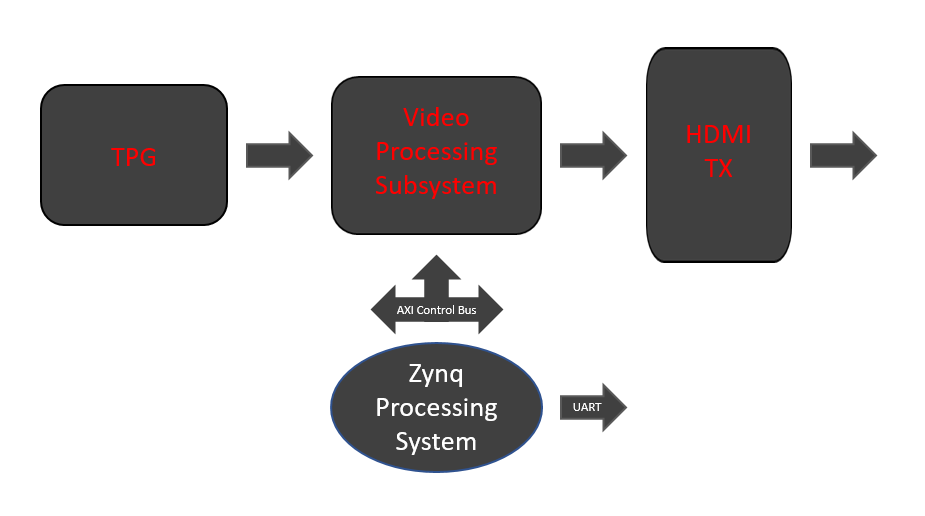

它包括下列组成部分:

复位功能

AMD Zynq 子系统例化,用于控制 IP

GPIO 用于监控状态(原示例设计保留不变)

Test Pattern Generator (TPG) 用于创建视频数据

Video Processing Subsystem 用于转换颜色格式和分辨率

Video PHY Controller

HDMI TX Subsystem

使用提供的脚本创建比特流:

1.在命令行或 Vivado 终端内,运行来自以下目录的 Tcl 脚本,同时确保 hdmi.xdc 文件与该 Tcl 脚本位于相同目录下:

Vivado -source v_proc_ss_0_ex.tcl

2.等待脚本完成,然后运行 Vivado 生成比特流。

此操作能以脚本模式完成,也可以打开 Vivado GUI 并遵循典型的综合、实现、比特流生成流程来完成。

3.生成比特流后,导出 XSA 文件。

如何基于 XSA 来创建 ELF 文件:

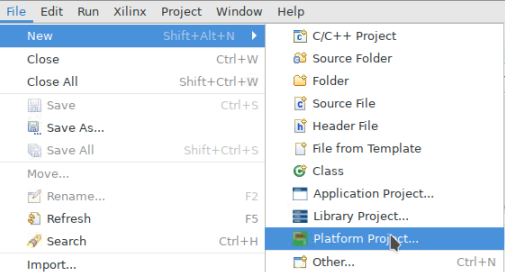

1.打开 AMD Vitis 统一软件平台的 GUI。

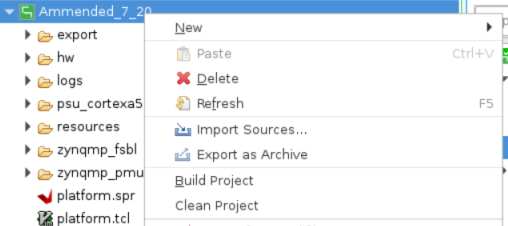

2.创建新的平台工程并指向从 Vivado 工程导出的 XSA。

3.使用构建工具来构建 BSP。

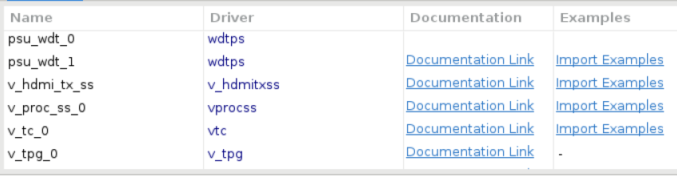

4.构建好 BSP 后,选择“Drivers”中的“Import Examples”。

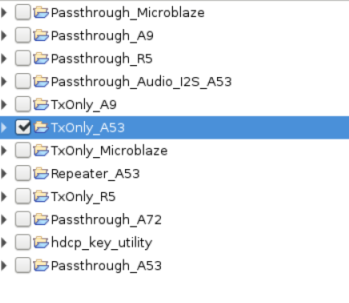

5.导入 HDMI TX Only。

6.将 /src 下的文件替换为 /SW 内的文件。

这些文件均已经过编辑,适用于 VPSS + HDMI 示例。

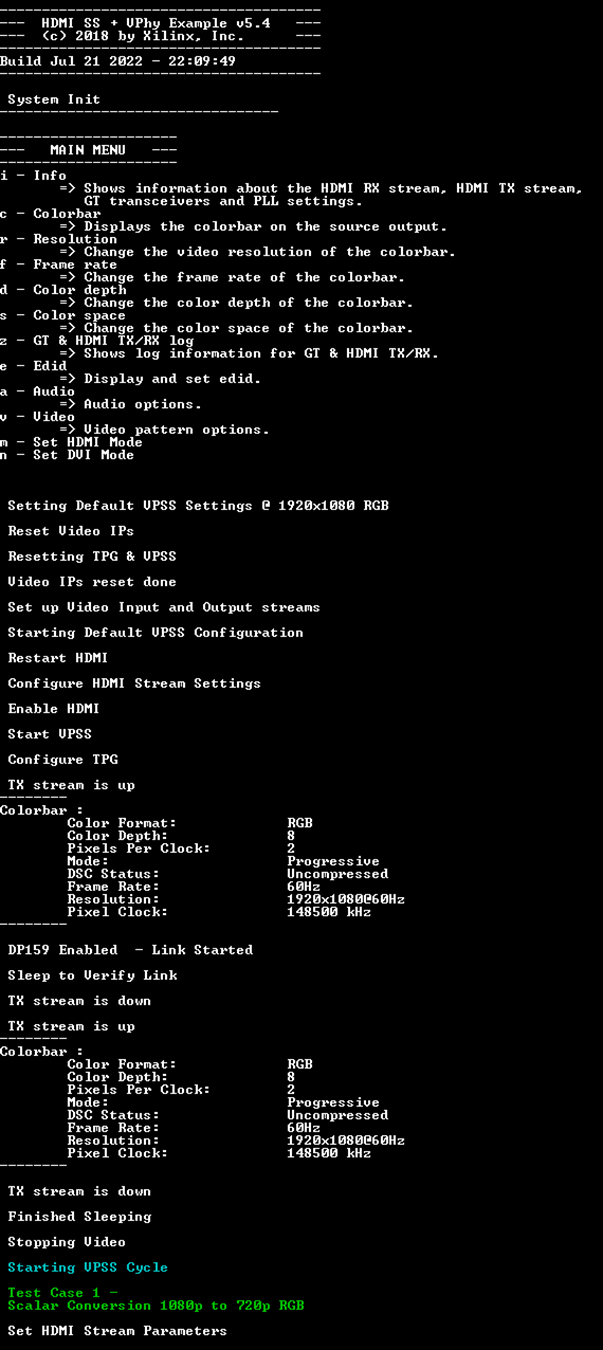

7.构建并测试,下图显示了 UART 控制台。

注释:如需了解有关构建和测试的更多信息,请参阅 PG235 和 PG231。

点击阅读原文,查看相关附件。

-

HDMI VCU118设计移植到VCU128开发板的步骤解析2020-11-20 7793

-

AN65974示例如何链接fifo_slave_block 和 video_out的IP块?2025-05-12 727

-

Video Processing Using FPGAs in Video Surveillance Systems2008-08-08 6806

-

ATSC Standard:AVC Video Transport Subsystem Characteristics2008-10-16 3946

-

如何理解DM8148的HD Video Coprocessor Subsystem和Media Controller Subsystem中的HDVICP22018-05-28 2254

-

mipi-csi2-rx示例设计许可证错误2018-12-28 8068

-

HDMI FrameBuffer示例设计2019-01-03 5146

-

怎么让video_capture示例工作运行?2019-08-14 1309

-

ADV7441A,pdf datasheet (HDMI/D2009-09-11 1015

-

VIDEO PROCESSING FOR DLPTM DIS2009-10-01 743

-

Video and Image Processing Up2009-11-24 672

-

HDMI_1.4_2.0_RX_Subsystem_IP介绍和基础debug建议2022-03-25 5764

-

Video Processing subsystem例程分析2022-10-28 3223

-

microblaze之Video Processing Subsystem调试误区2022-10-31 3017

全部0条评论

快来发表一下你的评论吧 !