ADS1287 技术文档核心内容总结

描述

ADS1287器件是一款低功耗模数转换器 (ADC),集成了可编程增益放大器 (PGA) 和有限脉冲响应 (FIR) 数字滤波器。该ADC适用于地震设备的苛刻需求,需要低功耗的精密数字化。

该ADC具有可编程增益、高阻抗互补金属氧化物半导体(CMOS)放大器,适用于在宽输入信号范围(±2.5 V至±0.156 V)上将检波器和水听器传感器直接连接到ADC。

*附件:ads1287.pdf

ADC集成了一个四阶、固有稳定的δ-Σ(ΔΣ)调制器。调制器数字输出由内部FIR数字滤波器滤波和抽取,以产生ADC转换结果。

FIR 数字滤波器提供高达每秒 1000 个样本 (SPS) 的数据速率。高通滤波器 (HPF) 从转换结果中去除直流和低频分量。片内增益和失调缩放寄存器支持系统校准。

放大器、调制器和数字滤波器在高分辨率模式下的功耗为 4.5 mW(在低功耗模式下为 2.4 mW)。该ADC采用紧凑的5mm×4mm VQFN封装。ADC在–40°C至+85°C温度范围内完全额定。

特性

- 可选作模式

- 高分辨率模式:

- 信噪比:113 dB(1000 SPS,增益 = 1)

- 功率:4.5 毫瓦

- 低功耗模式:

- 信噪比:110 dB(1000 SPS,增益 = 1)

- 功率:2.4 毫瓦

- 总谐失真:–115 分贝

- CMRR:115 分贝

- 高阻抗 CMOS PGA

- 增益 1、2、4、8 和 16

- 数据速率:62.5 SPS 至 1000 SPS

- 灵活的数字滤波器:

- Sinc + FIR + IIR(可选)

- 线性和最小相位响应

- 可编程高通滤波器

- 失调和增益校准

- 同步控制

- SPI 兼容接口

- 模拟电源:5 V 或 ±2.5 V

- 数字电源:2.5 V 至 3.3 V

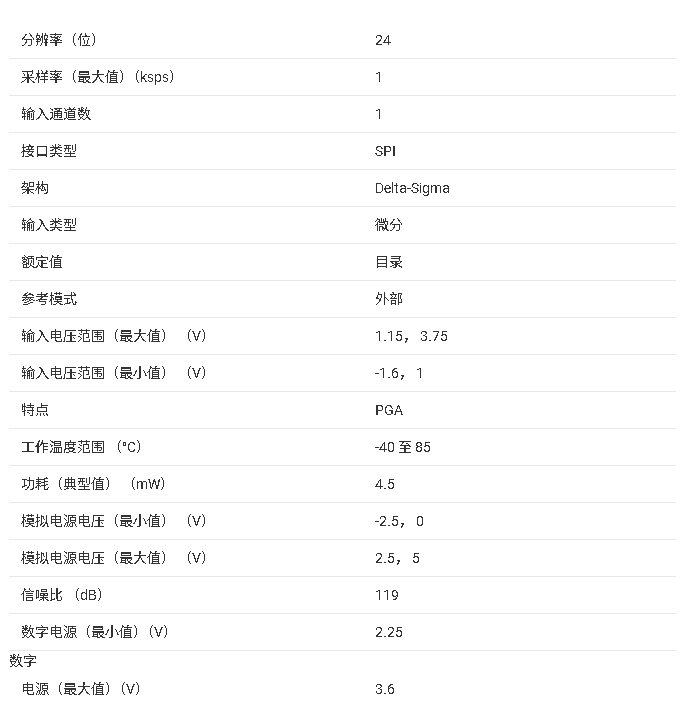

参数

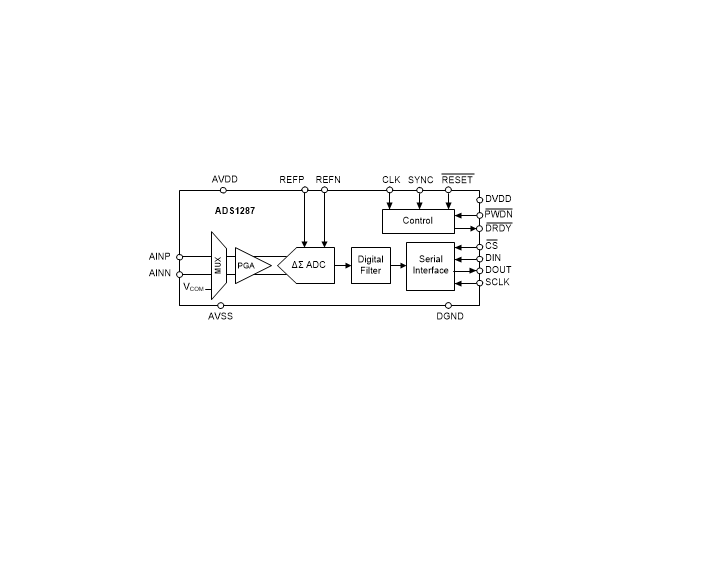

方框图

ADS1287 是德州仪器推出的低功耗、高分辨率 ΔΣ 模数转换器(ADC),集成可编程增益放大器(PGA)与灵活数字滤波器,专为能源勘探、被动地震监测、便携式仪器等对精度与功耗要求严苛的场景设计,文档版本为 SBAS778B,首次发布于 2017 年 6 月,2019 年 8 月修订,包含完整技术参数、功能说明、应用方案及封装信息。

一、核心特性与关键参数

(一)基础性能

- 分辨率与精度 :支持 31 位有效分辨率(FIR 滤波模式),数据速率覆盖 62.5 SPS - 1000 SPS;总谐波失真(THD)低至 -115 dB,共模抑制比(CMRR)达 115 dB,无杂散动态范围(SFDR)超 115 dB,宽温范围内(-40°C 至 +85°C)性能稳定。

- 双工作模式 :

- 高分辨率模式 :1000 SPS、增益 = 1 时,信噪比(SNR)113 dB,功耗 4.5 mW,适配高精度测量场景;

- 低功耗模式 :1000 SPS、增益 = 1 时,SNR 110 dB,功耗 2.4 mW,平衡精度与功耗需求。

- 可编程增益与输入 :集成高阻抗 CMOS PGA,增益可选 1/2/4/8/16 倍,支持 ±2.5 V 至 ±0.156 V 差分输入范围,可直接连接地震检波器、水听器等传感器。

(二)电源与环境适应性

- 供电灵活:模拟电源(AVDD/AVSS)支持双极性 ±2.5 V 或单极性 5 V,数字电源(DVDD)2.25 V - 3.6 V,内置 1.8 V LDO 为数字核心供电,BYPAS 引脚需外接 1 µF 去耦电容;

- 环境耐受:工作温度 -40°C 至 +85°C,ESD 防护达 ±2000 V(HBM)/±500 V(CDM),符合工业级可靠性要求。

二、核心功能模块详解

(一)信号链架构

- 输入多路选择器(MUX) :支持外部输入或内部短路(通过 400 Ω 电阻接 VCOM 中点电压),内部短路模式可用于偏移校准与噪声性能验证,MUX 配置通过寄存器 MUX [1:0] 控制;

- ΔΣ 调制器 :采用固有稳定的四阶 2+2 流水线架构,将量化噪声推至高频段,调制器采样频率(fMOD)在高分辨率模式为 fCLK/4,低功耗模式为 fCLK/8,需外部 2.5 V 基准电压(REFP/REFN 引脚);

- 数字滤波器 :由 sinc 滤波器、FIR 滤波器、IIR 高通滤波器(HPF)组成,支持多种滤波组合:

- sinc 滤波器:5 阶低通,抽取比 4 - 128 可调,决定基础数据率;

- FIR 滤波器:固定 32 倍抽取,支持线性 / 最小相位选择,通带纹波 ±0.003 dB,阻带衰减 135 dB,保障信号完整性;

- HPF:一阶 IIR 结构,截止频率 0.1 Hz - 10 Hz 可编程,可滤除直流与低频干扰。

(二)校准与同步控制

- 校准功能 :支持偏移校准(OFSCAL 命令)与增益校准(GANCAL 命令),通过 24 位偏移校准寄存器(OFC [2:0])和满量程校准寄存器(FSC [2:0])修正误差,校准后增益误差可降至 0.0005%;

- 同步模式 :

- 脉冲同步 :SYNC 引脚上升沿触发同步,重置滤波内存,需等待 63 个转换周期使数据稳定;

- 连续同步 :接收周期性同步时钟,仅当 SYNC 周期与数据率周期非整数倍时重新同步,适配多设备协同场景。

(三)接口与数据传输

- SPI 兼容接口 :4 线制(CS、SCLK、DIN、DOUT),支持两种数据读取模式:

- 连续读取(RDATAC) :DRDY 变低后直接读取 32 位数据(二进制补码,可截断为 24 位),无需重复发送命令;

- 命令读取(SDATAC) :需发送 RDATA 命令触发数据输出,适合需精准控制读取时机的场景;

- 数据完整性:DRDY 引脚低电平表示数据就绪,读取过程中需注意时序约束,避免数据被覆盖。

三、典型应用与设计要点

(一)目标应用场景

- 能源勘探与地震监测 :直接连接地震检波器,通过高分辨率模式采集微弱振动信号,支持被动地震数据采集节点;

- 工业精密测量 :适配便携式仪器、过程控制设备,低功耗模式可延长电池供电设备续航;

- 传感器信号采集 :支持 RTD、热电偶等低电平信号测量,PGA 增益调节适配不同传感器输出范围。

(二)硬件设计关键要点

- 电源去耦 :AVDD/AVSS 需并联 0.1 µF 陶瓷电容 + 10 µF 钽电容,DVDD 并联 0.1 µF 电容,所有电容贴近引脚放置,模拟地与数字地单点连接,减少噪声耦合;

- 输入滤波 :模拟输入端建议添加对称 RC 低通滤波器(电阻 100 Ω - 1 kΩ,电容 100 pF C0G 材质),抑制混叠干扰,同时匹配传感器输出阻抗;

- 时钟设计 :外部时钟(CLK 引脚)推荐 1.024 MHz 晶振或 MEMS 时钟源,时钟线远离模拟信号路径,避免引入抖动噪声,长距离布线需串联 50 Ω 匹配电阻。

四、封装与订购信息

- 封装规格 :采用 24 引脚 VQFN(RHF 封装),尺寸 5.0 mm×4.0 mm,暴露热焊盘需焊接至 PCB 以优化散热,热阻参数:结到环境(RθJA)30.2 °C/W,结到板(RθJB)8.5 °C/W;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

局部放电监测设备的核心内容与监测原理2025-12-11 417

-

ADS114S06B/ADS114S08B 技术文档核心内容总结2025-11-07 749

-

ADS1287D 产品核心信息总结2025-11-06 574

-

数智化光伏电站解决方案关注的核心内容2025-10-14 867

-

电缆隧道在线监测需要注意的核心内容2025-06-30 553

-

ADS1287低功耗、1000SPS、宽带宽模数转换器数据表2024-07-23 554

-

嵌入式系统核心内容的Embedded GUI技术Microwindows2019-04-12 1613

-

ADS1287高分辨率模数转换器的详细英文手册2018-05-10 1731

-

单片机学习的八大主要核心内容分析2017-09-08 1029

全部0条评论

快来发表一下你的评论吧 !