ADC32RF42 技术文档核心总结

描述

ADC32RF42器件是一款 14 位、1.5GSPS、双通道模数转换器 (ADC),支持输入频率高达 4 GHz 及以上的射频采样。该ADC32RF42专为高信噪比 (SNR) 而设计,可提供 –151.8 dBFS/Hz 的噪声频谱密度,并在较大的输入频率范围内提供动态范围和信道隔离。带有片内端接的缓冲模拟输入可在较宽的频率范围内提供均匀的输入阻抗,并最大限度地减少采样保持毛刺能量。

*附件:adc32rf42.pdf

每个ADC通道可以连接到一个双频数字下变频器(DDC),每个DDC最多三个独立的16位数控振荡器(NCO),用于相位相干跳频。此外,ADC还配备了前端峰值和RMS功率检测器和报警功能,以支持外部自动增益控制(AGC)算法。

该ADC32RF42支持具有基于子类 1 的确定性延迟的JESD204B串行接口,使用高达 12.5 Gbps 的数据速率,每个 ADC 最多有 4 个通道。该器件采用 72 引脚 VQFN 封装(10 mm × 10 mm),支持工业温度范围(–40°C 至 +85°C)。

特性

- 14位、双通道、1.5GSPS ADC

- 本底噪声:–151.8 dBFS/Hz

- RF 输入支持高达 4 GHz

- 孔径抖动:90 f

S - 信道隔离度:95 dB(f

在= 1.8 吉赫 - 光谱性能 (f

在= 950 MHz,–2 dBFS):- 信噪比:61.1 dBFS

- SFDR:67dBc HD2、HD3

- 光谱性能 (f

在= 1.85 GHz,–2 dBFS):- 信噪比:58.9 dBFS

- SFDR:64dBc HD2、HD3

- 片内数字下变频器:

- 多达 4 个 DDC(双频模式)

- 每个 DDC 最多 3 个独立 NCO

- 片内输入箝位,用于过压保护

- 可编程片内功率检测器,带有报警引脚,支持 AGC

- 片上抖动

- 片内输入端接

- 输入满量程:1.35 V

聚丙烯 - 支持多芯片同步

- JESD204B接口:

- 基于子类 1 的确定性延迟

- 每通道 4 通道,高达 12.5 Gbps

- 功耗:2 W/Ch,1.5 GSPS

- 72引脚VQFN封装(10 mm×10 mm)

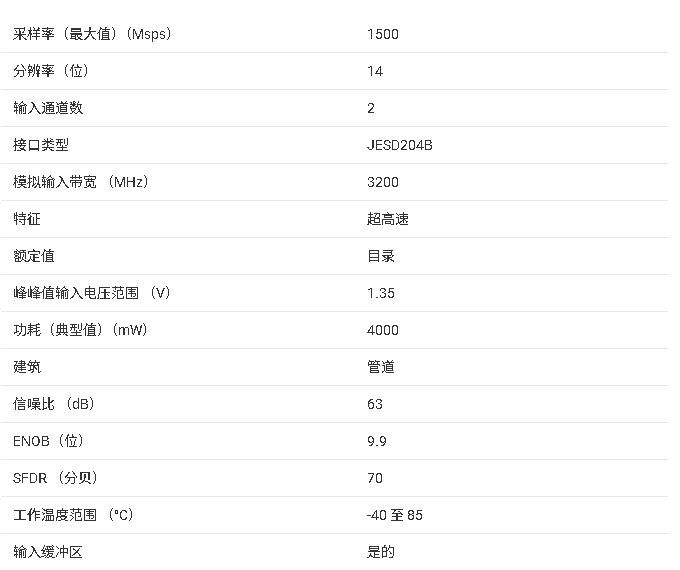

参数

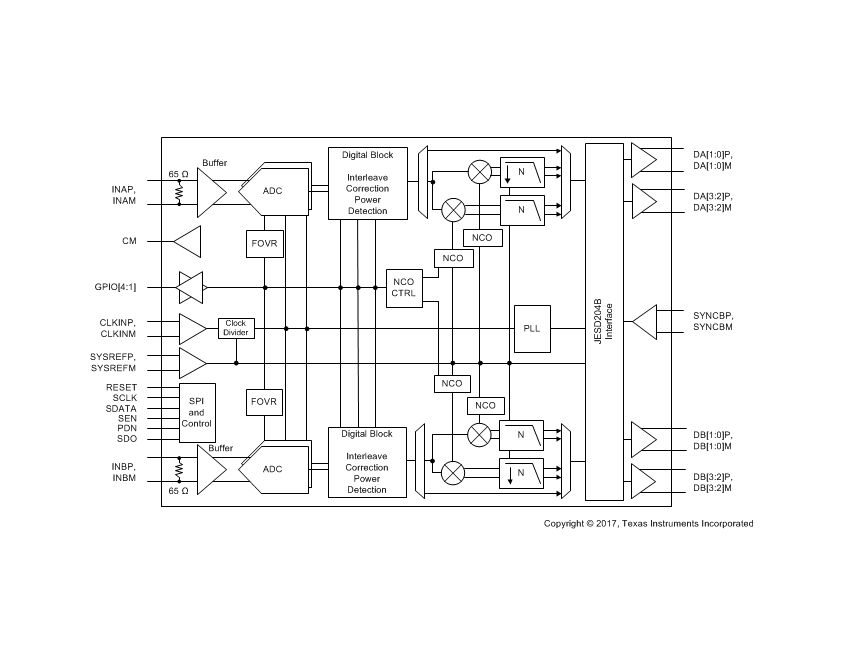

方框图

ADC32RF42 是德州仪器推出的 14 位双通道高速模数转换器(ADC),采样率达 1.5 GSPS,支持最高 4 GHz 射频输入,集成数字下变频器(DDC)与 JESD204B 接口,专为高动态范围宽带接收场景设计,适配蜂窝通信、相控阵雷达、电子战等应用。

一、核心基础信息

(一)核心定位与关键参数

- 分辨率与采样率:14 位无失码,单 / 双通道可选,最大采样率 1.5 GSPS,输入全量程 1.35 VPP。

- 关键性能:噪声基底低至 -151.8 dBFS/Hz,孔径抖动仅 90 fS;950 MHz 输入时 SNR 达 61.1 dBFS、SFDR 67 dBc,1.85 GHz 输入时 SNR 58.9 dBFS、SFDR 64 dBc;通道隔离度在 1.8 GHz 时达 95 dB。

- 工作环境:工业级温度范围 -40°C 至 85°C,结温最高 125°C;ESD 防护 ±1000 V(HBM)/±500 V(CDM)。

(二)封装与引脚

- 封装类型:72 引脚 VQFN(RMP 封装),尺寸 10 mm×10 mm,含热焊盘(需焊接至 PCB 地平面优化散热)。

- 引脚功能:包含双路差分模拟输入(INAP/INAM、INBP/INBM)、时钟输入(CLKINP/CLKINM)、JESD204B 数据输出(DA [3:0]、DB [3:0])、SPI 控制引脚(SCLK/SDIN/SEN/SDOUT)及 4 路 GPIO,支持多芯片同步的 SYSREF 和 SYNCB 引脚。

二、核心特性与功能模块

(一)模拟前端与信号处理

- 输入特性:内置 100 Ω 差分终端,输入阻抗 65 Ω、电容 2 pF,模拟带宽达 3.2 GHz;集成输入钳位电路,提供过压保护,最大限制 2.4 VPP 输入。

- 时钟与同步:支持 750 MHz-1.5 GHz 差分时钟输入,占空比 45%-55%;SYSREF 信号用于多芯片同步与内部时序校准,支持可编程延迟调整。

(二)数字下变频器(DDC)

- 工作模式:支持单 / 双波段接收,双波段模式下每通道最多 4 个 DDC,每 DDC 含 3 个独立 16 位数控振荡器(NCO),支持相位相干跳频。

- decimation 滤波:提供 4/6/8/9/10/12/16 倍复数抽取,阻带抑制约 90 dB,通带带宽约 80%,可灵活调整输出数据率。

(三)接口与控制

- JESD204B 接口:支持 Subclass 1 确定性延迟,每通道最多 4 路 lanes,单 lane 速率最高 12.5 Gbps,支持 8b/10b 编码与扰码。

- 控制接口:SPI 接口(支持 3 线 / 4 线模式)用于配置寄存器,4 路 GPIO 可配置为 NCO 控制、功率检测告警或过范围指示。

- 功率检测:集成峰值、RMS、交叉检测器,支持自动增益控制(AGC),可通过寄存器设置阈值与滞回特性。

(四)电源与功耗

- 供电需求:模拟电源 AVDD19(1.8-2.0 V)、AVDD(1.1-1.25 V),数字电源 DVDD(1.1-1.2 V);双通道 1.5 GSPS 工作时功耗约 4.03-6.95 W,单通道工作时约 2.66 W,全局掉电模式功耗 360 mW。

三、应用场景与设计要点

(一)典型应用

- 多模蜂窝接收机(2G/3G/4G)、相控阵雷达、电子战设备、宽带无线通信、高速数字化仪、通信测试仪器、毫米波接收机。

(二)设计关键要点

- 电源与去耦:各电源引脚需就近放置 0.1 µF 陶瓷电容 + 10 µF 钽电容去耦,模拟地与数字地单点连接,减少噪声耦合。

- 时钟设计:推荐使用低相噪时钟源,时钟路径需阻抗匹配,可添加带通滤波器降低外部抖动影响。

- 布局要求:模拟输入与数字输出分区域布线,避免平行走线;JESD204B 差分线对长度匹配,减少 skew;热焊盘充分散热,输入线路短且对称。

- 同步配置:多芯片同步时需通过 SYSREF 信号校准时序,JESD204B 接口需配置 LMFS 参数与帧格式,确保确定性延迟。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC12D1000RF 12 位高采样率 RF 采样 ADC 技术文档总结2025-11-18 1129

-

ADC32RF8x 系列产品核心信息总结2025-11-10 789

-

ADC32RF44 技术文档核心总结2025-11-07 820

-

ADC32RF82 产品核心信息总结2025-11-06 612

-

ADC3541技术文档总结2025-10-30 999

-

ADC32RF5x 系列技术文档总结2025-10-29 770

-

ADC32RF54双通道 14 位高速 RF 采样 ADC 技术总结2025-10-28 1091

-

ADC34RF55 技术文档总结2025-10-27 966

-

ADC32RF42在FPGA端无法采集到数据是怎么回事?2024-12-10 372

-

请问通过ADC32RF42 EVM GUI能直接配置出lmk04828的14路时钟吗?2024-11-22 333

-

将ADC32RF42 EVM与xilinx ZC706开发板直接相连,JESD204B时钟无法建链成功,为什么?2024-11-20 442

-

ADC32RF42双通道14位1.5GSPS模数转换器数据表2024-07-22 590

-

ADC12J4000EVM 评估模块的产品介绍2020-12-14 1207

全部0条评论

快来发表一下你的评论吧 !