根据JESD204B标准设计了高速串行接口发送端控制层电路

电子说

描述

高性能数据转换器是第五代移动通信基站系统的核心器件,其采样速率不低于3 GS/s、分辨率高于12 bit,因此高速串行接口取代传统接口电路成为必然趋势。基于JESD204B协议设计了一种应用于3 GS/s 12 bit ADCs的高速串行接口控制层电路。在保证高速传输的前提下,折中考虑功耗和资源,该电路在传输层采用预分频技术完成组帧;在数据链路层采用极性信息简化编码技术实现8 B/10 B编码。在Vivado 16.1环境下,采用Xilinx公司的ZC706 FPGA中PHY IP和JESD204B Receiver IP完成控制层接口电路的验证。实验结果表明数据传输正确,且串化后的传输速度达到7.5 Gb/s,相较于同类型的接口设计,其传输速度提高了50%。

0 引言

在第五代移动通信中,高性能A/D、D/A转换器是其发展的核心器件。因此,随着转换器分辨率和采样速率的提高,多路并行数据传输不仅增加芯片的引脚设计,还增加板级布线和系统互联的硬件开销,直接增加系统成本。而且当数据速率超过1 Gb/s时,低电压差分信号(Low-Voltage Differential Signaling,LVDS)技术难以满足转换器带宽的需要。因此,用于数据转换器的高速串行接口正在形成一种趋势,以支持更高速转换器、灵活的时钟以及确定性延迟等日渐严苛的要求[1]。

JESD204B针对高速数据转换器的串行数据接口,不仅可以克服LVDS并行数据传输带来的性能下降,同时最高可支持12.5 Gb/s,比LVDS吞吐量提高10倍,降低I/O需求及封装尺寸,降低静态功耗和节省系统成本。

目前,主流的高速高精度数据转换器芯片均采用JESD204B接口,如ADI近期发布的14 bit 2.6 GS/s双通道模数转换器AD9689和TI推出的12 bit 8 GS/s射频模数采样芯片ADC12J4000[2]等。国内相关技术虽然落后于国外,但各高校和科研机构针对不同的应用均做了相关研究,并取得了一定的进展。本文根据JESD204B标准设计了高速串行接口发送端控制层电路,主要包括传输层、数据链路层。通过搭建的硬件仿真平台,验证了控制层电路的正确性,并且其性能也很理想。

1 JESD204B标准概述

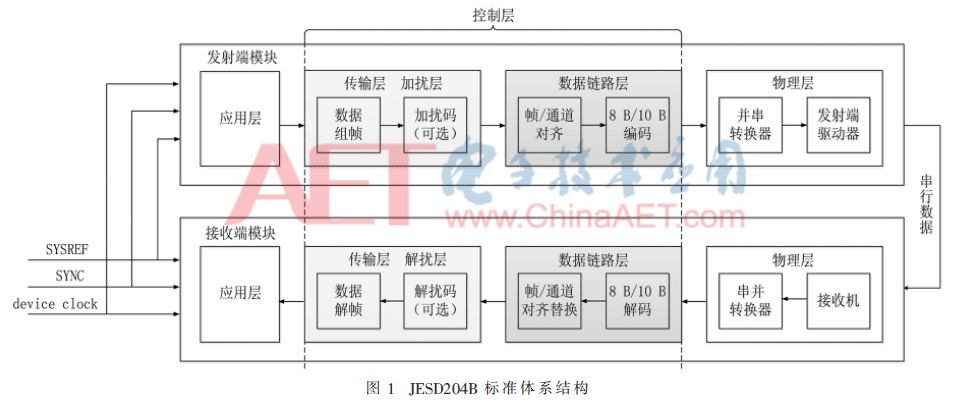

JESD204B是一种数模转换器通过串行接口链路连接后端数字信号处理设备的标准。该标准的体系结构可分为应用层、传输层、链路层和物理层,在功能上可将接收接口作为发送接口的逆过程。应用层是负责JESD204B链路配置和数据映射。传输层主要是用户根据数据格式的配置来对数据结构重新打包,以便映射为8位字节。加扰层为可选择模块,主要通过对8位字节的加解扰来扩展频谱,从而减少电磁干扰效应。数据链路层主要实现同步字符的产生、多帧同步、链路对齐、链路同步等用于通道对准监控和维护的操作,以及8 B/10 B编解码。物理层用于支持高速串行数据的发送与接收、串行与并行之间的转换。其结构如图1所示。

2 发送端控制层电路的设计与实现

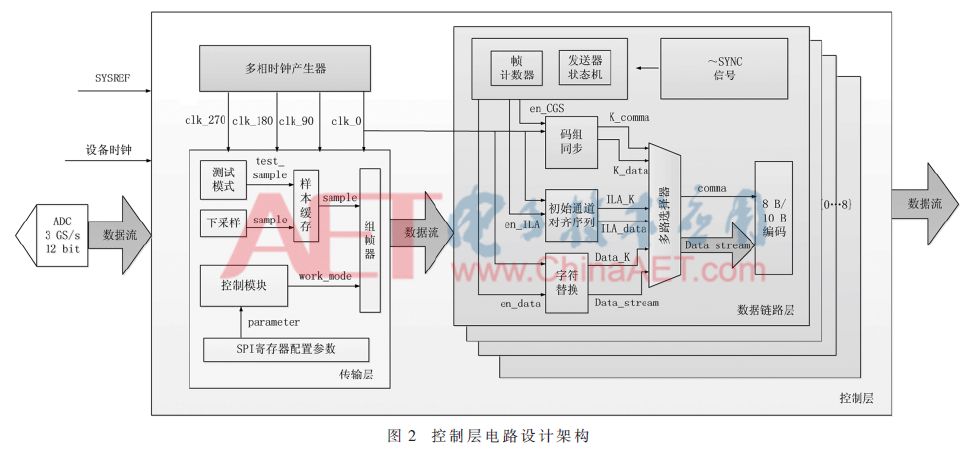

根据3 GS/s 12 bit高速高精度A/D转换器以及JESD204B标准中子类1工作模式的要求,搭建了一个完整的发送端控制层电路框架,如图2所示。本文设计的电路主要包括3个模块:传输层模块、数据链路层模块和8 B/10 B编码器模块。首先根据转换器数量M=4和样本数S=4,将ADC过来的3 GS/s 12 bit数据送入传输层,然后对其降频后通过读取串行外设接口(Serial Parallel Interface,SPI)发送过来的配置信息来添加控制字符和尾字符的方式把数据打包成通道数L=8的并行数组;之后把每个通道的32 bit数据送入数据链路层,通过码组同步(Code Group Synchronization,CGS)、初始通道对齐序列(Initial Lane Alignment Sequence,ILAS)阶段和字符替换来实现同步字符的产生、多帧同步、链路对齐与同步等操作;最后把数据送入8 B/10 B编码模块来完成控制层接口的数据传输。

2.1 传输层模块设计

传输层对于发送端控制层接口来说,是整个电路模块设计的开始,它主要通过添加控制字符和尾字符把接收的3 GS/s 12 bit ADC数据打包成8位并行数组。由于从ADC过来的数据速率很高,并且考虑在FPGA板上可实现的最高频率问题,因此在传输层的第一级将其转换为4路并行的750 MS/s 12 bit的ADCs,并利用多相时钟产生器对每一路数据进行下采样,产生4相、相位间隔90°的187.5 MHz的采样时钟。然后根据SPI寄存器配置参数来进行合理的数据映射,即把多位样本数据转换成一系列非扰码的8位字节。因此传输层总体电路结构可分为5个模块:下采样模块、样本缓存模块、SPI寄存器配置参数读取模块、模式控制模块和组帧器模块。

下采样模块是对数据进行S取4的采样,进而达到对整个系统降频的目的。样本缓存模块是对前面下采样模块的样本数据按由低到高依次先暂存在样本缓存器中,缓存空间大小定义为256 bit。图3为下采样模块送入样本缓存模块的数据组合格式,这样的组合也有益于组帧时数据的读取。SPI寄存器配置参数模块主要是读取SPI发送过来的配置信息,根据配置寄存器中定义的10 bit存储参数值,为模式控制模块提供组帧判断信息。模式控制模块是根据不同的配置参数组合对当前的工作模式进行判断。表1是根据项目需求提出的6种工作模式以及所支持的映射组帧参数。组帧器模块主要是根据模式控制模块的组帧模式信息,按照JESD204B标准的数据映射方法完成对样本缓存模块采样数据的组帧。这种映射方式有利于降低电路功耗,节省电路资源和减小电路面积。

2.2 数据链路层设计

数据链路层是整个发送端的关键组成部分。在数据链路层中,需要对传输层传输过来的数据进行初始化帧同步、初始化通道同步和字节产生替换来建立正确的传输通道,然后采用8 B/10 B方式对数据进行编码,并生成特殊控制符来实现通道对准监控和维护。同时,在设计该模块电路时要兼顾速度、面积和功耗等资源。所以,将数据链路层分为链路控制模块、CGS模块、ILAS模块、字符替换模块以及多路数据选择器模块。

2.2.1 链路控制模块

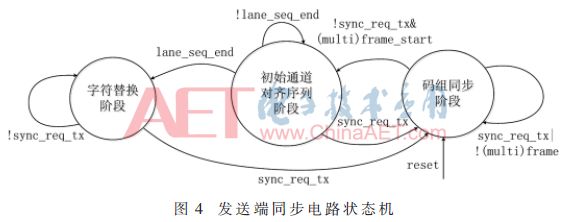

链路控制模块是对整个数据链路层的控制,主要负责在链路层初始化过程、同步维持过程和重同步过程中发送对应的数据和控制信号,方便其余模块根据其反馈信息进行调整,从而完成链路初始化到正常数据发送操作的过程,如图4所示的跳转机制。

首先,链路在复位结束或收到再同步请求时,进入到CGS阶段,不断发送规定的码组同步字符。若发现同步请求信号取消,状态机就会转移到ILAS阶段。ILAS阶段会将4个多帧序列发送完,然后发送相应的指示信号给状态机,表明已完成该序列并请求状态转移。控制模块接收到该信号有效后,将状态机转换到正常的数据发送阶段,并选择字符替换模块输出数据。

2.2.2 CGS模块

CGS阶段是链路层进行初始化操作的第一步。主要通过Comma码进行字符边界的检测,使得接收端在连续的串行数据流中检测出字符的边界。

具体实现过程是,当链路系统发生复位或者重同步时,接收端SYNC同步信号拉低置0,由此进入CGS阶段。在CGS阶段期间,发送端发射一系列连续的标志符/K28.5/(不少于F+9个/K28.5/字节,F为每帧的字节数目),接收端在收到至少4个连续/K28.5/字符,并对无序比特流定边界后就解除对发送端同步请求信号。发送端检测到同步请求解除后,在下一个本地多帧时钟上升沿停止发送/K28.5/字符,然后进入ILAS阶段。

2.2.3 ILAS模块

当系统完成CGS阶段之后,发送端紧接着就进入ILAS阶段。在ILAS阶段,一方面是为了发送链路配置数据,另一方面是完成帧以及多帧初始化同步。ILAS由4个多帧组成,这4个多帧均以/R/=/K28.0/控制字符开头,以/A/=/K28.3/控制字符结尾,中间为正常数据。这样可以让接收端通过/A/字符来完成多帧末尾的对齐。除此之外,第二个多帧的第二个8位字节是/Q/=/K28.4/控制字符,它标示着链路配置数据传输的开始,其中配置数据有14个字节。

2.2.4 字符替换模块

在JESD204B协议中,用码组同步和初始通道对齐序列来完成字节边界同步和多通道对齐。当系统完成了上述两个阶段后,在非扰码模式下传输层将用户数据直接发送到数据链路层的用户数据阶段。此时,要对数据进行同步字符替换,达到监控、校正和通道对准,从而建立在发送端与接收端正确的传输通道,提高传输的准确性。DATA字符替换模块遵循如下规则:

(1)当前帧的最后一个字节与多帧的最后一个字节不一致时,如果当前帧的最后一个字节和前一帧的最后一个字节相同时,发送端应该把当前帧的最后一个字节用控制字符/F/=/K28.7/进行替换。但如果前一帧的最后一个字节已经是特殊控制字符,则当前帧的最后一个字节不对其进行替换,保持原始数据的正常传输。

(2)当前帧的最后一个字节与多帧的最后一个字节一致时,如果当前帧的最后一个字节和前一帧的最后一个字节相同时,发送端应该把当前帧的最后一个字节用控制字符/A/=/K28.3/进行替换。与规则1不同的是,即使前一帧已经用特殊控制字符替换过了,也应该对原始数据进行替换。

2.2.5 8 B/10 B编码模块

8 B/10 B编解码最早由IBM公司提出,早期的查表法虽然实现起来较简单,但其速率、面积和功耗等资源方面受到了很大的限制。为了满足JESD204B协议接口,本文采用极性信息简化编码表对8 B/10 B编码进行实现。

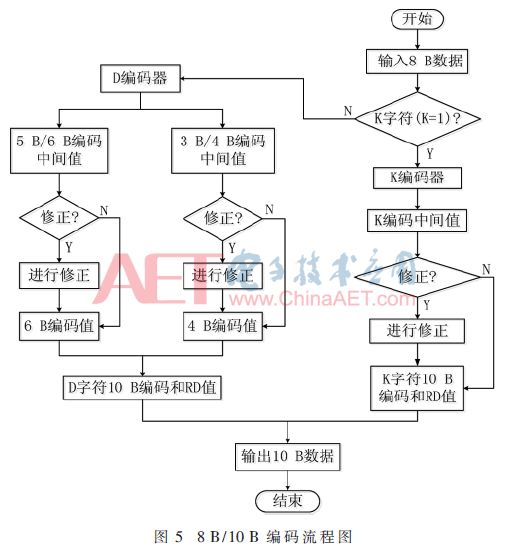

对于新型8 B/10 B编码来说,它主要是在保证DC平衡和转换密度的情况下,利用3 B/4 B和5 B/6 B并行编码来提升电路工作频率。同时还采用一些特殊控制符来进行误码监测。本文就是基于这样的设计将编码电路分为K字符编码器模块和D字符编码器模块,其中K字符编码器模块采用直接编码的方法,而D字符编码器模块分为5 B/6 B编码和3 B/4 B编码。首先进行K字符编码和D字符编码的选择,并且进行对应的初步编码;然后对所对应的编码进行修正,最后进行选择性输出。其相关的主要编码流程如图5所示。

3 仿真与验证

3.1 验证方法

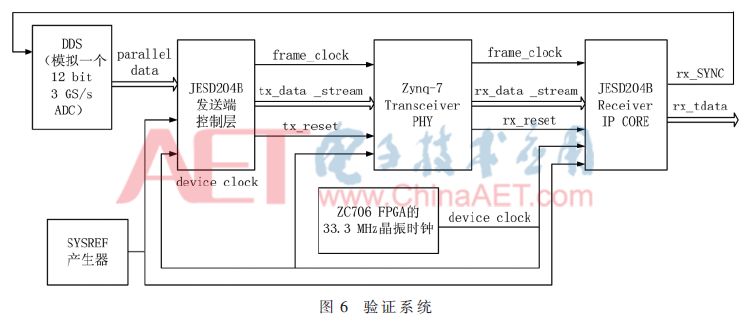

本文采用Modelsim 10.1软件完成了JESD204B发送端控制层电路的前端仿真验证。采用Vivado 16.1软件和Zynq-7000系列芯片XC7Z045FFG900-2 FPGA中的JESD204B PHY IP和Receiver IP[11]搭建硬件仿真验证平台,把控制层输出的并行数据发送给PHY IP,经过串化等一系列操作送给JESD204B Receiver IP,最后通过用ILA核抓取数据传输的实时波形图和对比发送、接收的数据,来实现硬件仿真验证,如图6所示。

3.2 验证结果

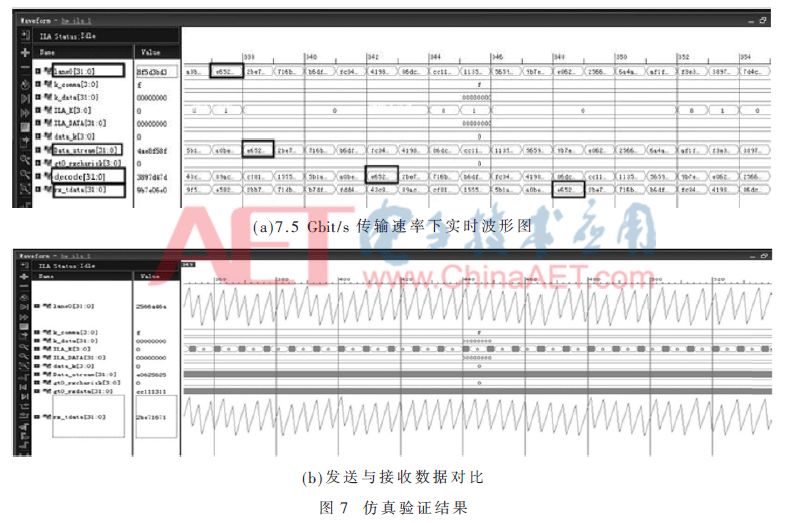

用Vivado16.1将功能仿真正确的RTL级代码综合后的电路烧写到ZC706开发板上,并使用ILA核抓取信号的实时波形进行分析。图7(a)和图7(b)是链路建立后用户数据传输的实时波形截图,在经过传输层输出32 bit数据、链路层用户数据、8 B/10 B编解码和JESD204B Receiver IP输出的32 bit数据后,对比发现发送和接收的数据无错码,即验证了发送端控制层电路数据传输的正确性。

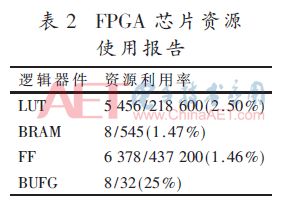

本文设计电路占用的FPGA资源如表2所示。除此之外,整个发送端控制层电路的功耗为0.467 W,建立时间的slack为0.235 ns,保持时间的slack为0.068 ns,并且经过IP串化后的位速率达到7.5 Gb/s。

4 结论

随着转换器分辨率和速度不断提高,JESD204B串行接口电路成为高速高精度数据转换器的标准接口。本文根据JESD204B标准设计了应用于3 GS/s 12 bit ADC发送端控制层接口,在满足速率的前提下,采用预分频技术和极性信息简化编码技术实现功耗和资源优化,并采用Xilinx公司的Zynq-7000系列芯片XC7Z045FFG900-2 FPGA验证系统,完成了硬件仿真验证,串化后的位速率可以达到7.5 Gb/s,相较于同类型的接口设计,其传输速度提高了50%。

-

JESD204B接口标准信息理解2018-09-13 0

-

JESD204B的系统级优势2018-09-18 0

-

在Xilinx FPGA上快速实现JESD204B2018-10-16 0

-

基于高速串行数字技术的JESD204B链路延时设计2018-11-21 0

-

串行LVDS和JESD204B的对比2019-05-29 0

-

JESD204B串行接口时钟的优势2019-06-19 0

-

FPGA高速数据采集设计之JESD204B接口应用场景2019-12-03 0

-

如何让JESD204B在FPGA上工作?FPGA对于JESD204B需要多少速度?2021-04-06 0

-

一文读懂JESD204B标准系统2021-05-24 0

-

JESD204B协议介绍2022-11-21 0

-

JESD204B的优势2022-11-23 0

-

JESD204B标准及演进历程2017-11-18 14491

-

针对高速数据转换器的最新高速JESD204B标准带来了验证挑战2017-11-18 3293

-

JESD204B使用说明2024-12-18 1232

全部0条评论

快来发表一下你的评论吧 !