半导体“HBM和3D Stacked Memory”技术的详解

半导体“HBM和3D Stacked Memory”技术的详解

描述

【博主简介】本人“爱在七夕时”,系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵。当前在各网络平台上均以此昵称为ID跟大家一起交流学习!

相信一聊到HBM DRAM(高带宽内存)和3D Stacked Memory(3D堆叠内存),大家都会有同样一个疑问:它们之间有什么关系?为什么很多的时候这两者会同时出现?......其实,具体来讲:HBM是3D Stacked的核心技术分支与典型代表,二者是“具体技术实例”与“广义技术类别”的关系——HBM是3D Stacked技术在高性能计算场景下的核心落地形态,而3D Stacked是HBM实现性能突破的关键技术基础。

简言之:3D Stacked Memory是“技术方法”,而HBM是“用这种方法解决特定问题的产品”。

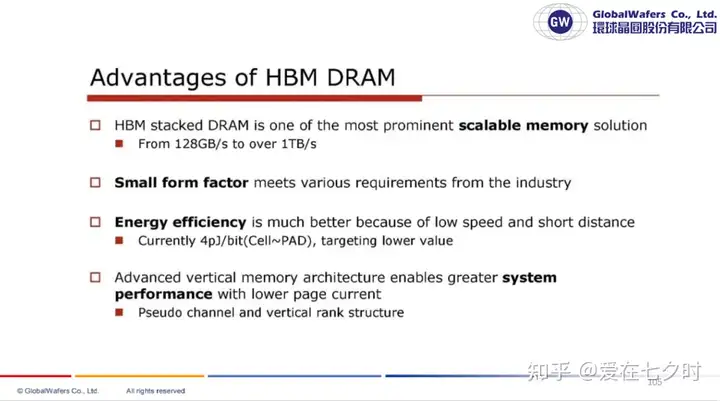

同时,HBM也是3D Stacked Memory在高性能计算场景下的具体实现,其3D堆叠架构解决了传统内存的“带宽瓶颈”与“功耗问题”,是AI、HPC等前沿领域的核心支撑技术。未来随着HBM3D、定制化HBM的发展,其在存储产业的地位将进一步提升。

关于HBM的部分,我曾在之前的章节中有详细介绍过,这里就不过多赘述了,有兴趣的朋友可以一起探讨。所以,本章节想要跟大家分享的还是HBM DRAM(高带宽内存)和3D Stacked Memory(3D堆叠内存)技术相关的内容。

一、HBM DRAM和3D Stacked Memory技术的简介

1、HBM DRAM(高带宽内存)

以下是关于HBM技术详解介绍:

半导体“高带宽内存(HBM)”芯片技术的详解;

2、3D Stacked Memory(3D堆叠内存)

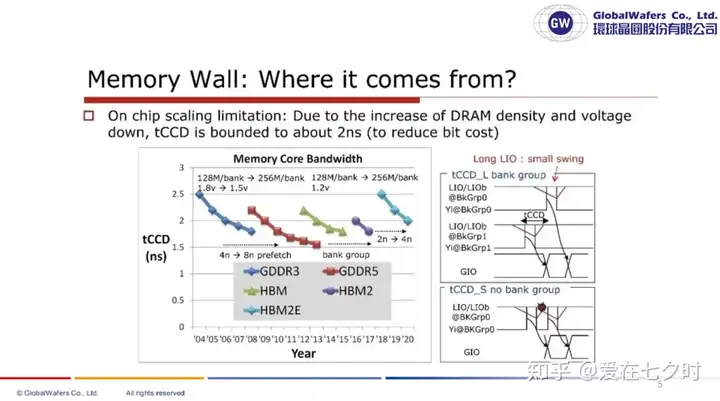

3D堆叠内存,英文全称:3D Stacked Memory,3D堆叠内存芯片则是通过3D封装技术,将多层DRAM堆叠而成的新型内存。3D堆叠内存芯片能提供很大的内存容量和内存带宽,其中混合内存立方体(Hybrid Memory Cube)和高带宽内存(High Bandwidth Memory)是两种新型的3D堆叠内存技术。利用3D堆叠内存,可以进行许多PIM设计,比如改变整个系统,或者实现简单的功能卸载,主要思想是将某种形式的处理逻辑(通常是加速器、简单内核或可重构逻辑)放在3D堆叠内存的逻辑层中。取决于体系结构的设计,这个PM处理逻辑(PIM核心或PIM引擎)可以执行应用程序的一部分(从单个指令到函数)或整个线程和应用程序。本节将讨论利用3D堆叠内存的PM在图处理、移动设备、图形处理单元上的使用。

说白了,3D DRAM就是一种通过堆叠多个存储层和使用垂直互联技术来增加存储密度和性能的先进DRAM的技术。3D DRAM能够提供更高的存储密度、更低的功耗和更高的带宽,适用于高性能计算、数据中心和AI等应用场景。

(1)3D DRAM的结构

3D DRAM与传统的2D DRAM相比,采用了垂直堆叠的结构。传统的2D DRAM将存储单元横向排布在单个硅基晶圆平面上,而3D DRAM通过将多个存储层垂直堆叠在一起,以形成更高的存储密度。

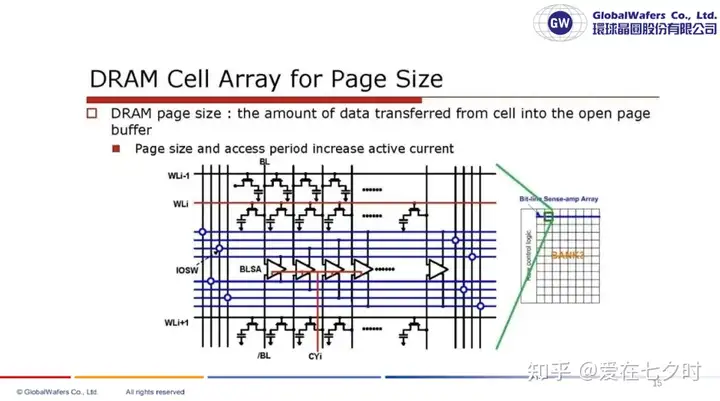

a.堆叠结构

3D DRAM的结构由多个DRAM层组成,每一层都包含大量的存储单元。每一层中的存储单元按照行和列的方式排列,类似于传统DRAM的平面排列方式。

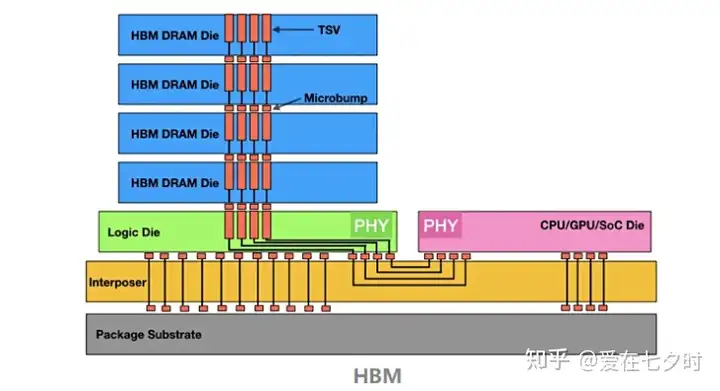

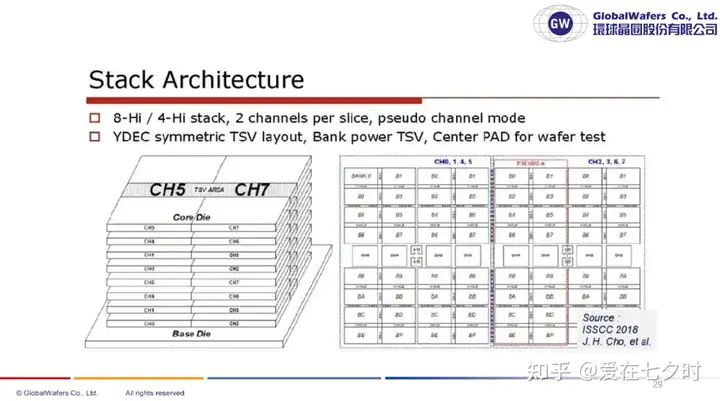

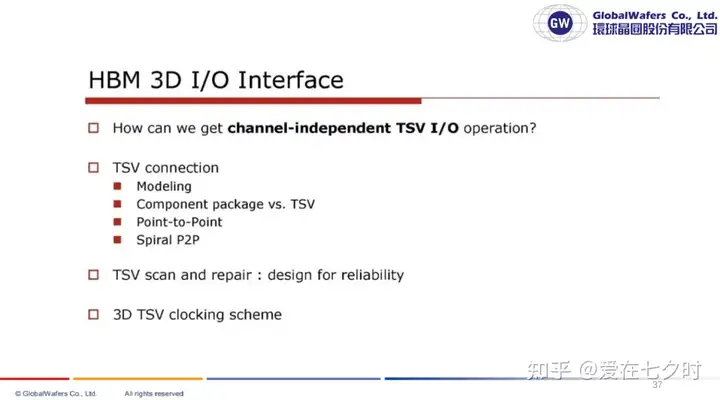

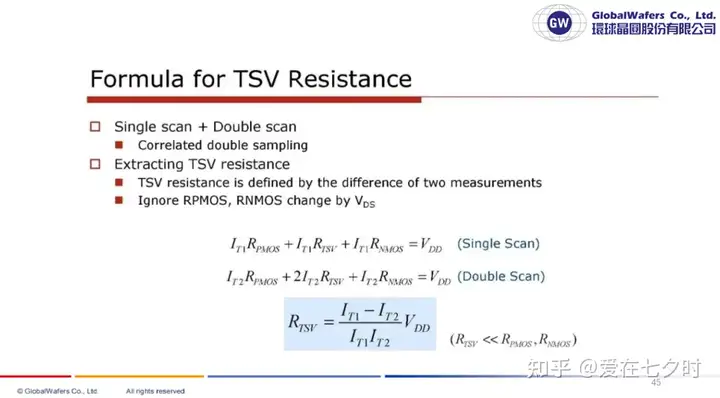

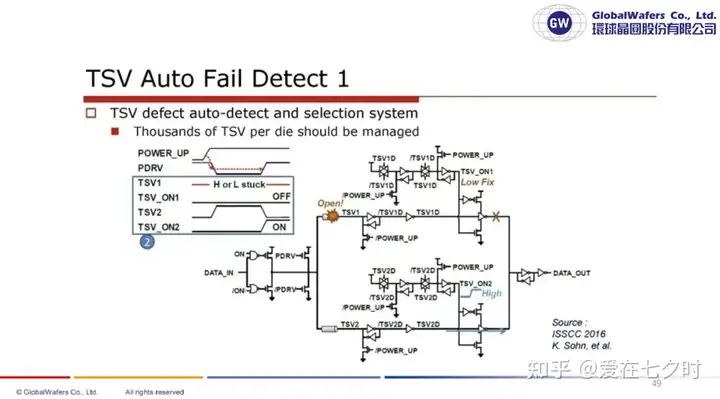

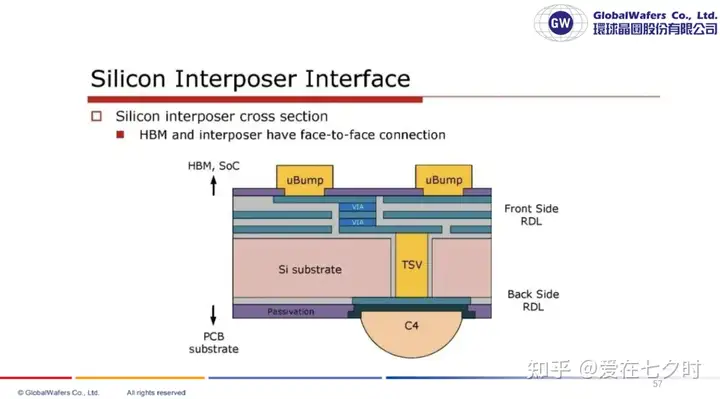

b.垂直互联(Through-Silicon Via, TSV)

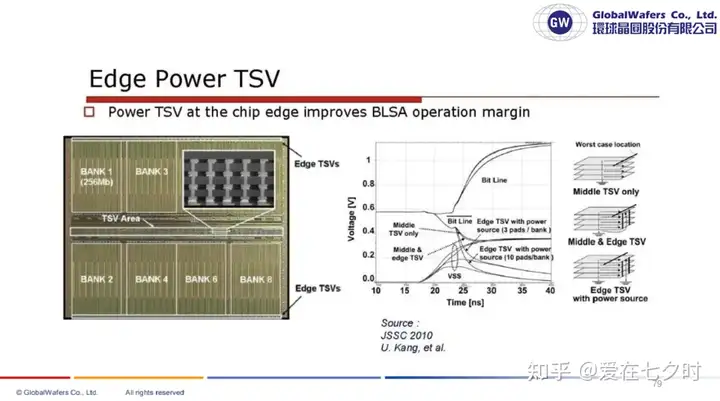

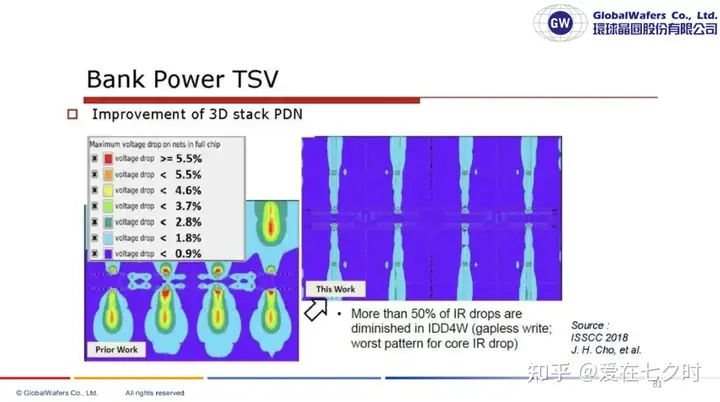

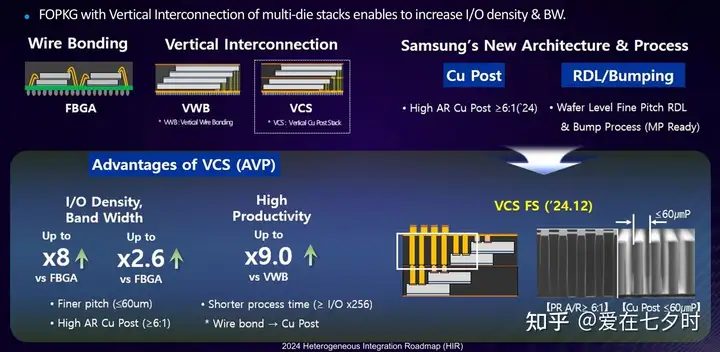

垂直互联技术在3D DRAM中至关重要,它通过在晶圆中穿孔并填充导电材料来连接不同的存储层。TSV技术可以显著减少信号传输路径,降低延迟并提高数据传输速率。

(2)3D DRAM的制程技术

3D DRAM的制程技术比2D DRAM更复杂,涉及到多层堆叠、热处理、垂直互联的形成和各层之间的电气隔离。

a.晶圆级堆叠

3D DRAM制造过程中,首先在多个晶圆上分别制造出DRAM存储单元,然后通过晶圆粘合技术将这些晶圆堆叠在一起。

b.TSV制造和填充

通过刻蚀和化学机械抛光(CMP)工艺,形成垂直穿孔,随后在这些孔中填充铜或钨等导电材料以形成垂直互连。

c.热处理和电气隔离

由于多个晶圆堆叠在一起,热处理工艺和电气隔离至关重要。需要确保各层之间的热应力和电荷干扰被最小化。

(3)3D DRAM的优势

3D DRAM相较于传统的2D DRAM,具有许多显著的技术优势:

a.更高的存储密度

由于采用垂直堆叠结构,3D DRAM可以在相同的平面面积上容纳更多的存储单元,从而显著提高存储密度。

b.更低的功耗

3D DRAM通过缩短信号传输路径,降低了数据访问的延迟和能量损耗,能够在较低的工作电压下实现更高的性能。

c.更高的带宽和更快的速度

由于TSV技术的应用,层与层之间的数据传输速度更快,带宽也更高,从而可以更好地支持高性能计算和数据中心应用。

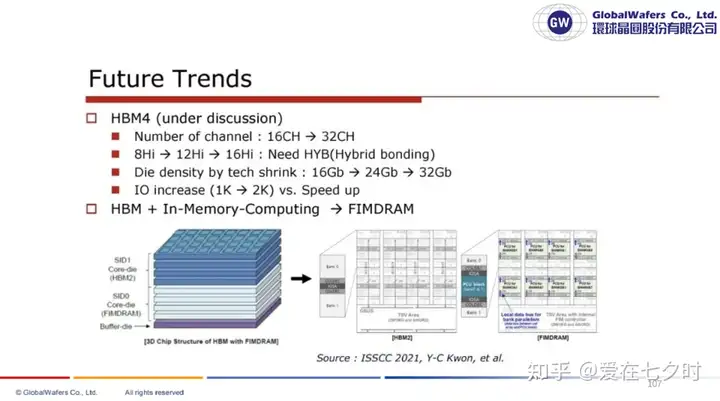

所以,未来,随着制程技术的进一步提升和对更高性能的需求增加,3D DRAM将继续朝着更高层数堆叠、更小的制程节点和更低功耗的方向发展。可能会引入新的材料和结构,如垂直晶体管技术(如Gate-All-Around FETs)以及更先进的封装方式(如Chiplet封装),以进一步提升3D DRAM的性能和应用广度。

二、HBM DRAM和3D Stacked Memory技术之间的关系

因为HBM与3D Stacked Memory是“具体技术实例”与“广义技术类别”的关系,所以想要讲清楚这两者之间的具体关系,得从以下三个方面说起:

1、HBM是3D Stacked Memory的核心技术与典型应用

3D堆叠内存是通过垂直堆叠多层存储芯片实现高带宽、大容量的广义内存技术类别;而HBM是其中专为AI、高性能计算(HPC)等超高性能场景优化的技术实例。

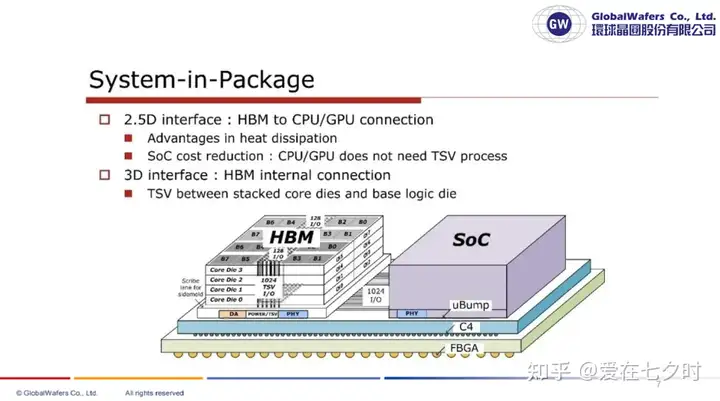

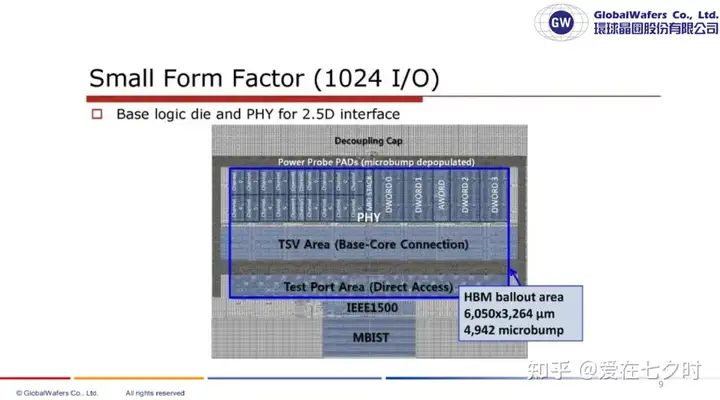

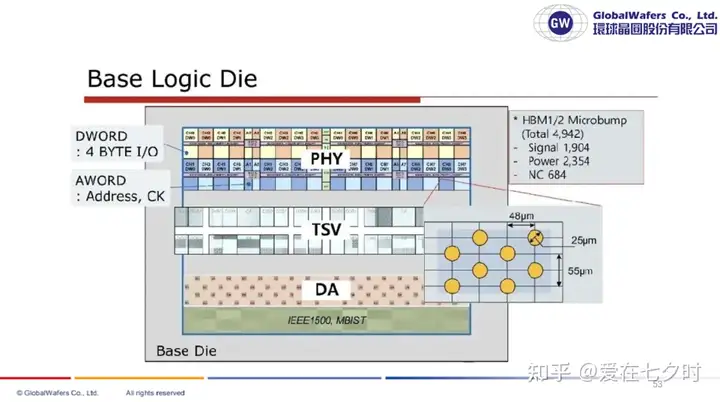

根据搜索结果,HBM的定义明确指向“3D堆叠DRAM”:它是将多个DRAM芯片(Core Die)通过**硅通孔(TSV)与微凸点(Microbump)**垂直堆叠,并与底层逻辑芯片(Base Die)封装在一起,形成“处理器-内存”紧耦合架构的新型内存。例如,HBM3E单封装容量可达24GB,带宽高达8Gbps/Pin,正是依托3D堆叠技术突破了传统内存的带宽瓶颈。

2、3D Stacked是HBM突破性能瓶颈的关键技术基础

HBM的核心优势(超高带宽、低功耗、小尺寸)完全依赖3D堆叠技术实现:

a.缩短数据传输距离

通过垂直堆叠DRAM芯片,数据无需在平面上长距离传输,而是“抄近道”在层间传递,大幅降低延迟;

b.提升位宽与带宽

HBM采用超宽I/O总线(如1024位、2048位),远高于传统GDDR5的32位,结合多层堆叠,带宽可达传统内存的5-10倍;

c.降低功耗

短距离传输与高带宽特性,使HBM每瓦带宽比GDDR5高3倍以上,解决了高性能计算的“功耗墙”问题。

3、HBM与其他3D Stacked Memory的差异与定位

3D Stacked Memory是一个广义范畴,HBM与其他3D Stacked技术(如NAND、3D DRAM)的核心区别在于技术路径与应用场景:

a.与伪3D堆叠(如NAND)的区别

NAND是“多颗Die独立连接基板”的伪3D堆叠,层数受限(≤8层)、成本较低,用于SSD等长期存储;而HBM是“多层Die通过TSV互连逻辑Die”的真3D堆叠,专注高性能缓存;

b.与3D DRAM的区别

3D DRAM侧重“存储单元的垂直化”(如三星的VS-CAT DRAM),是单元结构层面的创新;而HBM是“封装级的DRAM堆叠”,强调与处理器的紧耦合,两者形成互补。

三、HBM DRAM和3D Stacked Memory技术详解

以下内容就是本章节要跟大家分享的重点,希望有兴趣的朋友可以一起交流学习,具体分享内容如下:

因为本PPT章节太多,剩下部分如有朋友有需要,可私信我邀请您加入我“知识星球”免费下载PDF版本。注意:此资料只可供自己学习,不可传阅,平台有下载记录,切记!欢迎加入后一起交流学习。

四、HBM DRAM和3D Stacked Memory技术的应用

高带宽内存(HBM)作为3D堆叠内存的核心落地形态,与广义的3D堆叠内存(如3D DRAM、3D数字内存内计算(3DIMC))的应用场景高度重叠,均聚焦于高带宽、低功耗、高算力需求的领域。所以结合具体技术与产品,分场景说明两者的应用情况如下:

1、人工智能(AI)与机器学习:当前与未来的核心战场

AI模型(尤其是大型语言模型LLM、深度神经网络)对内存带宽与容量的需求呈指数级增长,HBM与3D堆叠内存成为突破“内存墙”的关键:

a.HBM的当前主流应用

HBM已成为AI GPU/TPU的“标配”,用于解决模型训练与推理中的数据搬运瓶颈。例如:

英伟达H100 GPU搭载HBM,带宽高达3TB/s,支撑大模型训练的高吞吐量需求;

AMD MI300 GPU集成HBM,用于生成式AI与高性能计算,性能较上一代提升数倍;

超级计算机如富士通A64FX,通过HBM实现高速数据交互,支撑气候模拟等复杂计算。

b.3D堆叠内存的未来潜力

针对LLM的大容量、低延迟需求,单片3D堆叠DRAM与3DIMC成为下一代解决方案:

单片3D堆叠DRAM:通过垂直位线(VBL)/字线(VWL)设计与异质集成,其加速器推理吞吐量可达NVIDIA H100的15倍,能效高55倍;

d-Matrix的3DIMC技术:将内存与计算深度集成,宣称AI推理速度比HBM快10倍、能耗降低90%,直接挑战HBM在AI推理中的地位。

2、高性能计算(HPC):提升系统算力密度

HPC场景(如科学计算、数据分析)需要处理海量数据,HBM与3D堆叠内存通过缩短数据传输路径提升系统效率:

a.HBM的应用

HBM常与高性能CPU/GPU结合,用于超级计算机的互连与存储。例如,日本理化学研究所(RIKEN)的Fugaku超级计算机,通过HBM实现节点间的高速数据传输,峰值性能达442 PFlops。

b.3D堆叠内存的补充

3D堆叠技术可提升存储密度,减少HPC系统的占地面积。例如,3D NAND闪存的堆叠架构已被用于HPC的辅助存储,未来或扩展至主存领域。

3、图形处理与消费电子:提升视觉体验

HBM的高带宽特性使其成为高端图形处理的理想选择,支撑高帧率游戏、4K/8K渲染等场景:

a.HBM的应用

高端显卡(如英伟达RTX 40系列、AMD Radeon 7000系列)搭载HBM2e/HBM,提升图形数据的传输速度,使游戏最低帧数较前一代提升25%以上。

b.3D堆叠内存的延伸

3D堆叠技术可用于消费级设备的存储与计算集成,例如将3D DRAM与图像处理器(ISP)结合,提升手机的图像处理速度与AI运算能力。

4、细分领域:传感器与专用芯片

3D堆叠内存的非易失性、高集成度特性,还被用于专用传感器芯片:

SPAD(单光子雪崩二极管)芯片:通过3D堆叠技术(如晶圆级混合键合),将像素阵列与逻辑电路垂直集成,提升光子探测效率(PDE)并降低暗计数率(DCR),用于自动驾驶的激光雷达、医疗成像等领域。

五、总结一下

说实话,要做HBM DRAM和3D Stacked Memory技术的总结还是挺难的,因为两者的关系比较特殊,在其终端的应用场景里,既有共性,也有差异,所以只能简单地分开总结吧:

1、共性方面

两者均聚焦于高带宽、低功耗需求,核心是解决“数据搬运慢、能耗高”的问题;

2、差异方面

HBM是当前AI/HPC的主流解决方案,强调“成熟量产”;3D堆叠内存(如3D DRAM、3DIMC)是未来方向,侧重“更高密度、更低延迟”,尤其在LLM与AI推理中潜力巨大。

随着AI模型的持续增大与算力需求的爆发,HBM与3D堆叠内存的应用将向更广泛的消费电子、边缘计算等领域渗透,成为未来计算系统的“内存基石”。

简而言之:HBM是3D堆叠内存的“现在时”,其他3D堆叠技术是“未来时”——两者协同推动内存性能边界,最终服务于不同场景的计算需求。

免责声明

【我们尊重原创,也注重分享。文中的文字、图片版权归原作者所有,转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时私信联系,我们将第一时间跟踪核实并作处理,谢谢!】

-

3D堆叠像素探测器芯片技术详解(72页PPT)2024-11-01 4679

-

三星将于今年内推出3D HBM芯片封装服务2024-06-19 1847

-

半导体2.5D/3D封装技术:趋势和创新2022-04-29 1090

-

SuperView W3光学3D表面轮廓仪助力半导体智能制造2022-03-21 2060

-

采用艾迈斯半导体的ASV技术有什么特点?2021-07-09 2351

-

AR0237IR图像传感器推动3D成像技术的发展2020-12-16 2002

-

新型2.5D和3D封装技术的挑战2020-06-16 8778

-

3D SiC技术闪耀全场,基本半导体参展PCIM Asia引关注2018-07-02 1299

-

半导体制冷的巧克力3D打印成型2018-03-07 1201

-

半导体产业的未来:3D堆叠封装技术2016-06-10 2825

-

Finfet技术(3D晶体管)详解2012-08-19 2920

-

多视角裸眼3D显示器技术发展和市场动态2012-08-17 1836

-

3D工艺成为半导体微细加工技术必然趋势2012-05-15 1385

-

半导体制程迈入3D 2013年为量产元年2011-12-28 1003

全部0条评论

快来发表一下你的评论吧 !