下拉电阻的作用原理

电子说

描述

下拉电阻

1、概念:将一个不确定的信号,通过一个电阻与地GND相连,固定在低电平;

2、下拉是从器件输出电流;拉电流;

3、当一个接有下拉电阻的IO端口设置为输入状态时,它的常态为低电平;

下拉电阻的作用

1、提高电压准位:

a、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

b、OC门电路必须加上拉电阻,以提高输出的搞电平值。

2、加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

3、N/A pin防静电、防干扰:在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗, 提供泄荷通路。同時管脚悬空就比较容易接受外界的电磁干扰。

4、电阻匹配,抑制反射波干扰:长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

5、预设空间状态/缺省电位:在一些 CMOS 输入端接上或下拉电阻是为了预设缺省电位。 当你不用这些引脚的时候, 这些输入端下拉接 0 或上拉接 1。在I2C总线等总线上,空闲时的状态是由上下拉电阻获得

6、提高芯片输入信号的噪声容限:输入端如果是高阻状态,或者高阻抗输入端处于悬空状态,此时需要加上拉或下拉,以免收到随机电平而影响电路工作。同样如果输出端处于被动状态,需要加上拉或下拉,如输出端仅仅是一个三极管的集电极。从而提高芯片输入信号的噪声容限增强抗干扰能力。

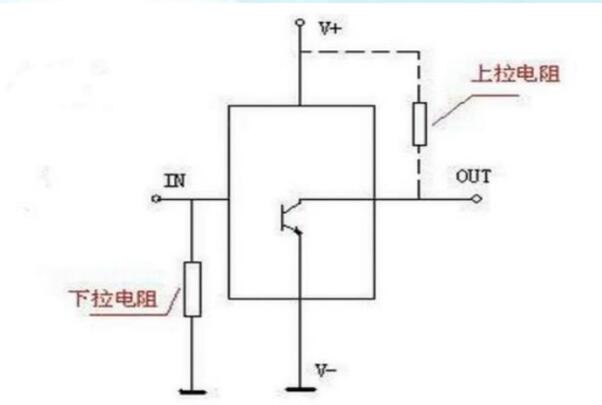

下拉电阻的原理图

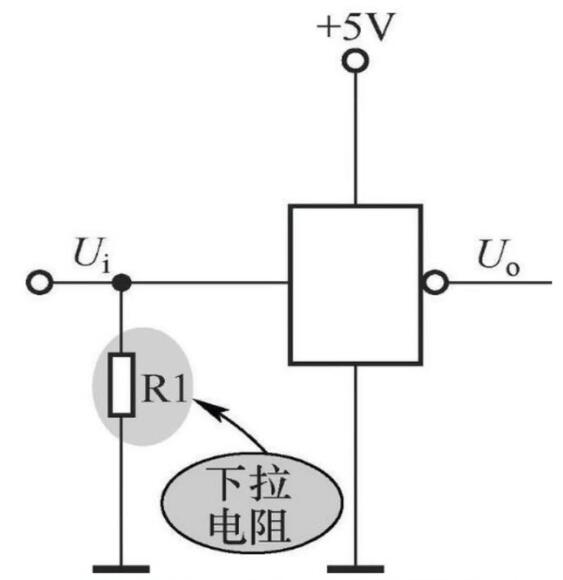

下拉电阻典型电路

图所示是下拉电阻电路。这是数字电路中的反相器,输入端Ui通过下拉电阻R1接地,这样在没有高电平输入时,可以使输入端稳定地处于低电平状态,防止了可能出现的高电平干扰使反相器误动作。

如果没有下拉电阻R1,反相器输入端悬空,为高阻抗,外界的高电平干扰很容易从输入端加入到反相器中,从而引起反相器朝输出低电平方向翻转的误动作。

在接入下拉电阻R1后,电源电压为5伏时,下拉电阻R1一般取值在100至470欧,由于R1阻值很小,所以将输入端的各种高电平干扰短接到地,达到抗干扰的目的。

下拉电阻选择

下拉电阻的设定的原则和上拉电阻是一样的。下拉电阻的选择应结合开关管特性和下级电路的输入特性进行设定,主要需要考虑以下几个因素:

1、驱动能力与功耗的平衡。以上拉电阻为例,一般地说,上拉电阻越小,驱动能力越强,但功耗越大,设计时应注意两者之间的均衡。

2、下级电路的驱动需求。同样以上拉电阻为例,当输出高电平时,开关管断开,上拉电阻应适当选择以能够向下级电路提供足够的电流。

3、高低电平的设定。不同电路的高低电平的门槛电平会有不同,电阻应适当设定以确保能输出正确的电平。以上拉电阻为例,当输出低电平时,开关管导通,上拉电阻和开关管导通电阻分压值应确保在零电平门槛之下。

4、频率特性。以上拉电阻为例,上拉电阻和开关管漏源级之间的电容和下级电路之间的输入电容会形成RC延迟,电阻越大,延迟越大。上拉电阻的设定应考虑电路在这方面的需求。

- 相关推荐

- 热点推荐

- 下拉电阻

-

三极管下拉电阻的作用是什么?2024-06-04 6972

-

下拉电阻的作用有哪些2024-05-02 3994

-

上拉电阻与下拉电阻的作用2023-06-07 4249

-

上拉电阻和下拉电阻的作用是什么?2023-05-26 4474

-

RS485接口电路上拉电阻和下拉电阻的作用是什么?2023-04-27 1166

-

上拉电阻和下拉电阻作用、区别和应用2023-04-21 18632

-

上拉电阻和下拉电阻原理及作用2023-03-17 7384

-

理解上拉电阻与下拉电阻的原理与作用2022-01-14 1786

-

上拉电阻和下拉电阻的作用及选择2016-12-15 1197

-

上拉下拉电阻作用总结 (2)2016-05-19 838

-

上下拉电阻的作用2015-04-18 26443

-

拉电阻、下拉电阻的原理和作用2014-11-17 5229

-

上拉、下拉电阻的作用2012-08-20 2090

全部0条评论

快来发表一下你的评论吧 !