半导体先进封装“重布线层(RDL)”工艺技术的详解;

半导体先进封装“重布线层(RDL)”工艺技术的详解;

描述

【博主简介】本人“爱在七夕时”,系一名半导体行业质量管理从业者,旨在业余时间不定期的分享半导体行业中的:产品质量、失效分析、可靠性分析和产品基础应用等相关知识。常言:真知不问出处,所分享的内容如有雷同或是不当之处,还请大家海涵。当前在各网络平台上均以此昵称为ID跟大家一起交流学习!

随着电子设备向更小型化、更高性能的方向发展,传统的芯片互连技术已经无法满足日益增长的需求。在这样的背景下,重布线层(RDL)工艺技术应运而生,因为与传统封装相比,当前先进封装技术凭借三大核心优势脱颖而出:显著提升芯片功能密度、大幅缩短互联距离、实现系统级重构。而这一技术飞跃的实现,很大程度上得益于重布线层(RDL)工艺技术的突破性应用,从而成为了先进封装技术中的核心之一。

封装中的重布线层(RDL)工艺是集成电路封装设计中的一个重要层次,主要用于实现芯片内电气连接的重新分配,并且在封装中起到连接芯片和外部引脚之间的桥梁作用。重布线层(RDL)的设计和实现直接影响到封装的电气性能、可靠性和制造成本。

一、重布线层(RDL)工艺技术的概述

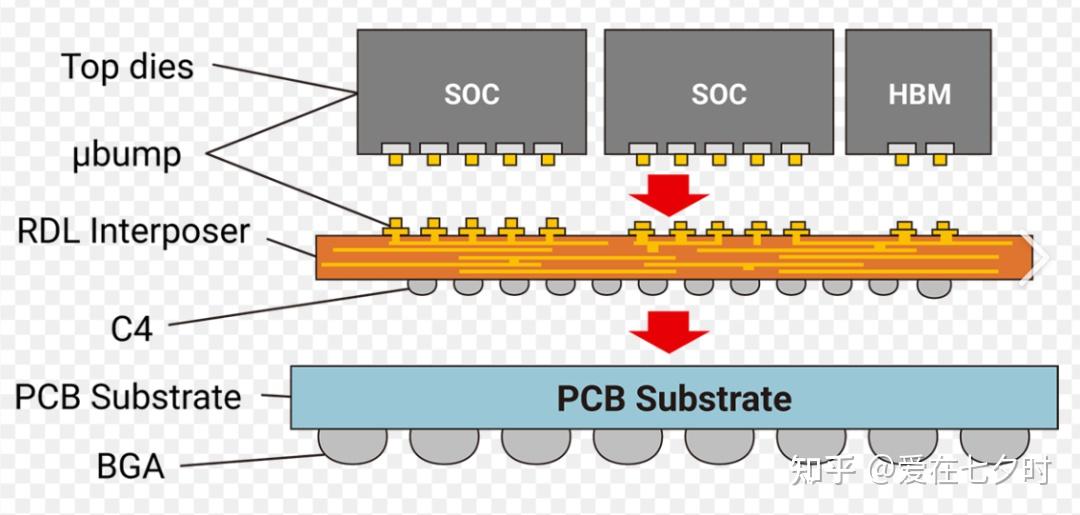

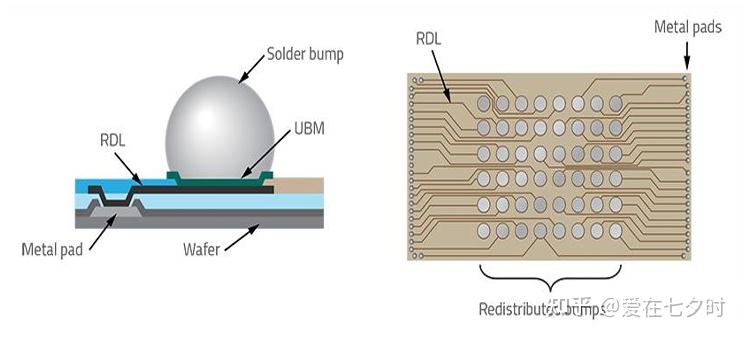

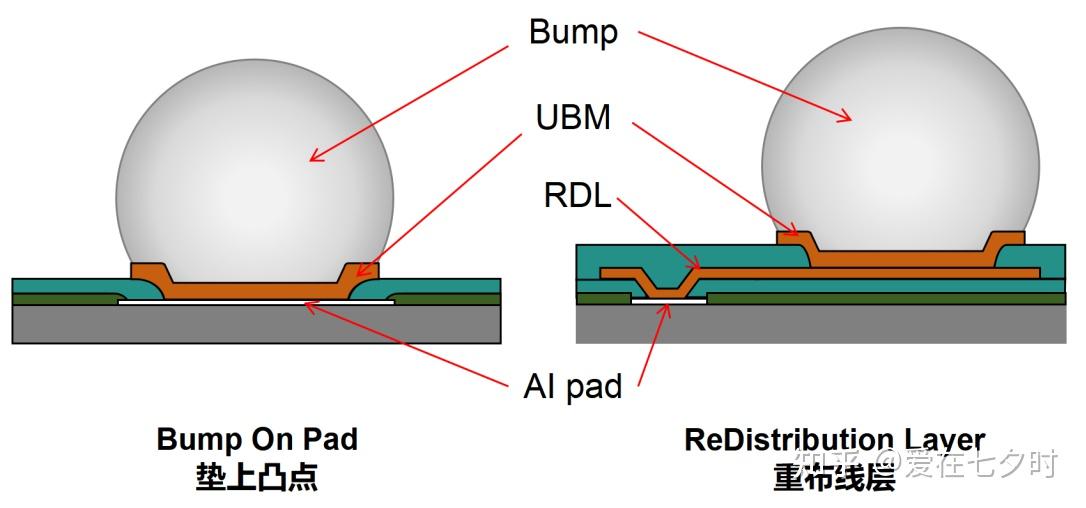

重布线层,英文全称:Re-Distribution Layer,简称:RDL。它是先进封装的关键互连工艺之一,其核心目的是将多个芯片集成到单个封装中。该工艺通过在介电层顶部创建图案化金属层,将IC的输入/输出(I/O)重新分配到新位置(通常位于芯片边缘),从而利用标准表面贴装技术(SMT)实现IC与印刷电路板(PCB)的高效连接。RDL技术不仅使设计人员能够以紧凑且高效的方式布局芯片,还能显著减少器件的整体占地面积,成为实现高密度异构集成的核心技术支撑。

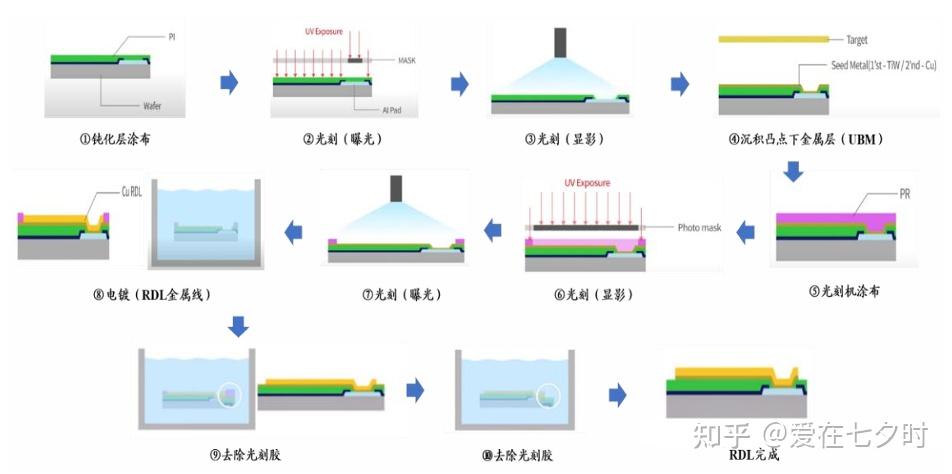

晶圆级金属重布线制程在IC上涂布一层绝缘保护层,再以曝光显影的方式定义新的导线图案,然后利用电镀技术制作新的金属线路,以连接原来的芯片引脚和新的凸点,达到芯片引脚重新分布的目的。重布线层的金属线路以电镀铜材料为主,根据需要也可以在铜线路上镀镍金或者镍钯金材料,相关核心材料包括光刻胶、电镀液、靶材、刻蚀液等。

二、IC输入/输出(I/O)数量的介绍

业内人都知道:想要在微缩化的芯片世界中,通过重布线层(RDL)工艺妙地重新布局IC输入/输出(I/O)焊盘,实现高性能与高可靠性的双重飞跃就一定先要了解“输入/输出(I/O)”,那究竟什么是输入/输出(I/O)呢?

其实,输入/输出(I/O)的缩写“I/O”是“Input/Output”的英文首字母。而输入/输出(I/O)数指的就是芯片上输入输出端口的数量,也可以说是引脚的数量。I/O数量越多,芯片可以同时传输的数据量就越大,处理速度越快。

1、重布线层(RDL)重塑输入/输出(I/O)的未来

重布线层(RDL)这个看似简单的缩写背后,承载着半导体封装领域的一次革命性变革。在追求更高集成度、更快数据传输速度的今天,重布线层(RDL)工艺将芯片的输入/输出(I/O)焊盘从密集的中心区域迁移至边缘,并在更广阔的空间内重新分布。这一创新不仅极大地缓解了输入/输出(I/O)端口拥挤的问题,更为先进封装技术如3D封装、扇出型封装(FOWLP)等提供了强有力的支持,使得芯片能够拥有更多的输入/输出(I/O)数量,从而满足日益增长的数据传输需求。

2、输入/输出(I/O)数量是速度与效率的双重考量

输入/输出(I/O)数量是衡量芯片与外界通信能力的关键指标,直接关乎到芯片的数据吞吐量与处理速度。想象一下,一个拥有众多输入/输出(I/O)端口的芯片,就像是一个四通八达的交通枢纽,能够同时处理来自多个方向的数据流,实现信息的快速交换与处理。因此,随着云计算、大数据、人工智能等技术的蓬勃发展,对芯片输入/输出(I/O)数量的需求也在不断攀升。RDL工艺正是在这一背景下应运而生,它通过优化输入/输出(I/O)布局,让芯片在有限的面积内实现更高的数据传输效率。

三、重布线层(RDL)技术的工艺流程

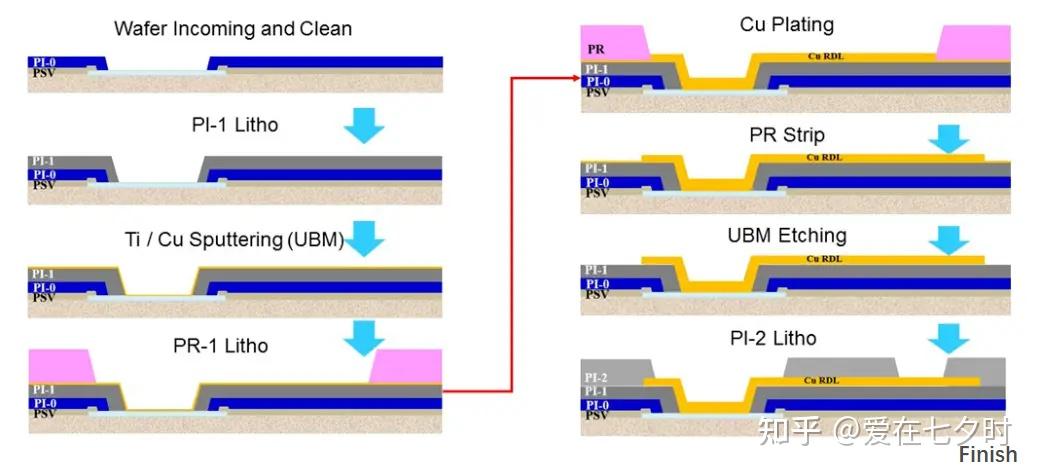

1、晶圆清洗

晶圆清洗是RDL工艺的第一步,通过物理和化学方法去除晶圆表面的杂质和颗粒,为后续的工艺步骤创造一个干净、无污染的工作环境。这一步骤对于提高光刻胶和金属沉积层的附着性至关重要。

2、PI-1 Litho(第一层PI光刻)

在这一步中,利用PSPI(光敏性聚酰亚胺)光刻工艺,在晶圆上精确地制作出第一层钝化层(PI-1)的图案。PSPI作为一种高性能的光刻材料,能够在紫外光照射下发生化学变化,从而实现图案的精确转移。这一过程为后续的金属沉积提供了必要的保护屏障。

3、Ti/Cu Sputtering(钛/铜溅射沉积)

紧接着,进行钛/铜溅射沉积,形成底部金属层(UBM)。钛层作为缓冲层,能够有效隔离铜层与钝化层之间的直接接触,防止铜原子扩散;而铜层则作为电镀的种子层,为后续的电镀工艺提供了均匀的基底。

4、PR-1 Litho(第一层光刻胶光刻)

在UBM层上涂布一层光刻胶,然后通过曝光和显影工艺,精确地定义出RDL的图案。这一层光刻胶就像一张精密的“地图”,指引着铜电镀的方向,保护着不需要电镀的区域,同时在需要电镀的区域暴露出铜层。

5、铜电镀(Cu Plating)

在光刻胶露出的区域进行铜电镀,形成RDL的导电层。这一步骤是RDL工艺的核心,通过电镀的方式将铜沉积在暴露的UBM层上,形成连接芯片的焊盘和封装外部引脚的导电通道。

6、光刻胶去除(PR Strip)

电镀完成后,需要去除光刻胶,以便进行后续的工艺步骤。这一步通常采用化学方法,将光刻胶从晶圆表面剥离。

7、UBM层蚀刻(UBM Etching)

采用湿法刻蚀技术,去除不需要的UBM层,只保留在RDL电镀区域下方的UBM层。这一步骤确保了RDL结构的精确性和完整性。

8、PI-2 Litho(第二层PI光刻)

最后,进行第二层PI光刻,为RDL提供额外的保护。这一层PI层不仅增强了RDL的机械强度,还提高了封装的可靠性,确保芯片在恶劣环境下仍能稳定工作。

四、重布线层(RDL)工艺的构造材质

重布线层(RDL)的构造并非随意为之,而是经过精心设计的材料组合。阻挡层通常采用Ti/Cu(钛/铜)结构,钛层作为缓冲层,能够有效防止铜原子向钝化层扩散,同时增强铜层与钝化层之间的粘附力;铜层则作为电镀的种子层,为后续的电镀工艺提供坚实的基础。互联材料选用导电性能优异的铜,确保信号在重布线层(RDL)中的高效传输。而介质材料则多采用聚酰亚胺(PI),以其良好的绝缘性、耐热性和机械强度,为重布线层(RDL)提供必要的保护与支撑。

五、重布线层(RDL)工艺的设计目标

1、信号分配

重布线层(RDL)的一个主要目标是将芯片的I/O(输入/输出)信号有效地分配到封装的不同区域。这样做可以优化信号传输路径,减少信号延迟和串扰。

2、电源分布

除了信号线的布置外,重布线层(RDL)还负责电源层的布置,确保芯片和封装基板之间的电流稳定传输,避免过高的电流密度导致过热或烧毁问题。

3、尺寸与性能平衡

通过优化重布线层(RDL)的布局,设计师可以在保持小封装尺寸的同时,满足高性能的要求。这对于高集成度的芯片尤为重要。

六、重布线层(RDL)工艺的设计步骤

重布线层(RDL)的设计通常包括以下几个步骤:

1、信号分配分析

在设计重布线层(RDL)之前,首先要评估芯片内部的信号连接方式,分析每个I/O引脚的功能和其需要的连接路径。通过与芯片设计团队协作,确保信号线的最优布局。

2、布线设计

根据需求进行具体的重布线层(RDL)布线设计。重布线层(RDL)通常采用多层结构,通过不同层次的线路进行信号和电源的分配。设计时需要考虑布线路径、走线长度、宽度、间距等,以优化电气性能并避免信号干扰。

3、电气性能仿真

在设计完成后,通过仿真工具对重布线层(RDL)进行电气性能验证。这包括信号完整性(SI)和电源完整性(PI)分析,确保高频信号不会因布线不当产生衰减,电源分布稳定。

4、热力分析与优化

由于高功率芯片会产生大量热量,重布线层(RDL)的设计还需要进行热力学分析。通过模拟热流和散热路径,确保封装内的温度不会过高,避免对芯片性能产生负面影响。

5、制造与测试验证

重布线层(RDL)设计完成后,进入制造阶段。制造时需要根据设计图纸进行多层基板的制作,并通过各种测试方法验证重布线层(RDL)的电气连接性和机械稳定性,确保封装可以顺利通过后续的可靠性测试。

七、重布线层(RDL)工艺技术与封装的关系

重布线层(RDL)层通常作为芯片封装的核心组成部分,与其他封装结构(如基板、外部引脚等)紧密配合。它不仅为芯片和封装基板之间的连接提供了通路,还决定了封装的电气性能、散热性能以及最终的封装尺寸。

例如,像BGA(Ball Grid Array)或FCBGA(Flip Chip Ball Grid Array)封装中,RDL负责将芯片的I/O引脚重分布到基板上的焊球位置,确保信号从芯片传输到封装外部的电路板。

八、重布线层(RDL)工艺的技术挑战

1、多层结构复杂性

重布线层(RDL)设计需要使用多层布线,这增加了设计的复杂性。设计师需要平衡信号传输质量、热性能和机械稳定性等因素。

2、信号完整性问题

随着芯片频率和集成度的增加,重布线层(RDL)中的信号完整性问题变得愈发严重。如何减少信号的损失、避免信号串扰、提高抗干扰能力是重布线层(RDL)设计的关键。

3、尺寸与成本控制

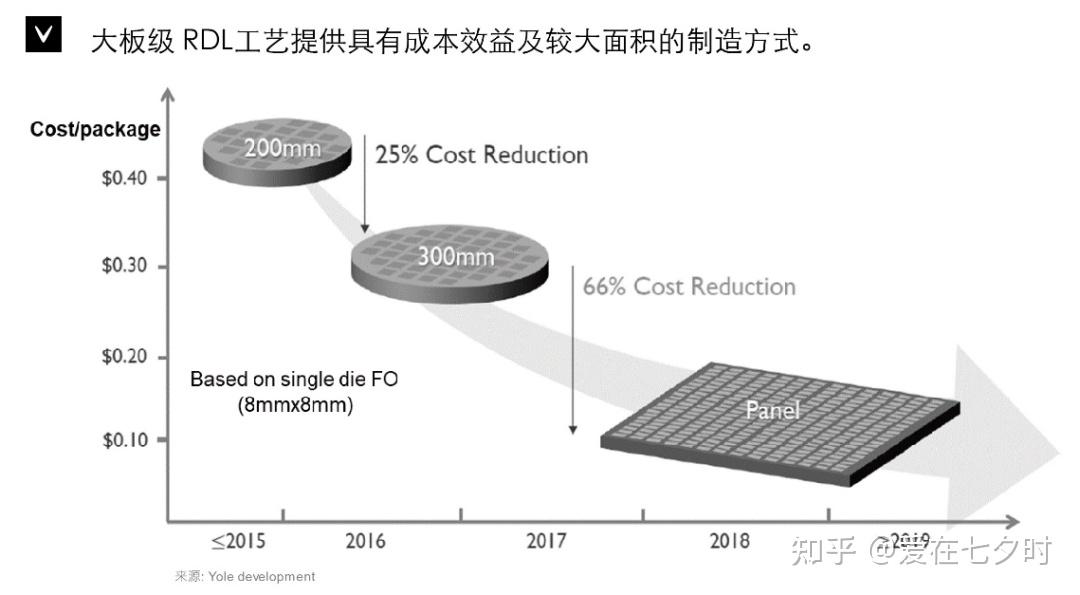

在保证性能的前提下,重布线层(RDL)的设计需要尽量减少封装的体积和制造成本。因此,如何通过优化布线来减小封装尺寸,并确保成本可控,是设计过程中必须考虑的因素。

九、重布线层(RDL)工艺的应用与发展趋势

当前,重布线层(RDL)工艺的应用的应用领域主要有以下几方面:

1、AI/HPC芯片

(1)2.5D封装:CoWoS用RDL替代硅中介层连接GPU与HBM(成本降低30%)

(2)3D IC:混合键合前的临时互联层

2、移动设备

Fan-Out WLP:苹果A系列处理器用重布线层(RDL)直接连接PCB,厚度减少40%

3、汽车电子

耐高温重布线层(RDL):掺钌铜导线可在150℃下稳定工作

4、CIS传感器

超细线路:0.8μm 重布线层(RDL)实现2000万像素传感器布线

重布线层(RDL)技术作为先进封装的核心互连方案,通过重分布芯片I/O信号实现三大关键应用:在Flip Chip封装中优化焊球布局(Redistribute I/Os for bump alignment),在WLP晶圆级封装中重构布线路径(Reconfigure routing paths),以及在SiP系统集成中搭建多芯片互连桥梁(Bridge multi-die interconnection)。这项"万能布线"技术(Universal wiring solution)既能突破芯片原生I/O限制,又可实现微米级互连,同时降低30%以上封装成本,已成为从2.5D/3D封装到Chiplet集成的关键使能技术。

随着集成电路技术的不断进步,封装的要求也越来越高。重布线层(RDL)工艺技术在高性能芯片封装中起着越来越重要的作用。尤其在像5G、AI、汽车电子等领域,对封装的要求更是不断提高。未来,重布线层(RDL)工艺技术将朝着更高频、更小尺寸、更低成本的方向发展,同时加强与热管理、可靠性分析等其他封装领域的协同设计。

总结一下

重布线层(RDL)工艺是集成电路封装中不可或缺的设计层,负责芯片与封装之间的电气连接与信号分配。它不仅影响封装的电气性能,还与封装的尺寸、热管理、成本等多个因素密切相关。随着技术的发展,重布线层(RDL)工艺技术设计正变得越来越复杂,要求设计师在保证性能的同时,还需优化尺寸、成本,并解决信号完整性等技术挑战。

免责声明

【我们尊重原创,也注重分享。文中的文字、图片版权归原作者所有,转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时私信联系,我们将第一时间跟踪核实并作处理,谢谢!】

审核编辑 黄宇

-

晶圆凸起封装工艺技术简介2011-12-01 5305

-

半导体工艺技术的发展趋势2019-07-05 4527

-

半导体工艺技术的发展趋势是什么?2019-08-20 4474

-

半导体工艺技术2016-05-26 1180

-

SONNET中的工艺技术层介绍2019-10-08 2756

-

详解半导体封装测试工艺2023-05-31 2320

-

先进封装关键技术之TSV框架研究2023-08-07 3337

-

什么是先进封装?先进封装技术包括哪些技术2023-10-31 3870

-

先进封装RDL-first工艺研究进展2023-12-07 3910

-

半导体先进封装技术2024-02-21 1565

-

芯片先进封装里的RDL2024-09-20 3714

-

先进封装中RDL工艺介绍2025-01-03 5856

-

芯片封装中的RDL(重分布层)技术2025-03-04 4696

-

先进封装中的RDL技术是什么2025-07-09 3252

-

半导体先进封装“Bumping(凸点)”工艺技术的详解;2025-11-10 3146

全部0条评论

快来发表一下你的评论吧 !