罗德与施瓦茨HDMI源端物理层一致性测试解决方案

描述

PART 1

HDMI接口简述

HDMI(High-Definition Multimedia Interface, HDMI)是专用于数字音视频传输的高速接口标准。采用HDMI接口以后,所有的视频、音频甚至控制信号都可以通过一根HDMI线缆传输,大大简化了连接。由于HDMI可以支持高清、3D等应用,且芯片技术成熟稳定,因此已经是一个非常成功的数字显示接口。

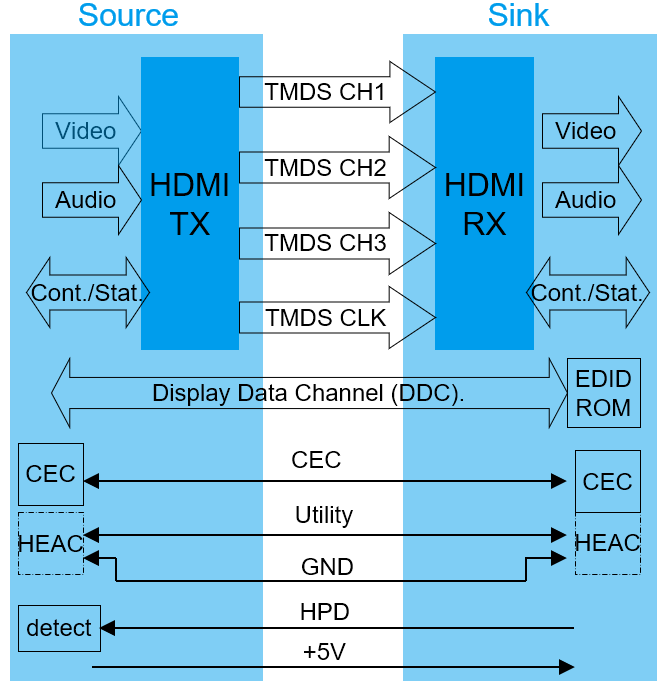

按照HDMI标准的定义,HDMI设备分为Source(源设备)、Sink(接收设备)以及Cabel(电缆)、Repeater(中继设备)。Source源端设备产生HDMI信号输出,如计算机、机顶盒、数码相机、DVD、游戏机等;Sink设备接收HDMI信号并显示,如显示器、电视机、投影仪等。

PART 2

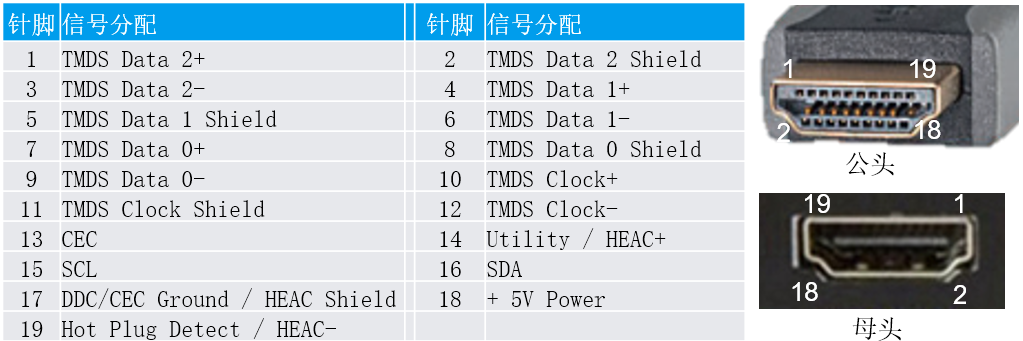

HDMI接口的信号分配

在HDMI标准中,音频和视频信号均采用统一的数据打包机制,通过TMDS通道进行传输。音频信号不占用额外的通道,而是采用和其他辅助信息一起组成数据包,利用TMDS通道在视频信号传输的消隐期进行传送。

HDMI接口总线上,包含4对TMDS差分信号,分别是3对差分数据和1对差分时钟。

除了TMDS信号以外,在HDMI总线上还有以下几种信号:

Display Data Channel (DDC) 显示数据通道:用于从 Source端 读取 Sink端 的增强型扩展显示识别数据(E-EDID),交换用于高清数字内容保护 (HDCP) 的加密密钥,例如Sink 所支持的视频分辨率、音频格式/频道等信息。

Consumer Electronics Control (CEC) 消费电子控制通道:它是单线双向控制总线,其核心目标是实现跨设备联动控制,例如:通过电视遥控器控制机顶盒、音响等设备;打开电视时自动唤醒播放设备;关闭电视时同步关闭外设。

Utility 通道:复用作为私有化辅助通信(固件升级、诊断)、HEAC(HDMI Ethernet Audio Return Channel ) 标准化以太网和音频回传、eARC 增强型音频回传等功能。

Hot Plug Detection line (HPD):热插拔通道,用于HDMI设备插入检测。

此外HDMI接口还有一根+5V电压线用于给显示器的E-EDID存储器供电,以及若干根GND屏蔽线。

PART 3

HDMI标准的迭代

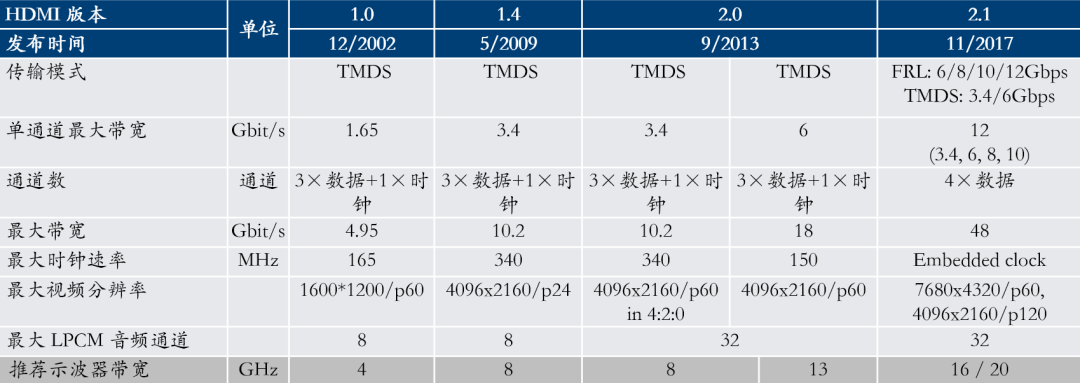

在HDMI.org(HDMI组织)和2011年新成立的HDMI Forum(HDMI论坛)的共同推动下,HDMI标准快速迭代,特别是HDMI 2.1标准中FRL传输模式的引入显著提升了传输带宽与数据速率。

在HDMI2.1之前的HDMI总线上,主要用来进行音视频信号传送的是4对TMDS差分信号,包括3对数据和1对时钟。当TMDS数据线速率≤3.4Gbps时,时钟线上的时钟频率为数据线传输速率的1/10。例如每对数据线上的速率为1.485Gbps时,时钟线上传输的时钟信号频率为148.5MHz。TMDS时钟频率和传输的像素频率一致,所以有时又称为像素时钟频率(Pixel Clock Rate)。当TMDS数据线速率>3.4Gbps时,TMDS时钟速率是数据速率的1/40或1/20。

HDMI2.1标准,既兼容了传统的TMDS传输方式,单对数据线速率高达6Gpbs;又增加了FRL(Fixed Rate Link)新传输模式。FRL模式取消了专门的TMDS时钟通道,改为使用嵌入式时钟,将4组差分对同时用于传输数据;每对差分线速率6G/8G/10G/12Gbps,实现了更高的总带宽,并支持动态速率协商(如24/32/40/48 Gbps总带宽)。FRL传输使得无损8K/60Hz 和 4K/120Hz 、动态HDR成为可能,满足了超高清影视与游戏的需求。

但不管哪一个版本的标准,都涉及TMDS(Transition Minimized Differential Signaling, 最小化传输差分信号)模式。TMDS作为数字视频传输的核心技术,其物理层性能直接影响系统兼容性、抗干扰能力及最终显示质量,因此基于标准规范的源端TMDS一致性测试已成为设备研发与认证的关键环节。以下章节,我们将专注于TMDS物理层一致性测试。

PART 4

TMDS传输方式的编码

TMDS是传统DVI显示接口传输技术的基础,HDMI继承了DVI的这项传输技术,所以DVI和HDMI接口之间是可以通过适配器顺畅转接的。TMDS是英文“Transition Minimized Differential Signaling”的缩写,直译为“跳变最小化差分信号”,它采用一种强制减少相邻比特跳变的8B/10B编码方式。它根据8位原始数据中“1”的数量选择XOR(异或)或XNOR(异或非)逻辑算法,转换生成9位中间码,其中前8位数据由原始信号经运算后获得,第9位则指示运算的方式;再通过反转这9位中间码实现直流平衡,最终输出10位码(第10位标记反转的状态);转换后的数据以差分方式传送。这种8B/10B编码强制减少相邻比特跳变,使得对外电磁辐射和ISI码间干扰减少,传输的数据趋于直流平衡,提高了信号传输的可靠性。

这里要注意TMDS和USB3.0的8B/10B编码方式不是同一回事,USB3.0 直接通过预定义的码表将8位数据映射为10位码,并使用专用K码作为数据包起始分隔符或控制指令,如K28.5(码字0011111010)用于数据包起始。TMDS无独立控制码,通过特定同步头(如视频消隐期的控制周期)标识数据包类型。

HDMI2.1的FRL模式并未沿用传统的TMDS 8B/10B编码,而是通过 BCH纠错码 + 无额外编码开销的直流平衡设计, 实现了更高的有效带宽效率。

PART 5

TMDS信号的电气特性

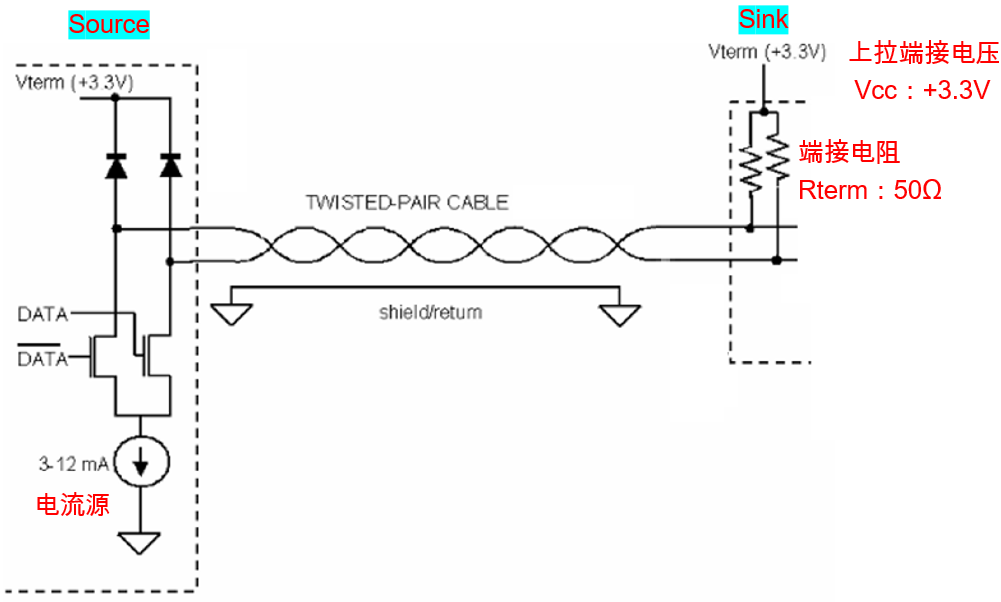

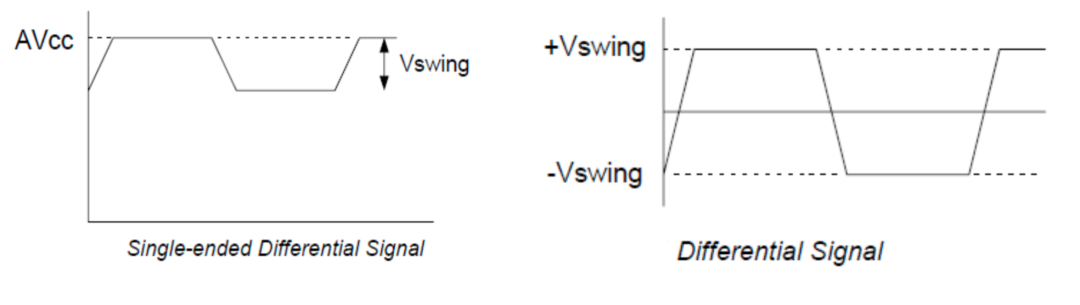

TMDS每通道数据速率最高为 6.0 Gbps。使用电流模式逻辑(CML)在一对差分线上串行传输数据。发送端采用电流源切换方式驱动差分线,Sink端通过Rterm(50欧姆)提供3.3V 上拉电源,电流值(通常为3-12 mA)与终端电阻Rterm(50欧姆)共同决定摆幅。

Vswing = Idirve * Rterm

例如,

当驱动电流为8 mA,终端电阻50 Ω ,单端信号摆幅Vswing为 8mA×50Ω=400mV。

差分信号摆幅为单端摆幅的两倍,即800mV。

PART 6

TMDS源端一致性测试的挑战

鉴于TMDS差分信号的高速传输特性,确保所研发的设备与不同品牌、版本的HDMI显示器/源端(如游戏主机、蓝光播放器)无缝协作,避免黑屏、分辨率不匹配等问题,是硬件和测试工程师的重要挑战。基于HDMI规范的TMDS源端电气特性测试是产品开发中不可或缺的环节,它不仅关乎技术合规性,更是保障用户体验、降低商业风险的关键手段。

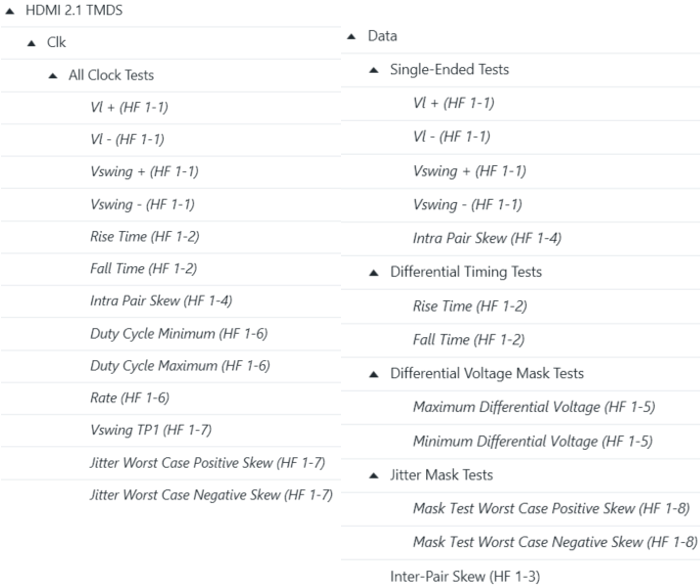

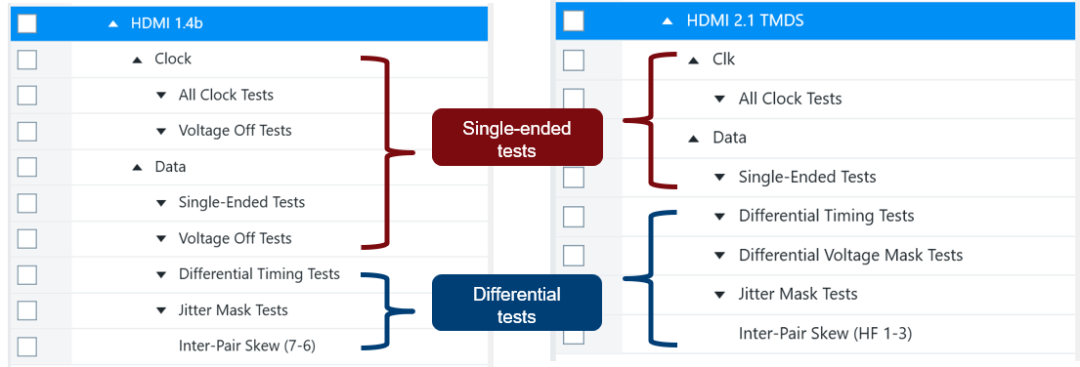

HDMI1.4b和2.1规范,针对于TMDS时钟/数据的单端、差分电气特性,如低电平、信号摆幅、占空比、上升/下降时间、差分对内偏移、差分对间偏移、差分数据眼图、差分时钟抖动、差分数据抖动等,都定义了详细的指标要求。

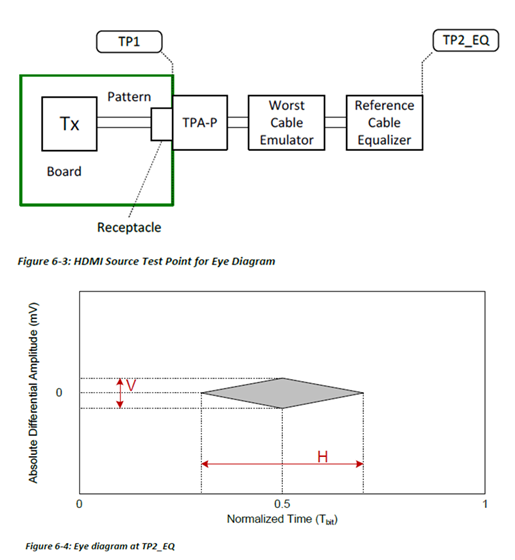

HDMI2.1 TMDS眼图测试,示波器软件还需要具有最差线缆模拟、参考线缆均衡等功能。

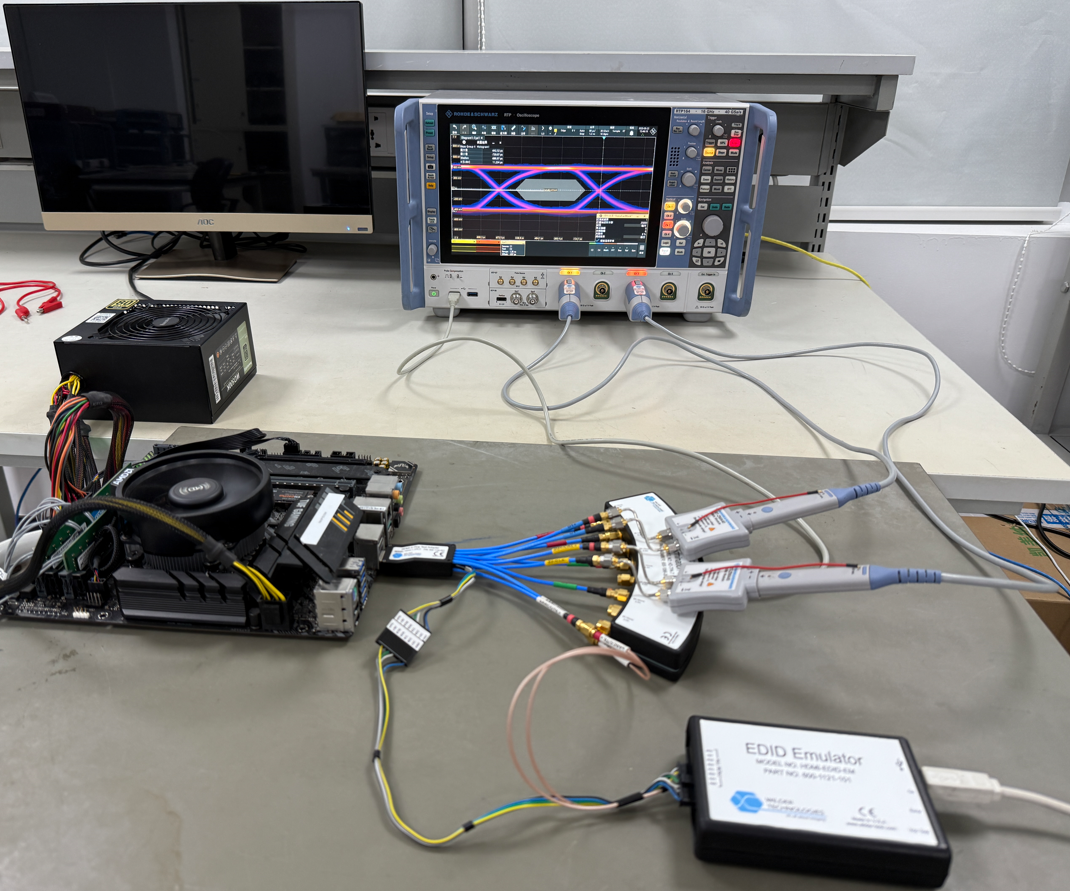

测试人员面对如此众多的测试项目和指标要求,不仅需要有匹配于TMDS信号速率的高带宽示波器、探头、夹具、EDID仿真器等硬件设施,还要熟悉各个测试项目的原理与测试流程。想要高效、顺畅得到产品的测试数据,绝对是一项颇具挑战性的任务。

PART 7

R&S HDMI 源端测试方案

对不同协议和速率的高速信号进行一致性分析,所需的示波器带宽不同。鉴于TMDS信号的频谱特性,通常来说捕获到其基波的三次以上谐波,就可以做一致性测试。例如3.4Gbps的TMDS信号,示波器能抓住其1.7Ghz基波的三次谐波即可,需要5.1Ghz以上带宽示波器;而最高6Gbps的TMDS信号,基波频率为3Ghz,抓住其三次谐波需要9Ghz以上带宽。罗德与施瓦茨的RTP系列示波器,带宽涵盖4G/6G/8G/13G/16G等型号,可以对应不同速率的测试。若考虑兼容不同的产品和速率场景,推荐采用13G带宽的RTP134B。

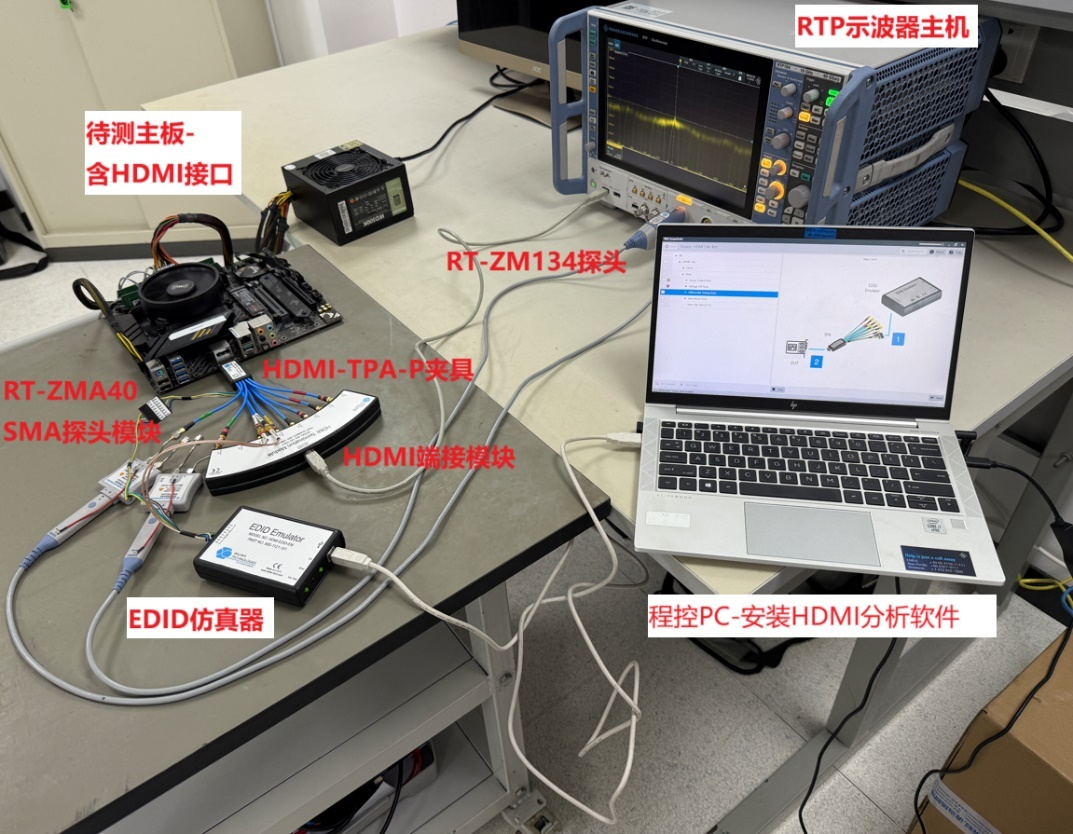

对于6Gbps的TMDS测试,典型的配置如下:

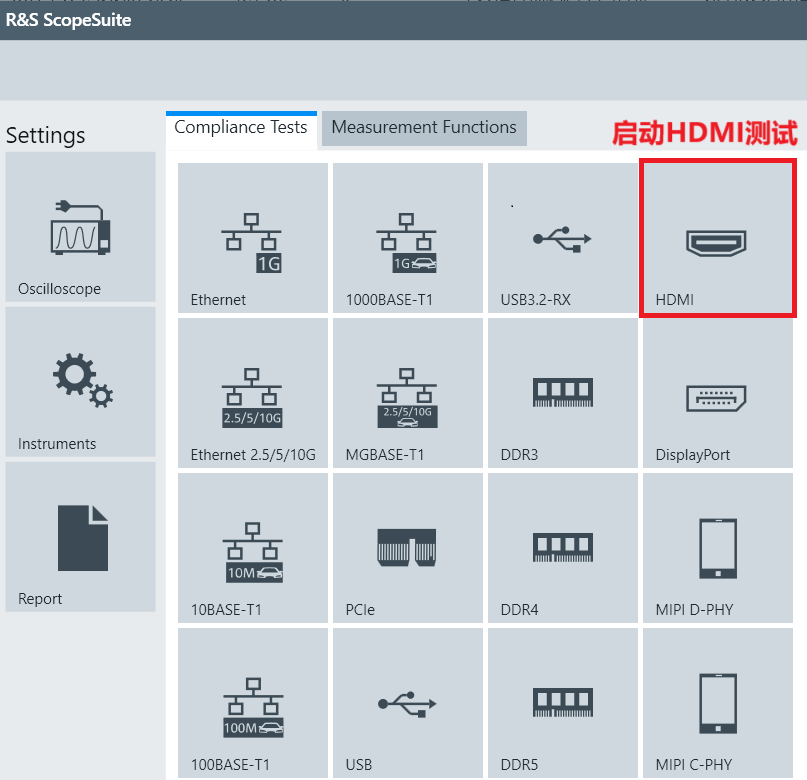

罗德与施瓦茨公司提供专门针对HDMI Source端物理层一致性测试的选件 RTP-K110,配合高级眼图K136/137和高速串行码型触发工具K140/K141,可以高效完成复杂的测试。

测试过程基于界面友好的ScopeSuite软件平台,提供了Step by Step引导式设置指南,就算是新手也可以在设置步骤的文字和参考图片指引下,顺畅完成测试过程。

软件设计人员将所有测试项目按照实测中的探头和线缆连接方式进行分组,跑一遍测试,就可以得到相同连接下所有测试项目的结果,大大节约了测试时间。

PART 8

HDMI测试的夹具选择

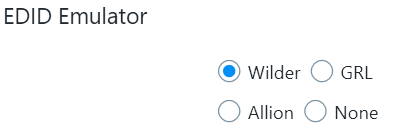

HDMI测试夹具是验证设备信号完整性、协议兼容性和电气性能的关键工具,其设计需符合HDMI标准规范(如CTS),确保测试结果准确且可重复。选择时可根据测试阶段、版本兼容性和预算综合考量,优先选择通过HDMI Forum认证的夹具。RTP-K110软件具有广泛的兼容性,可以适配Wilder 、GRL和Allion的夹具。用户在软件界面选择不同的夹具品牌,会出现基于特定夹具的引导界面,给测试操作人员和初学者带来很大的便利。

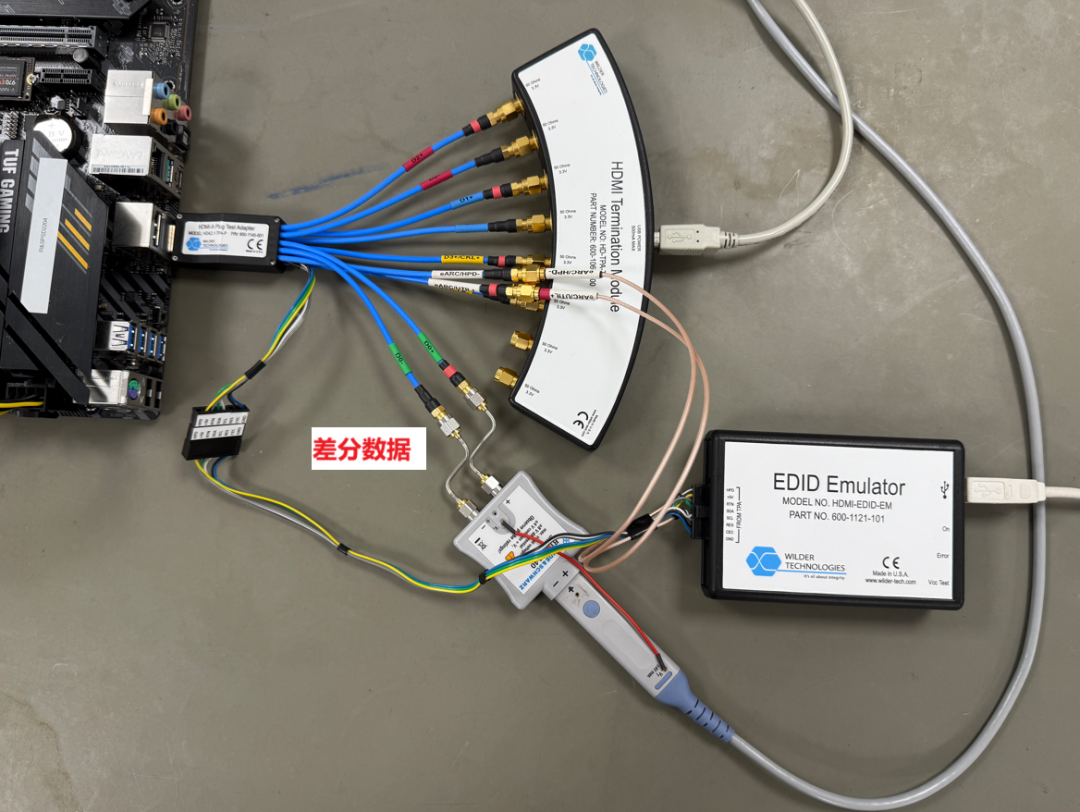

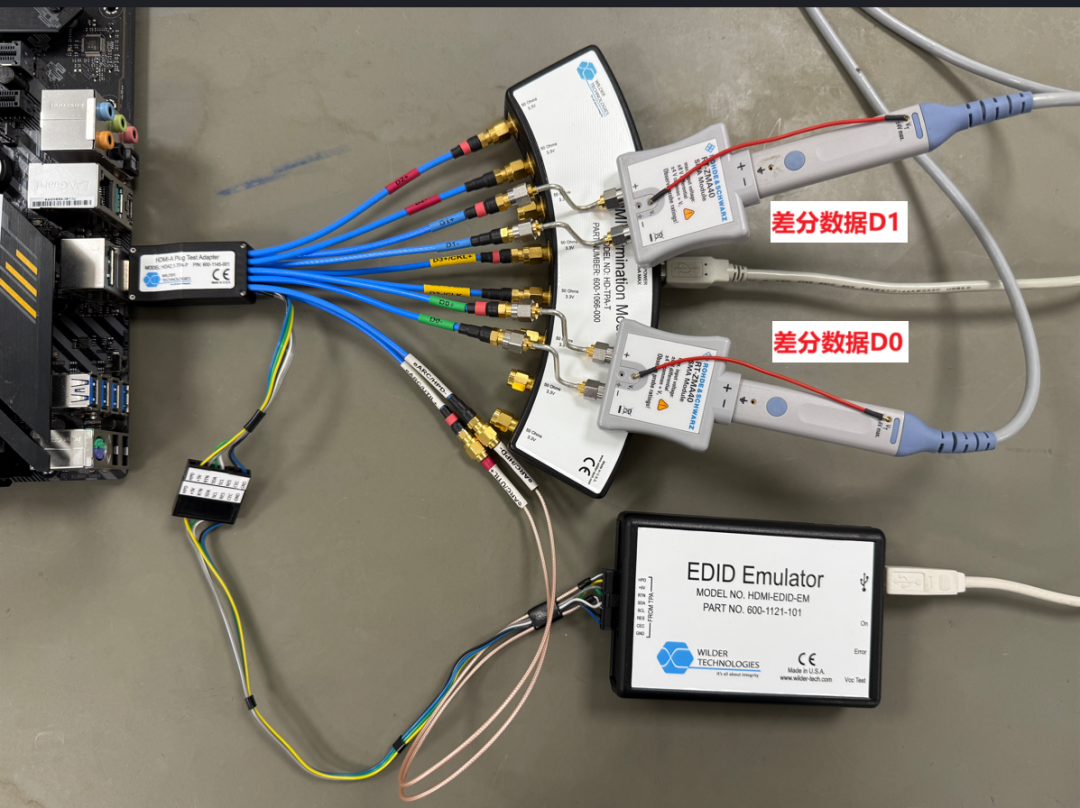

对于电脑主板、DVD这种HDMI Source端A接口母头插座来说,如果购买Wilder公司的夹具,需要配置:

HDMI-TPA-P:HDMI接口转SMA接头适配器。

HDMI-TPA-T: HDMI端接模块,将未使用的TMDS通道用50欧姆电阻、3.3V电压上拉端接。此模块可采用USB线缆从示波器的USB接口提供+5V供电。

HDMI-EDED-EM:HDMI EDID Sink Emulator Module,即EDID仿真模拟器。此模块通过USB线缆与安装Scope suite一致性分析软件包的示波器主机(或PC)连接。

PART 9

HDMI测试探头的3.3V上拉设计

前面我们提到过TMDS信号发送端采用电流源切换方式驱动差分线,Sink端通过Rterm(50欧姆)提供3.3V 上拉。当采用HDMI-TPA-P夹具将HDMI接口的TMDS差分对转接成SMA线束,再输入到示波器通道进行采集处理,此场景中由于没有Sink设备,缺少3.3V上拉的电路结构,TMDS信号其实是无法正常工作的。

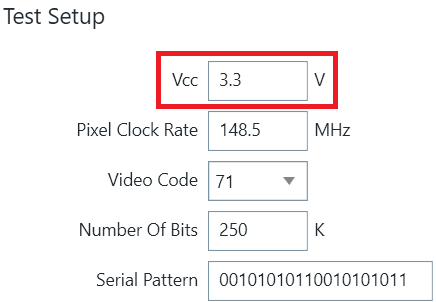

R&S公司用于HDMI测试的RT-ZM系列三模探头,具有最大+/-4V的端接电压VT。通过上图中的红色导线将RT-ZM探头和RT-ZMA40 SMA同轴附件的VT端连起来即可,3.3V上拉电压可在Scopesuite软件界面中设置,这样TMDS信号即可顺利发送出来。

PART 10

HDMI1.4b源端一致性实测简介

1. R&S HDMI测试交互界面

Scopesuite示波器一致性测试平台,可以安装在示波器主机上,也可安装在程控PC上。运行在PC上时可通过网口以Web browser方式对示波器测试波形进行截图,以及将测试报告直接保存在PC上,对于提高工作效率很有好处。

点击Scopesuite控制面板中的HDMI图标,将进入以下的HDMI协议版本选择页面。下面我们以HDMI1.4b为例进行测试过程介绍。

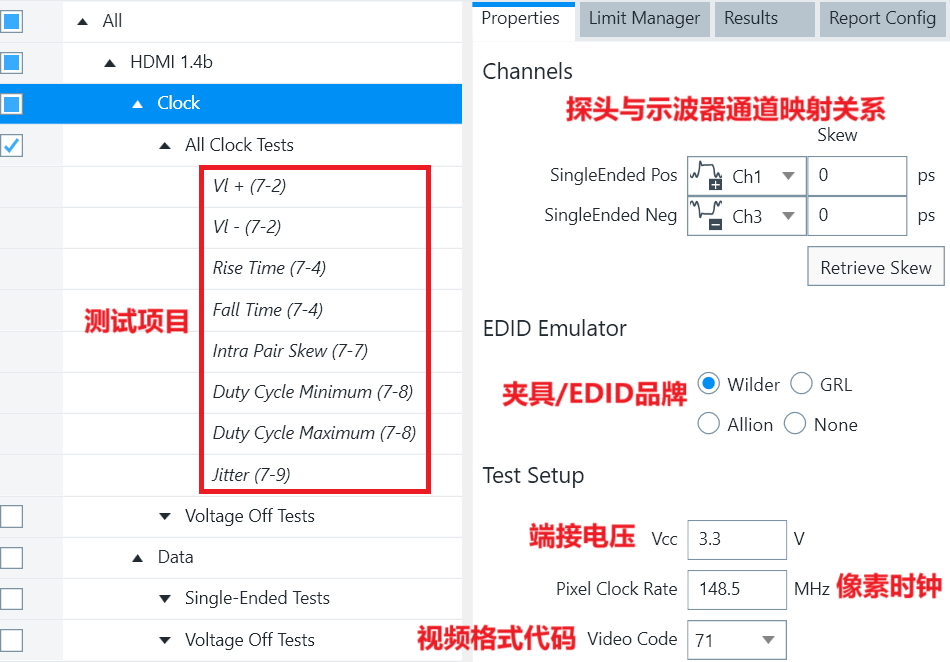

进入HDMI1.4b界面之后,我们可以看到如下的软件界面:

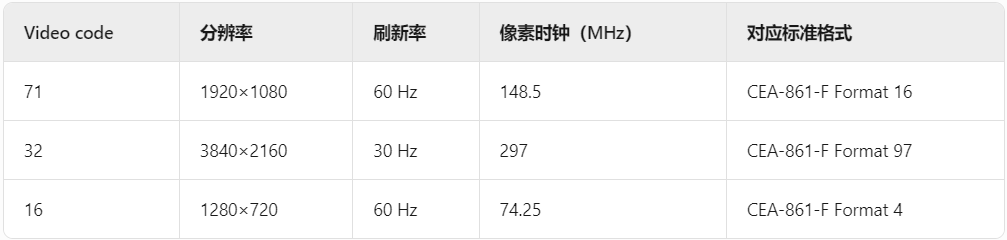

注意软件页面右侧的Properties设置中,像素时钟(Pixel Clock Rate)和视频格式代码(Video Code)是互相关联的。Video code是HDMI测试中用于快速配置视频格式的标识符,通常由测试设备(如示波器、协议分析仪)内部定义,对应特定的分辨率、刷新率和像素时钟组合。148.5 MHz通常对应 1080p@60Hz(1920×1080分辨率,60Hz刷新率),这是HDMI 1.4/2.0的常见测试用例,其视频格式代码为71。

RTP-K110 HDMI软件通过用户选定的Video code(或输入的像素时钟频率),查找到对应的视频格式,并通过EDID仿真器与待测HDMI接口通讯,设置HDMI源端接口输出特定的视频信号。这种软件交互设计,大大降低了测试人员自行去EDID工具中手工进行参数设置的复杂度,提高了测试效率。

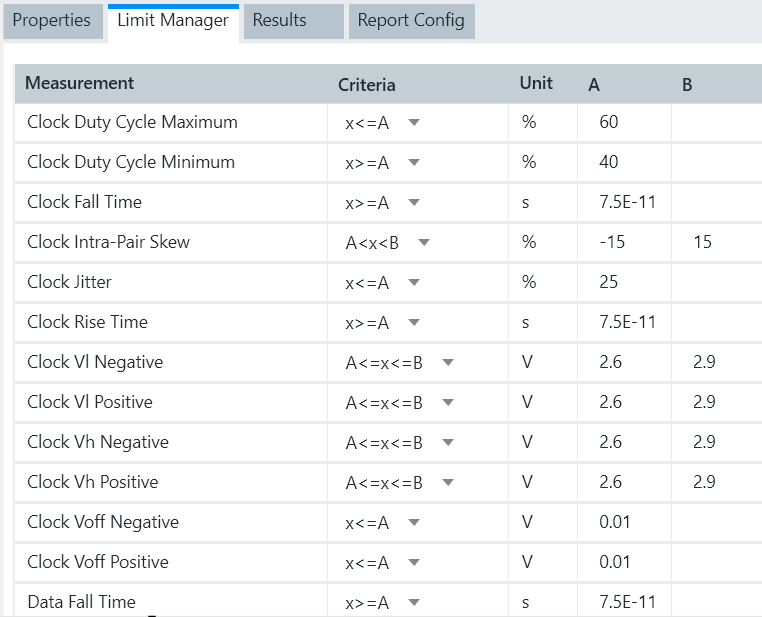

测试界面右侧的Limit Manager是测试指标的参照表,每个测试项目的Pass和Fail就是按照该表格的参数来对照的。

2. 时钟All Clock Test (单端接法)

R&S HDMI TMDS一致性测试软件的界面设计,将所有测试项目按照实测的探头和线缆连接方式进行分组,跑一遍测试,就可以得到相同连接下所有测试项目的结果。

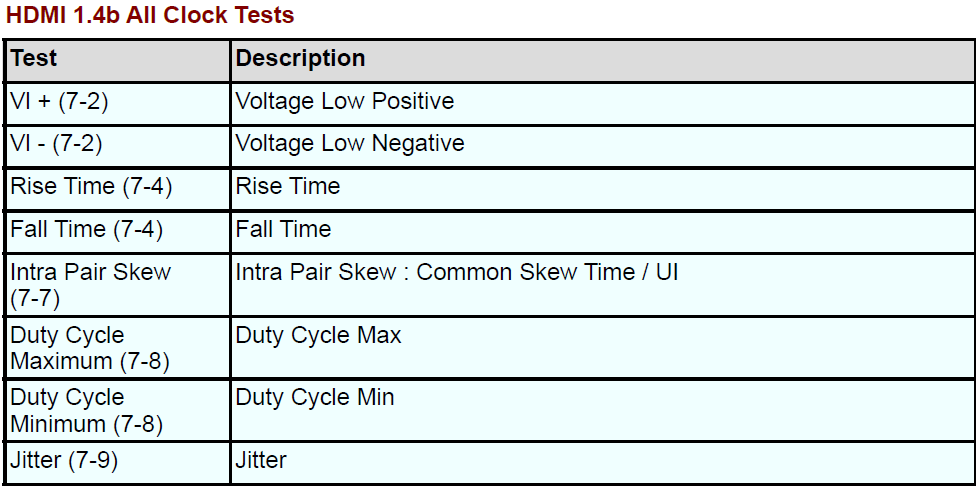

我们进入HDMI1.4b测试软件后,在Clock下的All clock Test测试组,包含如下项目:

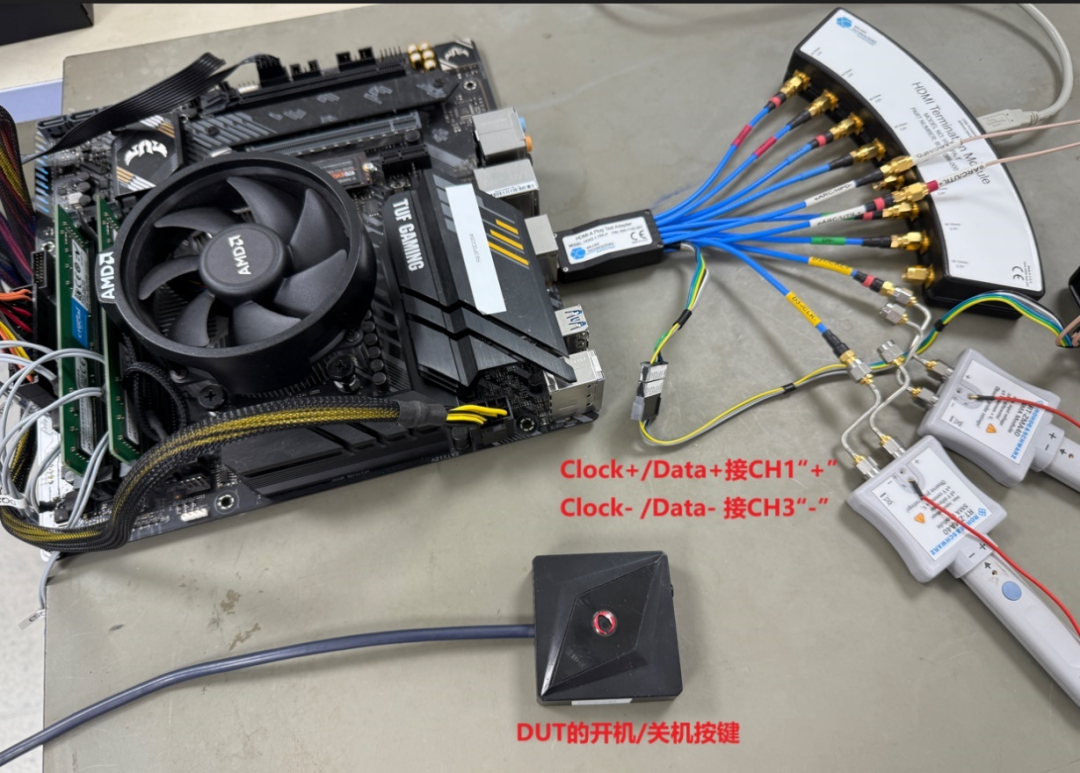

全套测试设备的连接图如下:

上图中HDMI分析软件(集成于Scopesuite平台)安装在一台程控PC上,所以EDID仿真器的USB接口也和PC连接。如果在示波器主机上运行HDMI分析软件,则EDID的USB线缆要改为与示波器的USB口相接。

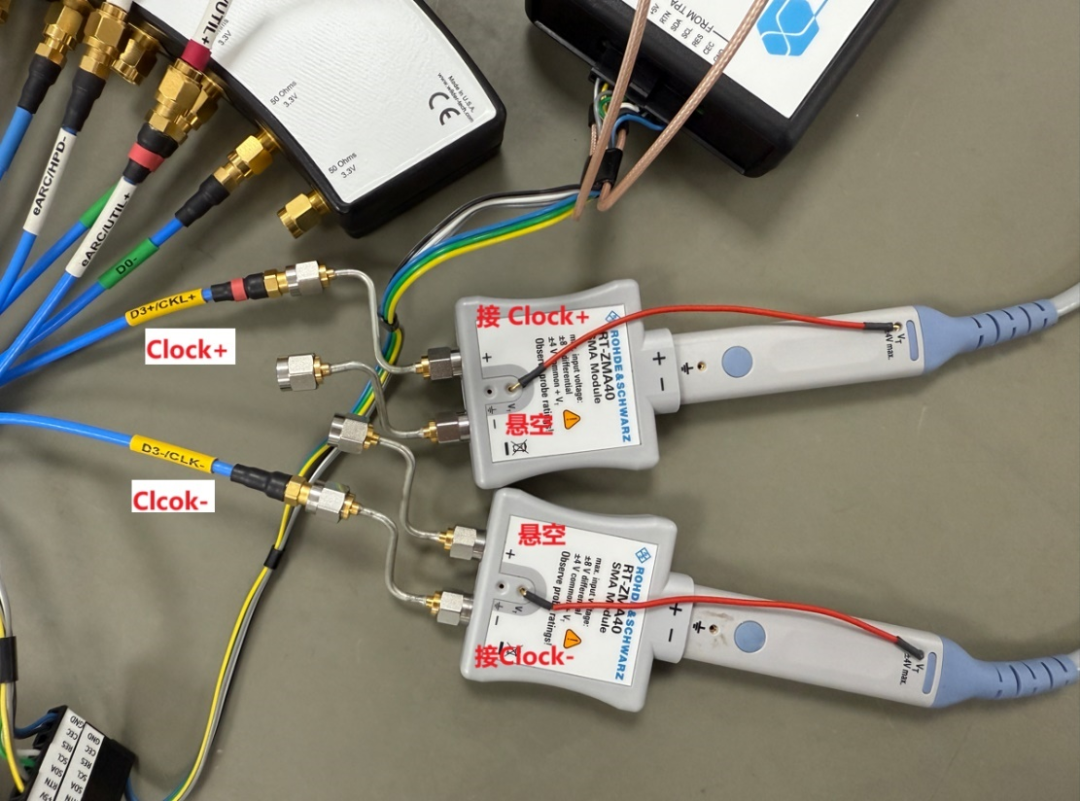

All Clock Tests测试组,所有测试项目都采用单端连接方式:示波器CH1通道SMA探测模块的“+”连接夹具的Clock +, CH3通道SMA探测模块的“-”连接夹具的Clock - ,也就是把差分时钟的Clock+和Clock-分别接入到两个通道中,RT-ZMA40探头模块的空置端口悬空,注意这里的接法不能搞错。

此外,还要特别注意:其它三对暂时没有用到的TMDS数据信号,需要与HDMI-TPA-T端接模块连接,其内部其实是通过50欧姆端接电阻上拉到3.3V电压,否则整个HDMI接口可能会工作不正常,测试结果不准确。测试连接图如下:

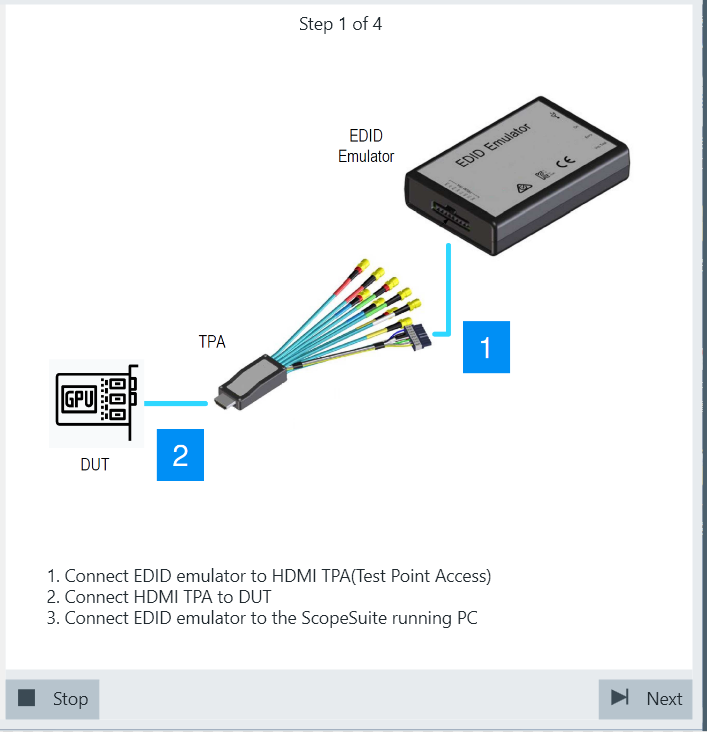

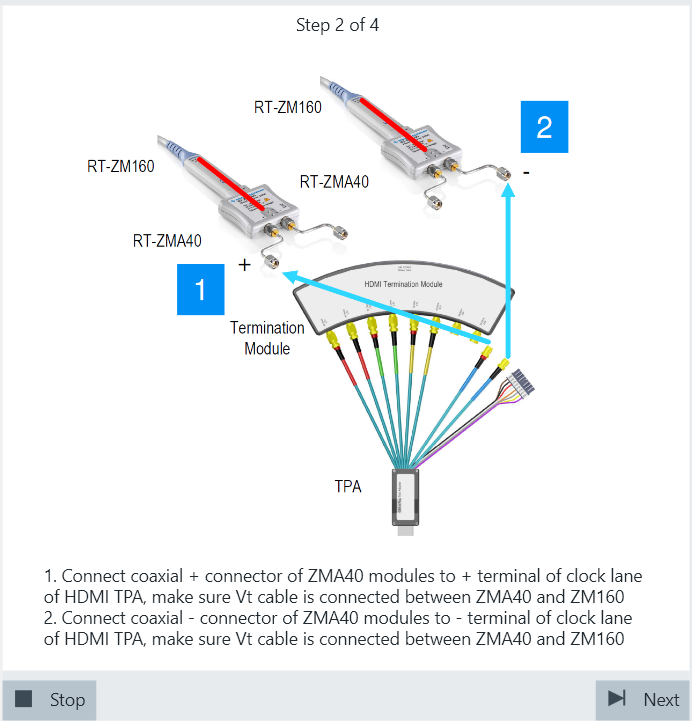

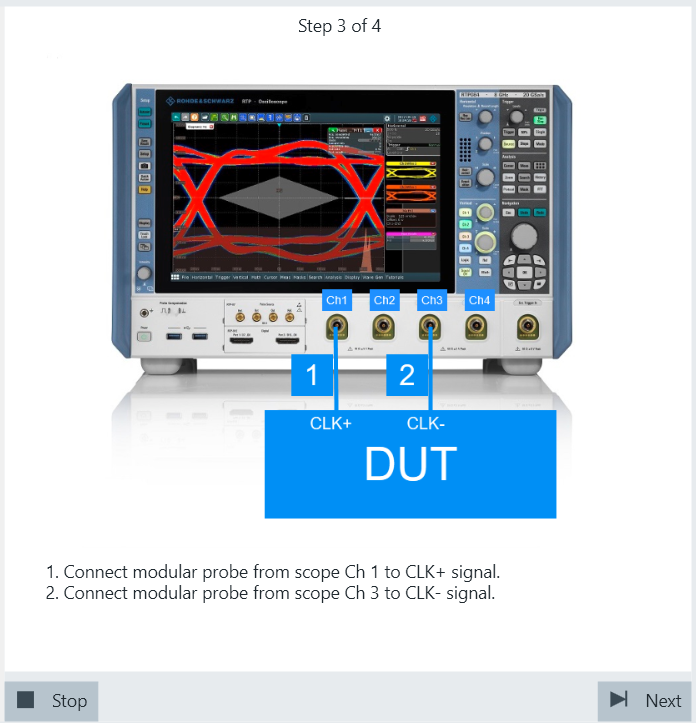

说了这么多,初学者可能感觉连接还挺复杂的。但其实对于使用R&S HDMI测试方案的人员来说,完全不用担心记不住这些步骤,因为软件会进行逐步的设置提醒。以下摘录了All Clock Test测试组的软件引导过程。

01

第一步

提示HDMI-TPA-P夹具与待测的HDMI接口连接,EDID仿真器与Scopesuite软件运行的程控PC(或示波器)连接。

02

第二步

提示RT-ZMA40 SMA探头接口模块与 HDMI-TPA-P夹具的连接。

03

第三步

提示RT-ZM130探头与示波器的连接,CH1接Clock+,CH3接Clock-。

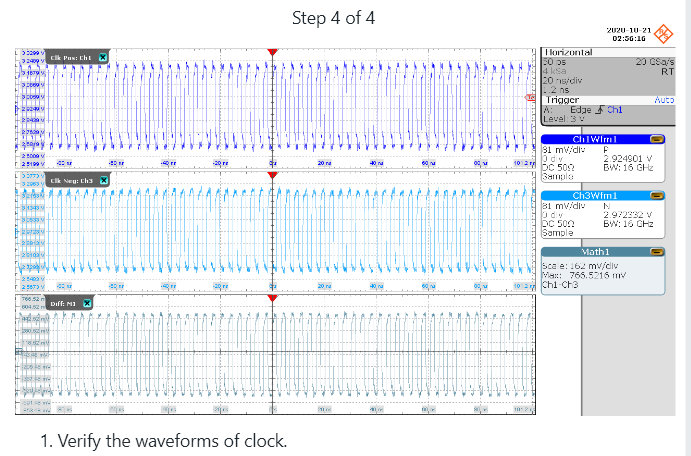

04

第四步

提示验证示波器屏幕上是否出现如软件提示的时钟波形。

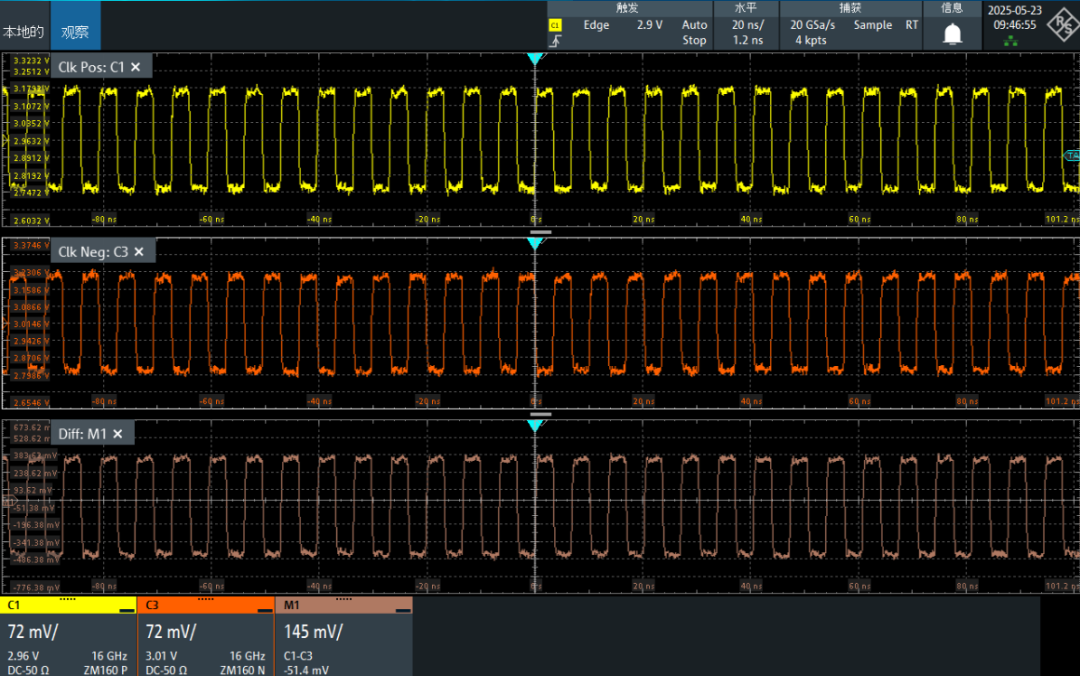

此时,示波器屏幕上的实际波形应该如下,从上至下分别是Clock+、Clock-、Clock差分数学波形。

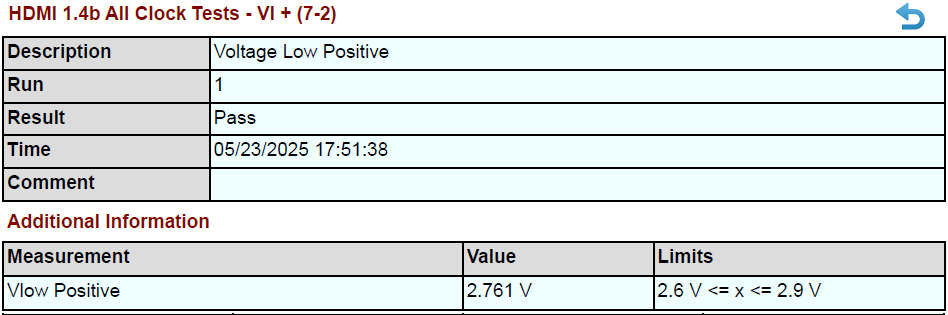

点击确认之后,软件自动捕获所需的波形数据,并进行一系列的分析。下面我们将生成的测试报告逐项展开,查看里面的测试数据。

Vl+ 与Vl- (7-2) 时钟线单端低电平:

测量TMDS差分时钟/数据的单端信号Clock+/Data+的低电平Vl+,以及Clock-/Data-的低电平Vl-。如果 Vl+ 和Vl-的值位于(2.6V~2.9 V)范围内,则测试通过。

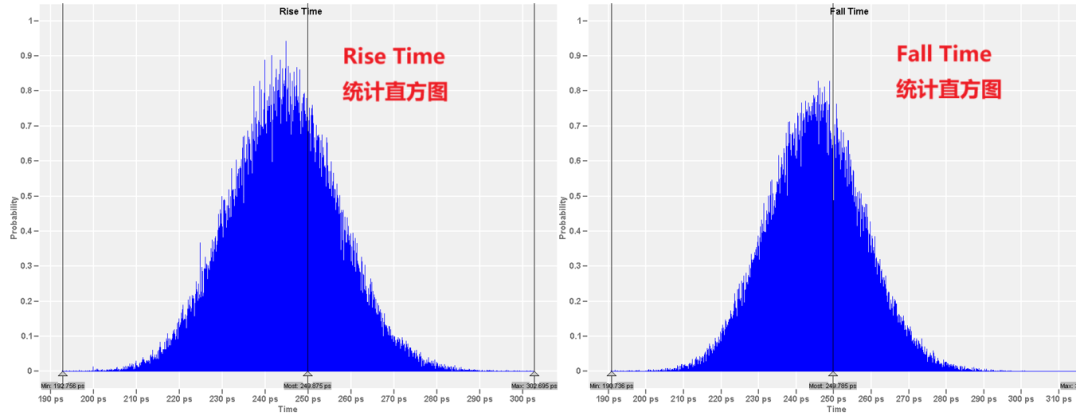

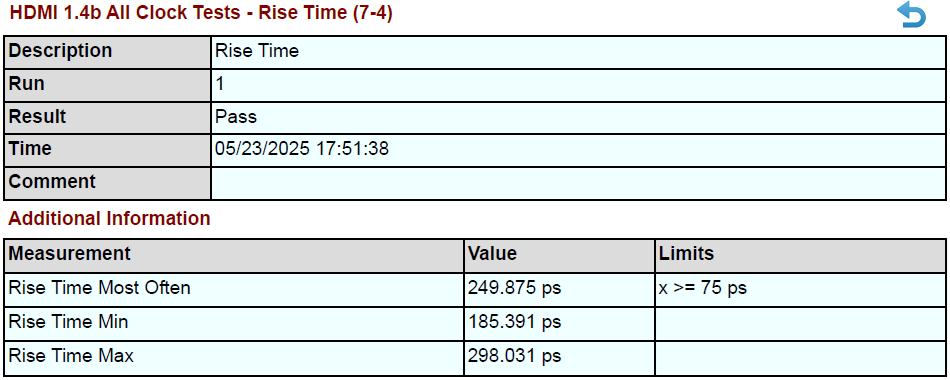

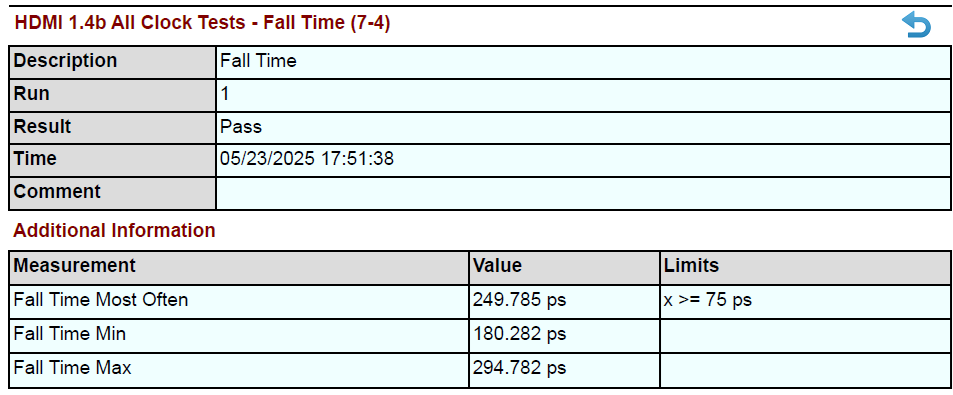

Rise Time 与Fall Time(7-4)上升与下降时间:

测量TMDS 时钟/数据的差分信号的上升时间Trise和下降时间Tfall,如果Trise 和Tfall ≥75ps,则测试通过。软件会自动统计所捕获波形的所有上升和下降沿信息,最终给出Most often和Max/Min的结果。

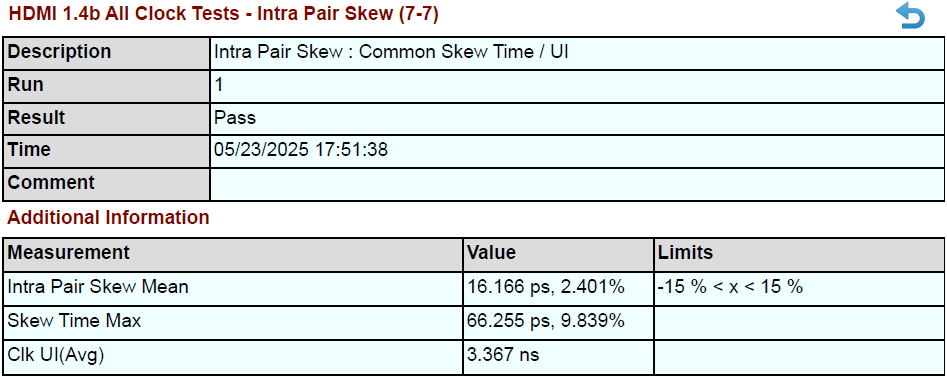

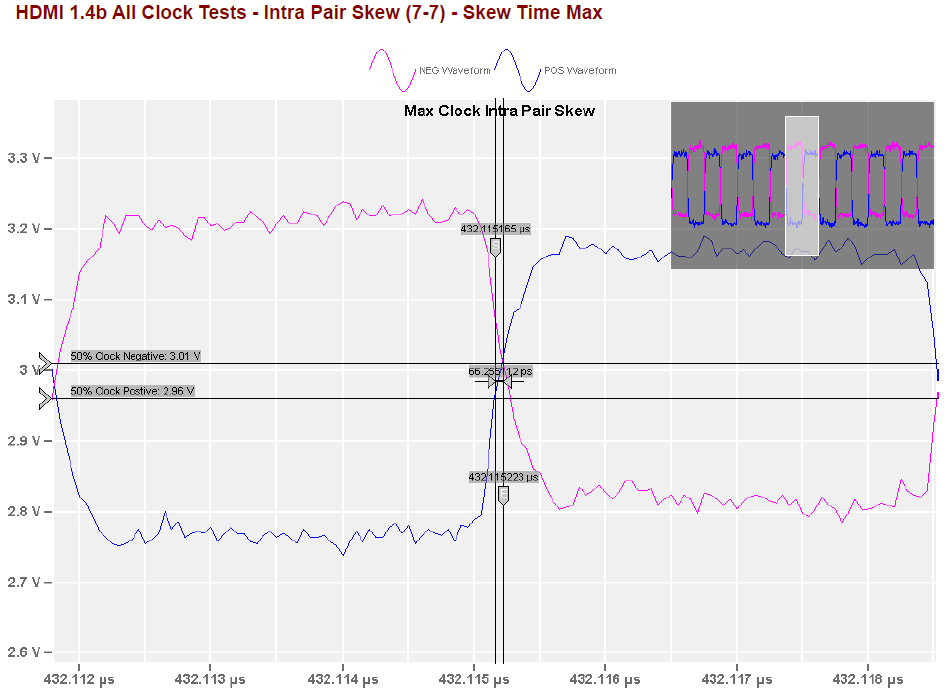

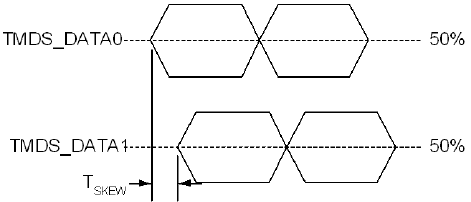

Intra Pair Skew (7-7)差分线对内偏移:

测量TMDS时钟/数据差分对内两个单端信号Clock+/Data+与Clock-/Data-的时间偏差值,即对内偏移。如果对内偏移值在+/-15% Tbit之内,则测试通过。

这里的Tbit为TMDS 数据通道的比特位宽。如果TMDS时钟(像素时钟)为148.5MHz,数据通道的速率则是它的10倍,即1.485Gbps,Tbit为1/1.485G=673.401ps。

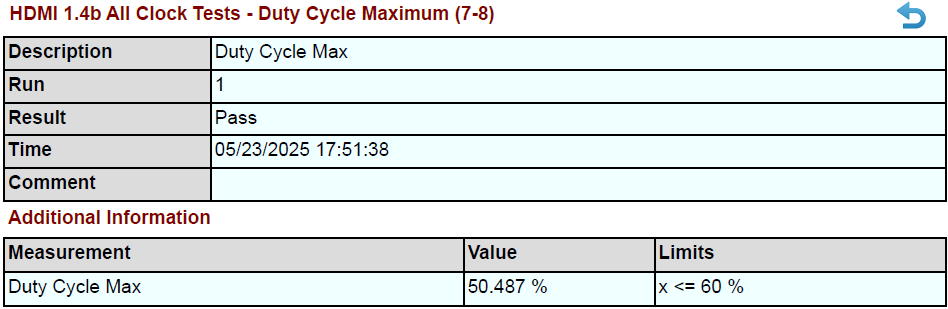

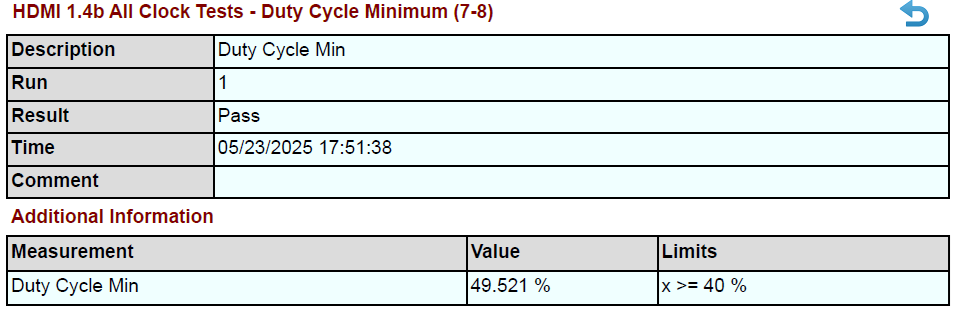

Duty Cycle Minimum与Duty Cycle Maximum (7-8)时钟信号最小/最大占空比:

测量TMDS 时钟差分信号的最小占空比Tduty-min和最大占空比Tduty-max,如果Tduty-min≥40%、Tduty-max ≤60%,则测试通过。

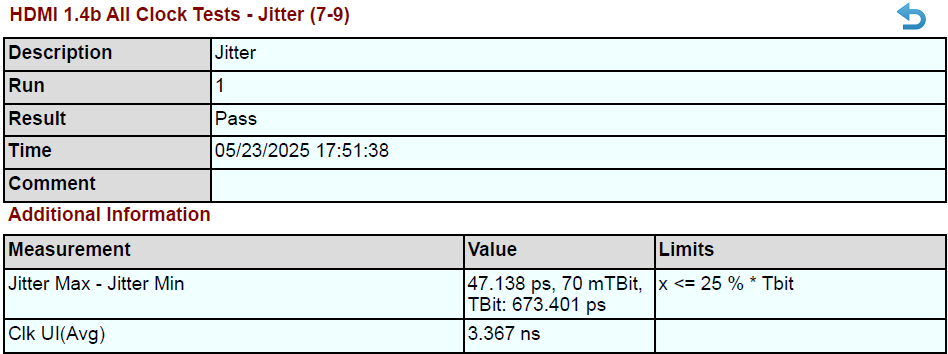

Jitter(7-9)时钟抖动:

测量TMDS 差分时钟相对于理想恢复时钟的抖动,如果Jitter≤0.25Tbit,则测试通过。

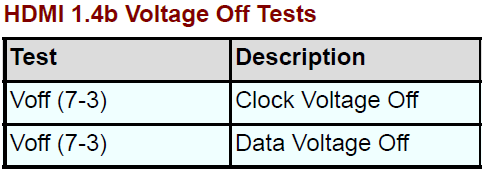

3. 时钟/数据Voltage Off Tests(单端接法)

HDMI1.4b的Clock和Data都有Voltage Off Tests测试组,包含了待机电压Voff+ 、Voff- (7-3)两个内容项 ;但在HDMI2.1的TMDS测试中已经取消了这项测试。

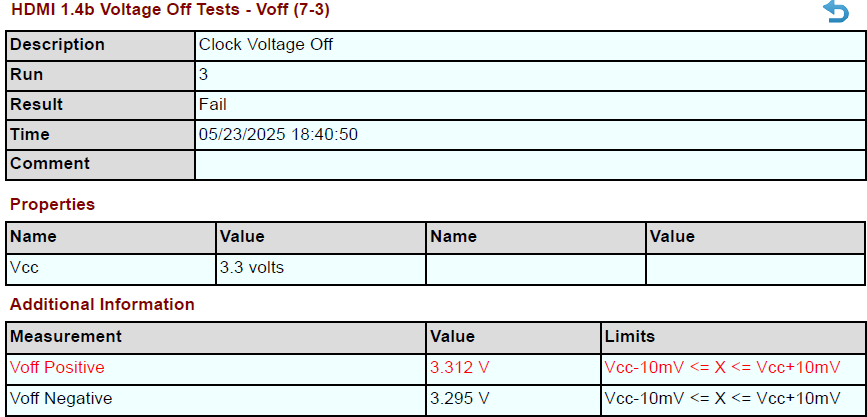

Voff+ 与Voff- (7-3) 待机电压:

测量TMDS差分时钟/数据的单端通道Clock+/Data+待机输出电压Voff+,Clock-/Data-待机输出电压Voff-。如果Voff+和Voff-在Vcc±10mV范围内(Vcc为3.3V,即3.29V~3.31V),则测试通过;如果超过规定限值,则意味着待机时的时钟/数据通道漏电流太大了。

探头和夹具的连接和All Clock Tests的单端连接方法是一样的:

测试报告结果展示如下:

其中Voff-的值为3.295V,与3.3V的Vcc电压差距在10mV以内,测试判定为通过。

但Voff+的值为3.312V,与3.3V的Vcc电压差距在10mV以上,测试判定为失败。

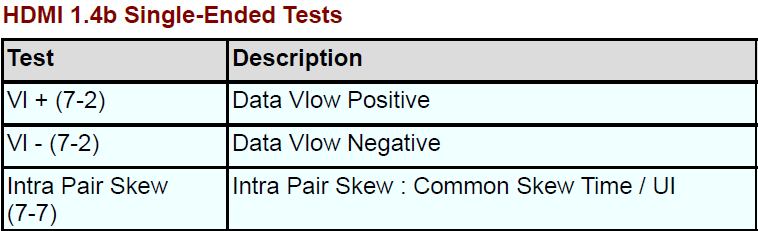

4. 数据Single-Ended Tests(单端接法)

该测试组的测量项包含数据线Data+低电平Vl+(7-2) 、Data-低电平Vl- (7-2) 、Intra Pair Skew (7-7)差分对内偏移。

探头连接方式与All Clock Tests完全一样,都是采用单端接法。数据线的Intra Pair Skew与之前介绍的时钟Intra Pair Skew测试方法和参数要求一样,不再赘述。三对数据线D0/D1/D2分别连接测试一次即可。

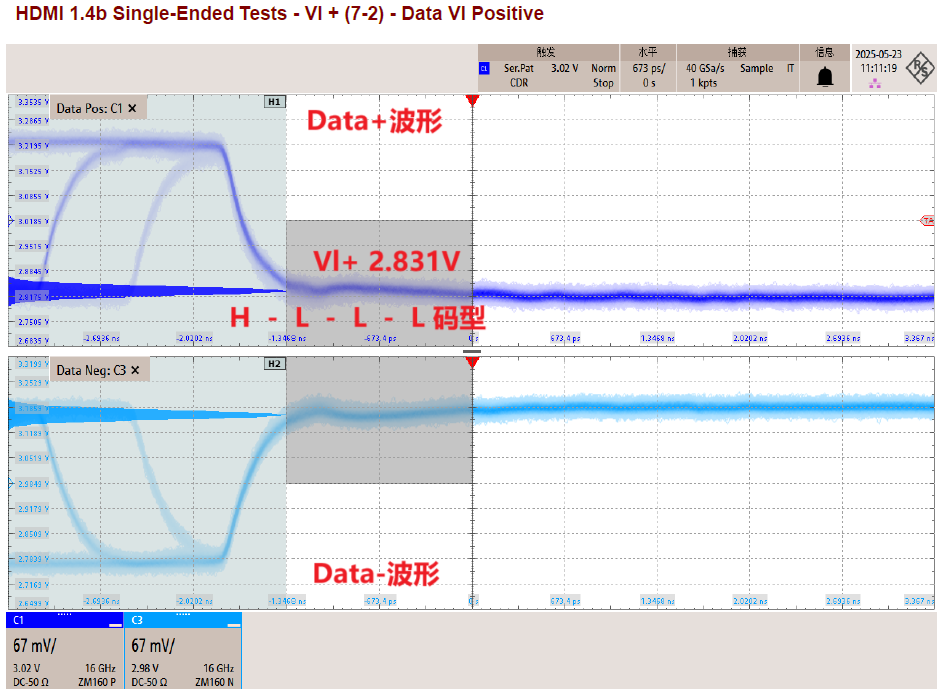

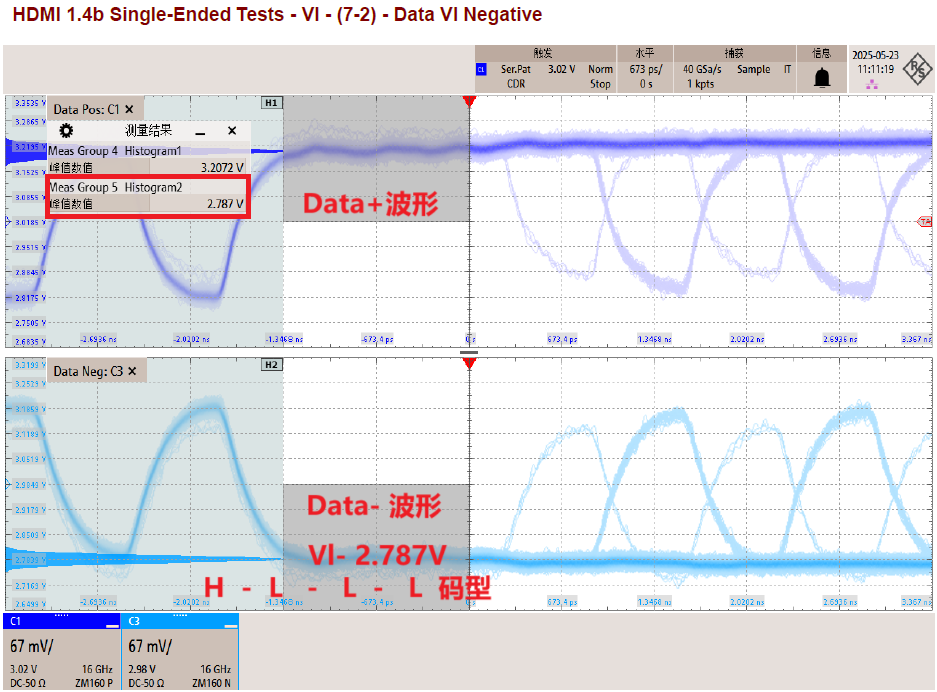

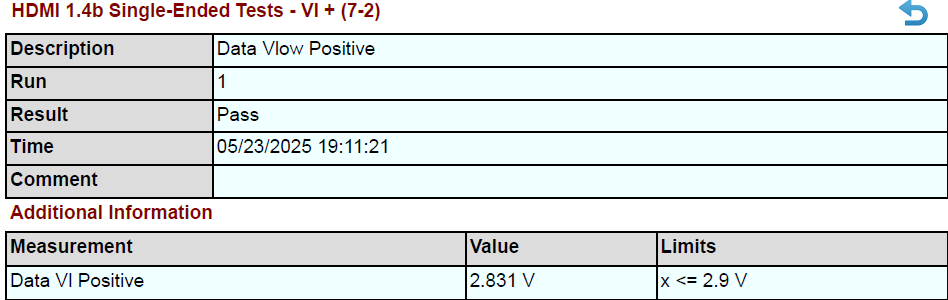

Vl+ 与Vl- (7-2) 数据线单端低电平

示波器采用串行码型触发,捕获1000次以上的Data+ 和Data-的H-L-L-L码型,再用直方图统计H-L-L-L码型中后面两个L电平的样点最大概率值(峰值),即得到Vl+和Vl-。

测试报告结果摘录如下:

若像素时钟频率 ≤165Mhz,且2.7V ≤ Vl ≤ 2.9V之间,则测试通过。

若像素时钟频率 >165Mhz,且2.6V ≤ Vl ≤ 2.9V之间,则测试通过。

以上测试中,像素时钟频率为148.5Mhz,且Vl+ (2.831V)和Vl- (2.787V),处于2.7V ≤ Vl ≤ 2.9V之间,测试判定为通过。

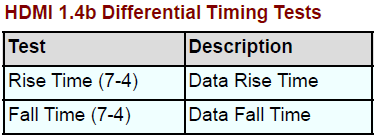

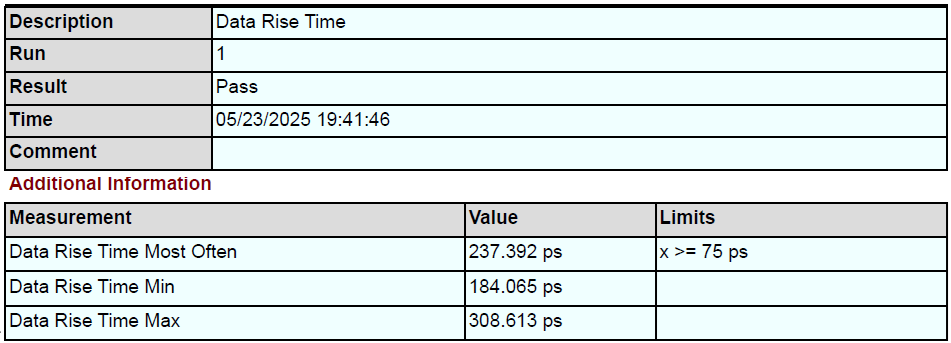

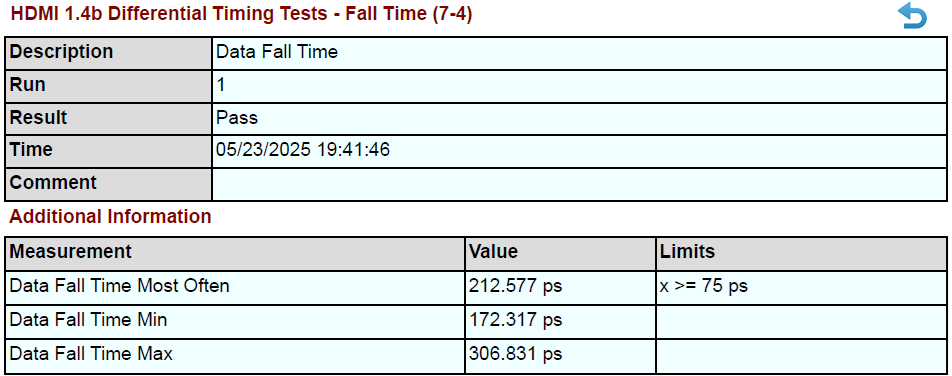

5. 数据Differential Timing Tests (差分接法)

这个测试组的测量项包含差分数据线的Rise Time和Fall Time(7-4)。

其连接方式是仅采用一个差分探头的差分接法。

测试过程这里不再赘述,三对数据线D0/D1/D2分别连接测试一次即可。

如果Trise 和Tfall ≥75ps,则测试通过。软件会自动统计所捕获波形的所有上升和下降沿信息,最终给出Most often和Max/Min的结果。

测试报告结果摘录如下:

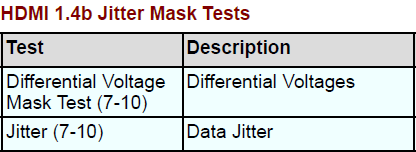

6. 数据Jitter Mask Tests (时钟-数据差分接法)

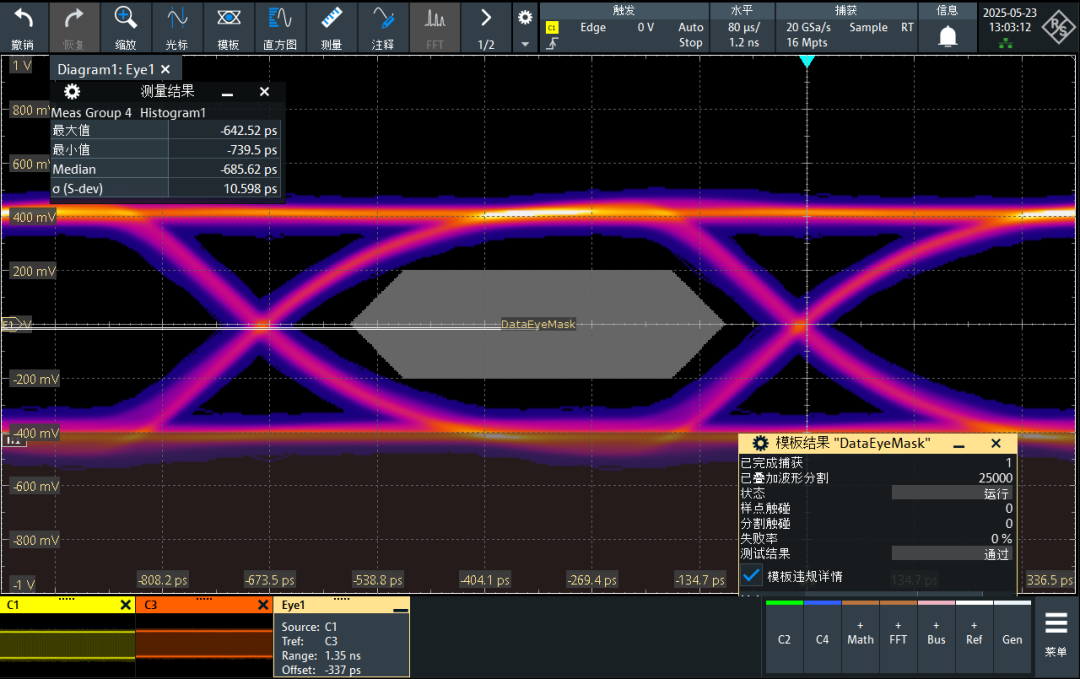

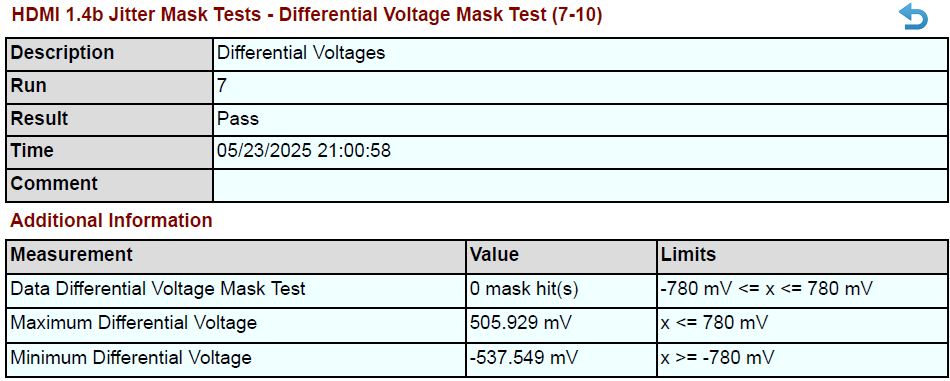

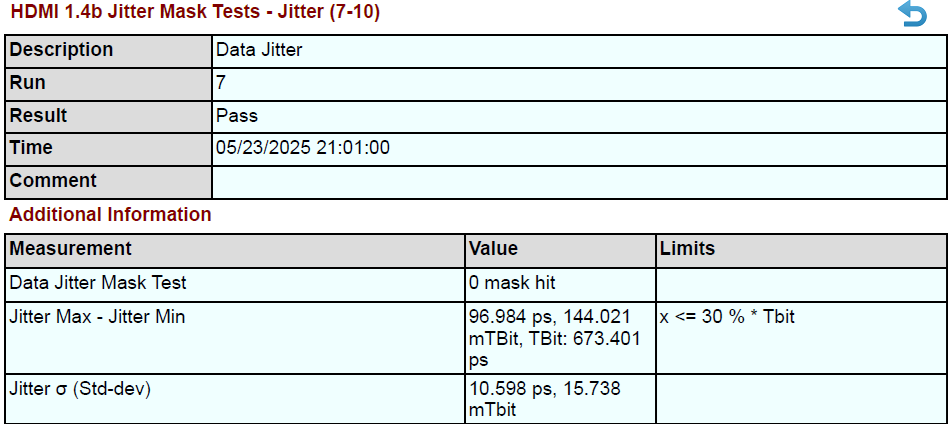

这个测试组的测量项包含Differential Voltage Mask Test 和Jitter (7-10) 差分电压眼图模板测试与数据抖动。

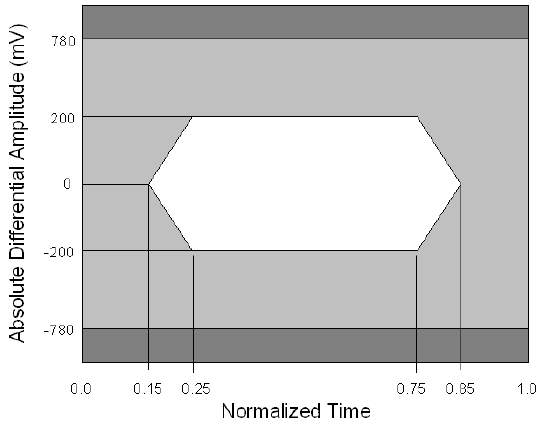

眼图模板测试是验证TMDS数据差分信号电压波形是否符合规范的核心测试项,主要用于确保信号在传输过程中的差分电压Vdiff和时序特性满足眼图模板要求。波形的任何部分都不能擦碰模板。

DMI1.4b CTS规范要求眼图测试过程中,示波器存储深度需要设置到16Mpts。此外对于示波器采样率也有要求,当TMDS时钟≤165MHz,ADC采样率设置为10GSa/s;当TMDS时钟>165MHz,采样率设置为20GSa/s。

测试过程中,示波器会自动捕获HDMI的时钟线上的信号,按照HDMI规定的时钟恢复方法通过10倍频从像素时钟中恢复出数据线的比特时钟,并以这个时钟为基准对数据线上的信号进行叠加形成眼图,该眼图与归一化眼图模板进行比较。如果眼图的任何部分大于780mV或<-780mV,则测试失败。

眼图模板可以在水平方向上向左、向右移动共计1个Tbit的位置,查看是否有某个水平位置让菱形模板与信号眼图没有任何擦碰,但不允许在垂直方向做任何移动。如果移动模板之后无法找到任何符合条件的水平位置,则眼图模板测试判定为失败。

数据抖动则是在数据差分信号眼图的零点交叉附近做水平方向的直方图,统计样点的抖动数据。如果抖动峰峰值(Pk-Pk)>0.3Tbit,则测试判定为失败。

其测试连接是TMDS差分时钟和一路差分数据的双探头差分接法,测试过程这里不再赘述,三对差分数据线D0/D1/D2分别和差分时钟配合起来各测试一次即可。

以下是此项测试生成的数据信号眼图:

测试报告结果摘录如下:

差分电压都在-780Mv~780mV之间,测试通过。

数据抖动的峰值为96.984ps,小于0.3*Tbit(202.02ps),测试通过。

数据抖动的峰峰值为96.984ps,小于0.3*Tbit(202.02ps),测试通过。

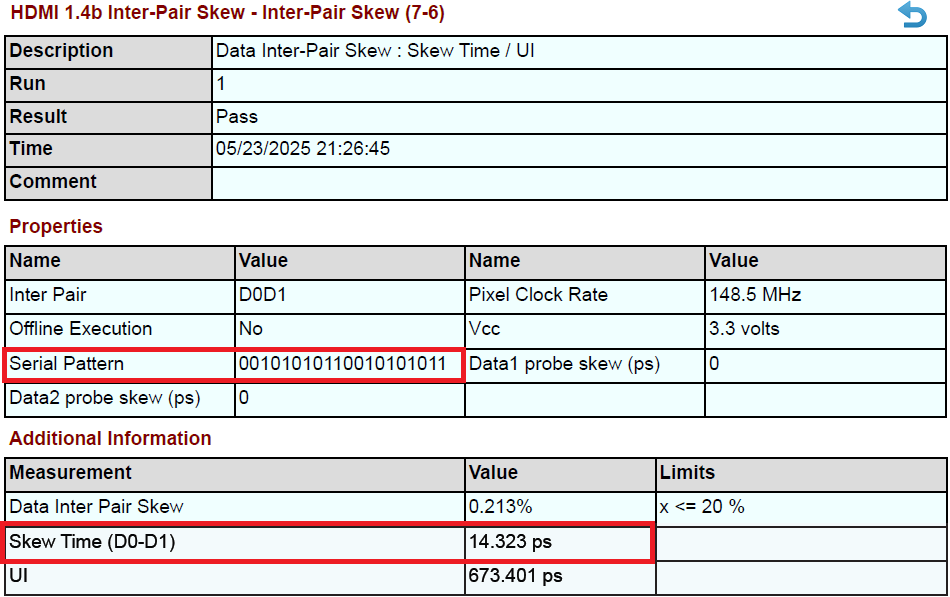

7. 数据Inter-Pair Skew (两路数据差分接法)

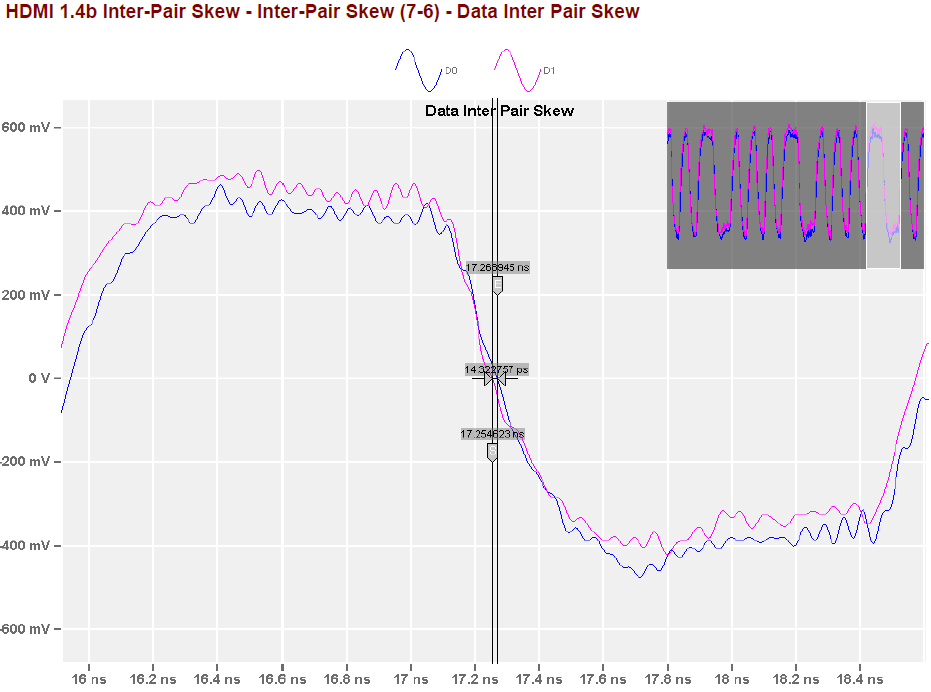

Inter-pair Skew(7-6)数据差分线对间偏移:

测量TMDS三组数据差分信号D0/D1/D2之间的时间偏移, 即D0-D1、D1-D2、D0-D2 这三组的对间偏移Tskew。如果Tskew>0.2*Tcharacter,则测试判定为失败。

这里的Tcharacter 是指TMDS 数据通道传送单个 TMDS 字符的持续时间,等于 10Tbit。

以下是D0-D1的测试连接图:

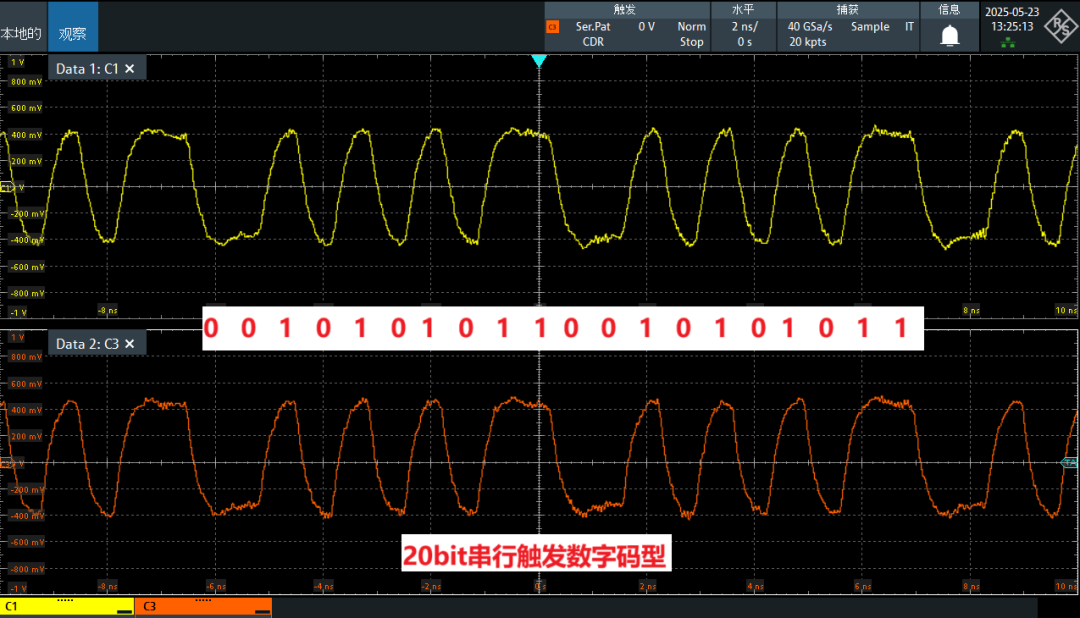

这个测试采用示波器的串行码型触发功能(Serial Pattern Trigger)功能,触发的是20比特的数字码型“00101010 11001010 1011”。

我们也可以从示波器屏幕上看到触发到的码型波形如下:

示波器软件会自动比对D0和D1两路数据差分信号的Skew时延:

测试报告结果摘录如下:

D0-D1的对间偏移位14.323ps,远小于0.2*Tcharacter =0.2*673.401*10=1346.802ps, 因此该项测试判定为通过。

罗德与施瓦茨业务涵盖测试测量、技术系统、网络与网络安全,致力于打造一个更加安全、互联的世界。 成立 90 多年来,罗德与施瓦茨作为全球科技集团,通过发展尖端技术,不断突破技术界限。公司领先的产品和解决方案赋能众多行业客户,助其获得数字技术领导力。罗德与施瓦茨总部位于德国慕尼黑,作为一家私有企业,公司在全球范围内独立、长期、可持续地开展业务。

-

罗德与施瓦茨引领3GPP关键任务通信服务设备一致性2024-07-15 1992

-

罗德与施瓦茨通过NTN NB-IoT射频和无线资源管理一致性测试用例的TPAC认证2024-05-23 1823

-

罗德与施瓦茨推出两种用于5G RF和RRM一致性测试的测试系统2024-02-28 2190

-

罗德与施瓦茨将提供超宽带(UWB)物理层一致性测试工具2022-07-06 3670

-

罗德与施瓦茨TS-RRM-NR 5G一致性测试系统介绍2022-05-26 3105

-

罗德与施瓦茨推出以太网电缆自动化测试解决方案2022-03-31 2670

-

GRL联手罗德与施瓦茨于德国建立先进的高速数字一致性测试实验室2021-11-05 1963

-

罗德与施瓦茨宣布新的IEEE 802.3ch MultiGBASE-T1汽车以太网标准一致性测试解决方案2021-04-16 2996

-

罗德与施瓦茨提供的首批5G NR协议一致性IMS测试用例通过PTCRB验证2021-02-19 2090

-

高速串行总线的物理层一致性测试是什么?由来呢?2019-08-12 3375

-

探讨发送端物理层一致性测试的含义,要素及目标和趋势2018-04-25 6932

-

罗德与施瓦茨公司的R&S BTC广播电视测试系统支持一致性测试2015-09-29 2587

-

罗德与施瓦茨成为第一个完成RCS5.1一致性测试用例认证的测试测量厂商2015-08-18 2403

-

泰克推出HDMI 2.0一致性测试及调试解决方案2014-06-18 2066

全部0条评论

快来发表一下你的评论吧 !