ADC14X250 14 位 250 MSPS 高速模数转换器(ADC)技术文档总结

描述

ADC14X250器件是一款单片单通道高性能模数转换器,能够将模拟输入信号转换为采样率为250 MSPS的14位数字字。该转换器采用差分流水线架构和集成输入缓冲器,可在 –40°C 至 105°C 的扩展温度范围内提供出色的动态性能和低功耗(在器件的 PCB 封装导热垫上测量)。

集成输入缓冲器消除了来自内部开关电容采样电路的电荷反冲噪声,并简化了驱动放大器、抗混叠滤波器和阻抗匹配的系统级设计。还可以调整缓冲器以校正差分输入信号路径的相位和幅度不平衡,以改善偶阶谐波失真。输入采样时钟分频器提供整数分频比,以简化系统时钟。集成的低噪声基准电压源简化了板级设计,无需外部去耦电容器。输出数字数据通过 32 引脚、5 mm × 5 mm WQFN 封装的 JESD204B 子类 1 单通道接口提供。该ADC14X250采用 1.2 V、1.8 V 和 3.0 V 电源供电。SPI可用于配置与1.2V至3V逻辑兼容的器件。

*附件:adc14x250.pdf

特性

- 分辨率:14 位

- 转换率:250 MSPS

- 性能:

- 输入:240 MHz,–3 dBFS

- 信噪比:70.1 dBFS

- 噪声频谱密度:–151.1 dBFS/Hz

- SFDR:87 分贝

- 非 HD2 和非 HD3 SPUR:–92 dBFS

- 无输入信噪比:71.1 dBFS

- 输入:240 MHz,–3 dBFS

- 功耗:584 mW

- 性能额定温度高达 105°C(导热垫)

- JESD204B 子类 1 单通道串行数据接口,通道速率高达 5 Gb/s

- 缓冲模拟输入

- 差分输入相位和幅度校正

- 输入采样时钟分频器(1,2,4,8分频)

- 4线串行外设接口(SPI)

- 32引脚WQFN封装(5×5 mm,0.5 mm间距)

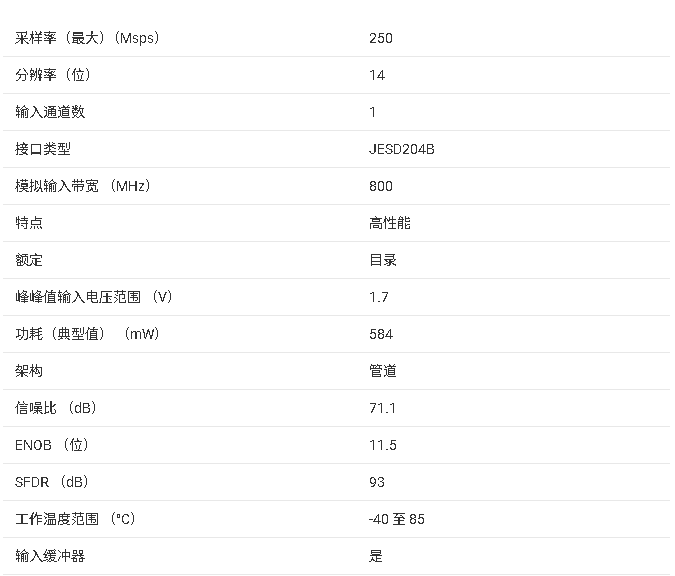

参数

方框图

ADC14X250 是德州仪器(Texas Instruments)推出的一款单通道高速高精度模数转换器,核心优势是兼具高采样速率与优异动态性能,采用 JESD204B 串行接口简化数据传输,适用于通信、雷达、测试测量等对速度和精度要求严苛的高频应用场景。

一、核心性能与定位

- 分辨率与采样速率 :14 位分辨率,最高 250 MSPS 采样率,支持 1/2/4/8 倍输入时钟分频,适配不同系统时钟方案。

- 动态性能 :240 MHz 输入、-3 dBFS 条件下,SNR 达 70.1 dBFS,SFDR 为 87 dBFS,噪声谱密度低至 - 151.1 dBFS/Hz;3 dB 带宽达 800 MHz,支持高频信号直接采样。

- 功耗与温度适应性 :典型功耗 584 mW,工作温度范围 - 40℃~105℃(热焊盘测量),结温最高 125℃,满足严苛环境应用需求。

二、关键功能与硬件特性

1. 信号处理与校正

- 集成模拟输入缓冲器,减少电荷回馈噪声,简化驱动放大器和阻抗匹配设计;

- 支持差分输入幅相不平衡校正,优化二次谐波失真(HD2)性能;

- 内置数字高通 IIR 滤波器,可配置 4 种低频频带,用于去除 DC 偏移。

2. 接口与封装

- 数字输出:JESD204B 子类 1 单通道串行接口, lane 速率最高 5 Gb/s,支持 8b/10b 编码、扰码功能;

- 配置接口:4 线 SPI 接口(兼容 1.2V~3V 逻辑),支持寄存器读写和设备配置;

- 封装规格:32 引脚 WQFN 封装(5mm×5mm,0.5mm 引脚间距),底部裸露热焊盘,优化散热性能。

3. 时钟与同步

- 差分时钟输入(CLKIN±),内置 100Ω 差分端接,支持 AC/DC 耦合;

- 提供 SYSREF 信号接口,实现 JESD204B 链路确定性延迟,支持周期性、间隙周期性和单脉冲 SYSREF 信号;

- SYNCb 差分同步输入,用于 JESD204B 链路初始化和重同步。

三、工作模式与配置

- 电源模式 :支持正常、掉电和休眠模式,掉电 / 休眠模式降低功耗至 38 mW,休眠模式唤醒无需重新校准;

- 数据格式 :默认二进制补码输出,可通过 SPI 配置为偏移二进制格式;

- 测试模式 :支持 PRBS7/15/23、斜坡、K28.5 等多种测试图案,便于系统调试。

四、典型应用场景

- 高中频采样接收机、多载波基站接收机(GSM/EDGE、LTE、WiMax 等);

- 分集 / 多模 / 多频带接收机、数字预失真(DPD)系统;

- 软件无线电(SDR)、雷达、测试测量仪器、便携式仪表。

五、设计关键要点

- 电源与去耦 :需为 VA3.0(3V)、VA1.8(1.8V)、VA1.2(1.2V)电源配置 0.1μF+0.01μF 去耦电容,BP2.5 引脚需额外并联 10μF 电容,电容均靠近引脚布局;

- 信号接口:模拟输入推荐差分端接 50Ω~200Ω,需设计抗混叠滤波器;串行输出 lanes 采用 100Ω 差分传输线,AC 耦合至接收设备;

- 时钟设计:CLKIN 信号需保证低抖动和足够边沿斜率(建议≥1 V/ns),SYSREF 与 CLKIN 需满足时序要求以实现确定性延迟;

- 校准与初始化:上电后自动完成 ADC 核心校准,更改采样率或时钟分频比后需手动重新校准。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC14DC080 双通道14位80MSPS模数转换器技术文档总结2025-11-24 1033

-

ADC3548/ADC3549 单通道高速模数转换器(ADC)产品文档总结2025-10-23 904

-

ADC14X250单片单通道高性能模数转换器数据表2024-07-18 576

-

ADS5424 14位、105 MSPS模数转换器(ADC)数据表2024-07-16 834

-

采样速率高达250 MSPS的模数转换器——AD96422023-04-14 1996

-

AD9643BCPZ-250双通道模数转换器ADC介绍2023-02-14 1583

-

AD9613:12位,170 MSPS/210 MSPS/250 MSPS,1.8 V双模数转换器(ADC)数据表2021-04-30 1175

-

AD9643:14位,170 MSPS/210 MSPS/250 MSPS,1.8 V双模数转换器(ADC)数据表2021-04-16 1170

-

AD9683:14位、170 MSPS/250 MSPS、JESD204B模数转换器2021-03-19 1111

-

AD9284-250EBZ用于仪表的8位,250MSPS模数转换器2019-08-12 1435

-

ADI推出双通道14位250 MSPS模数转换器AD92502012-10-19 4476

-

德州仪器推出业界最低功耗250 MSPS 14位ADC2009-12-04 1678

全部0条评论

快来发表一下你的评论吧 !