DAC7563T 12 位双通道电压输出数模转换器(DAC)技术文档总结

描述

DAC856xT、DAC816xT 和 DAC756xT 器件是低功耗、电压输出、双通道、分别为 16 位、14 位和 12 位数模转换器 (DAC)。这些器件包括一个2.5V 的4 ppm/°C 内部基准电压源,提供 2.5 V 或 5 V 的满量程输出电压范围。 这 内部基准电压源的初始精度为 ±5 mV,可在 V 精炼 /V转折针。

*附件:dac7563t.pdf

这些器件是单调的,提供出色的线性度并最大限度地减少不需要的代码到代码瞬态电压(毛刺)。它们使用多功能三线串行接口,该接口以高达 50 MHz 的时钟速率运行。该接口与标准兼容SPI™、QSPI™、Microwire 和数字信号处理器 (DSP) 接口。DACxx62T 器件集成了一个上电复位电路,可确保DAC 输出上电并保持在零刻度,直到将有效代码写入器件,而 DACxx63T 器件同样在中等刻度上电。这些器件包含一个掉电功能,可在 550 V 时将电流消耗降低到通常为 5 nA。低功耗、内部基准电压源和小尺寸使这些器件成为便携式电池供电的理想选择 设备。

DACxx62T 器件可直接插入且功能相互兼容,以及DACxx63T 器件。整个系列均采用 VSSOP-10 和 WSON-10 封装。

特性

- 相对精度:16位时为4 LSB INL

- 低毛刺脉冲:0.1 nV-s

- 双向基准引脚:输入或2.5V输出

- 4 ppm/°C 温度漂移 (典型值)

- 上电复位至零量程或中量程

- 低功耗:5V AVDD 时为 4 mW

- 宽电源范围:2.7 V 至 5.5 V

- 50 MHz SPI,具有施密特触发输入

- LDAC 和 CLR 函数

- 具有轨到轨作的输出缓冲器

- 与DAC8562系列引脚兼容

- 启用 5V TTL I/O

- 封装:WSON-10(3 mm × 3 mm)、VSSOP-10

- 温度范围:–40°C 至 125°C

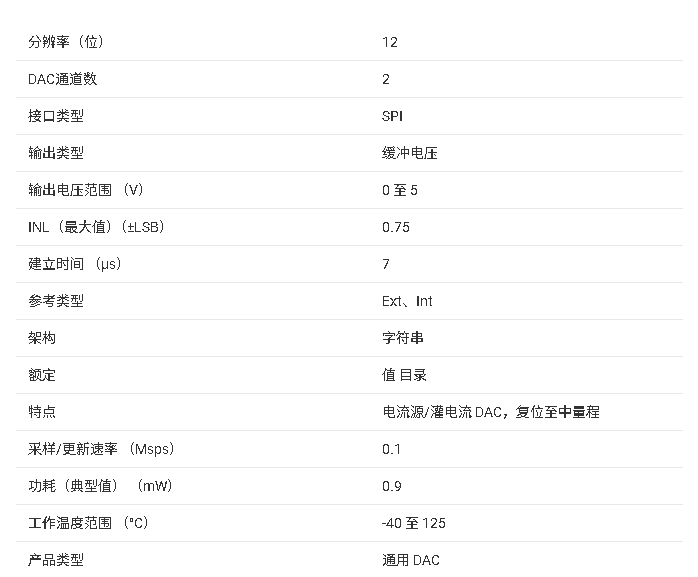

参数

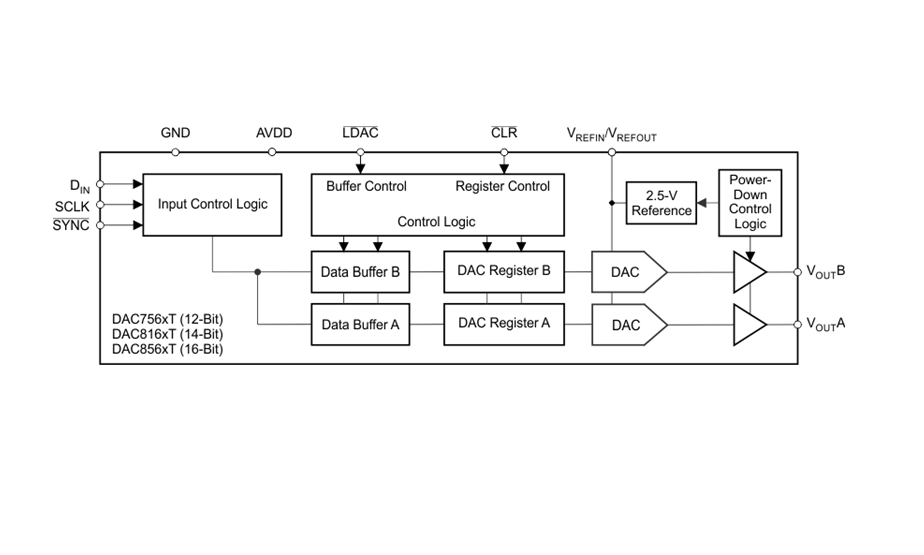

方框图

DAC7563T 是德州仪器(Texas Instruments)推出的一款低功耗、高精度双通道数模转换器,核心优势是内置高稳定基准源与低噪声输出兼具,支持灵活的同步更新与电源管理功能,适用于便携式仪器、PLC 模拟输出模块、闭环伺服控制等对功耗和精度均有要求的场景。

一、核心性能与定位

- 分辨率与线性度 :12 位分辨率,积分非线性(INL)±0.75 LSB,微分非线性(DNL)±0.25 LSB,保证单调性,码间瞬态干扰(毛刺脉冲)低至 0.1 nV・s。

- 基准与输出特性 :内置 2.5 V 基准源,温度漂移仅 4 ppm/°C,初始精度 ±5 mV;输出电压范围 0

AVDD(2.7V5.5V),支持轨到轨输出,满量程输出可通过增益配置实现 2.5V 或 5V。 - 功耗与环境适应性 :5V 供电时典型功耗仅 4 mW,掉电模式功耗低至 550 nA;工作温度范围 - 40℃~125℃,结温最高 150℃,满足工业级环境要求。

二、关键功能与硬件特性

1. 信号输出与控制

- 双通道独立工作,支持同步更新(通过 LDAC 引脚)或异步更新,可实现多通道协同输出。

- 内置输出缓冲放大器,驱动能力强,可驱动 2 kΩ 并联 3 nF 负载,压摆率 0.75 V/μs,满量程建立时间典型值 7 μs。

- 支持清零(CLR)功能,异步清零后输出中点刻度(mid-scale),符合设备上电复位默认状态。

2. 接口与封装

- 数字接口:3 线 SPI 兼容接口,支持 QSPI、Microwire 等标准,最高时钟频率 50 MHz,施密特触发输入提升抗干扰能力。

- 基准接口:VREFIN/VREFOUT 为双向引脚,可作为内置基准输出(2.5V)或外接基准输入,最大源 / 灌电流 20 mA。

- 封装规格:10 引脚 VSSOP 或 WSON 封装(3mm×3mm),WSON 封装带裸露热焊盘,优化散热性能。

3. 电源与功耗控制

- 电源配置:单电源供电(2.7V~5.5V),无需正负电源,简化系统设计。

- 功耗模式:支持 3 种掉电模式(1 kΩ/100 kΩ 接地或高阻态),可单独关闭任一通道以节省功耗,掉电时输出状态可预设。

三、工作模式与配置

- 增益配置 :支持 1 倍或 2 倍增益选择,内置基准启用时默认增益为 2(满量程 5V),外接基准时默认增益为 1(满量程等于基准电压)。

- 更新模式 :同步模式下,数据在第 24 个 SCLK 下降沿更新;异步模式下,通过 LDAC 引脚负边沿触发多通道同步更新。

- 复位与清零 :上电复位默认输出中点刻度(mid-scale);CLR 引脚触发后,输入寄存器与 DAC 寄存器均加载中点刻度,退出清零状态需完成一次完整的 24 位数据写入。

四、典型应用场景

- 便携式仪器、数据采集系统、可编程增益 / 偏移调整;

- PLC 模拟输出模块、电压控制振荡器(VCO)调谐、闭环伺服控制;

- 可通过外部电路扩展为双极性输出(±5V~±15V),适配更多工业场景。

五、设计关键要点

- 电源与去耦 :AVDD 引脚需就近配置 0.1 μF 陶瓷电容和 1 μF 电解电容,基准引脚(VREFIN/VREFOUT)建议并联 150 nF 以上电容滤波,降低电源噪声。

- 信号接口:SPI 信号线需短距离布线,避免与模拟信号线平行;模拟输出端可串联 5Ω~10Ω 电阻抑制寄生振荡,减少负载端反射。

- 基准与增益配置:使用内置基准时,需确保基准引脚负载电流不超过 20 mA;更改增益配置后,建议重新校准输出线性度,确保精度。

- 同步与功耗管理:多通道同步更新时,需先将数据写入缓冲寄存器,再通过 LDAC 引脚触发更新;闲置通道可配置为掉电模式,降低系统总功耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC3154 双通道、10位、500MSPS数模转换器(DAC)技术手册2025-11-14 969

-

DAC8552双通道、电压输出数模转换器(DAC)数据表2024-07-26 864

-

DAC7612双通道、12位数模转换器(DAC)数据表2024-07-19 622

-

DAC2932双通道、12位、电流输出数模转换器(DAC)数据表2024-07-16 578

-

DAC7553 12位双通道数模转换器数据表2024-06-20 513

-

UG-982:评估AD5341 12位、单通道、电压输出、数模转换器(DAC)2021-05-20 998

-

UG-974:评估AD5323 12位双通道电压输出数模转换器(DAC)2021-05-13 1111

-

UG-983:评估AD5342 12位双通道电压输出数模转换器(DAC)2021-05-12 1061

全部0条评论

快来发表一下你的评论吧 !