基于Vishay SiC653A数据手册的技术解析与应用指南

描述

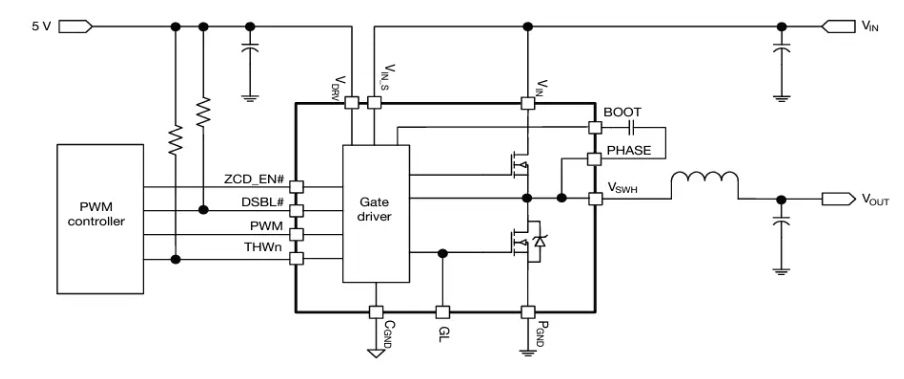

Vishay Semicductors SiC653A 50A VRPower^®^ 集成功率级针对同步降压应用进行了优化,可提供大电流、高效率和高功率密度。Vishay Semiconductors SiC653A采用紧凑型5mm x 5mm MLP封装,可让稳压器每相提供高达50A的持续电流。SiC653A采用Vishay的第四代TrenchFET MOSFET技术,最大限度地降低了开关和传导损耗,从而实现了卓越的性能。其先进的栅极驱动器IC包括大电流驱动能力、自适应死区时间控制、集成自举肖特基二极管、用于温度监控的热警告 (THWn) 和零电流检测,以提高轻载效率。该驱动器支持三态脉宽调制 (PWM)、3.3V和5V 逻辑,并与各种PWM控制器兼容。

数据手册;*附件:Vishay Semiconductors SiC653A 50 A VRPower®集成功率级数据手册.pdf

特性

- 热增强型PowerPAK^®^ MLP55-31L封装

- 第五代MOSFET技术和集成肖特基二极管的低侧MOSFET

- 提供超过50A的持续电流、70A峰值电流 (10ms) 和100A峰值电流 (10μs)

- 95% 峰值效率

- 高达 1.5 MHz 的高频操作

- 优化用于12V输入级的功率MOSFET

- 3.3V和5V PWM逻辑,具有三态和保持功能

- 零电流检测控制功能,可提高提高轻负载效率

- 低 PWM 传播延迟(<20 ns)

- 热监控标志

- 欠压闭锁保护

- 应用包括CPU、GPU和内存的多相VRD

典型应用

基于Vishay SiC653A数据手册的技术解析与应用指南

一、产品核心特性与技术创新

1. 高电流密度与功率集成

- 电流能力:支持50 A连续电流(每相),峰值电流达70 A(10 ms)及100 A(10 μs),适用于多相并联的CPU/GPU供电场景。

- 封装技术:采用5 mm × 5 mm MLP55-31L PowerPAK®封装,通过热增强设计将结到环境热阻(θJA)降至10.6 °C/W。

- 半导体工艺:内部功率MOSFET基于第五代TrenchFET®技术,显著降低开关与导通损耗。

2. 智能化驱动与保护功能

- 集成门极驱动IC:兼容3.3 V/5 V PWM逻辑与三态控制,集成自举肖特基二极管。

- 自适应死区控制:通过监测高边(GH)与低边(GL)门极电压动态调整死区时间,避免直通风险。

- 多重保护机制:

- 欠压锁定(UVLO) :在VDRV低于3.1 V时关闭驱动,确保系统安全启动。

- 热警告标志(THWn) :当结温超过160 °C时触发开漏输出,需外接控制器决策关断。

- 零电流检测(ZCD) :轻载时通过ZCD_EN#引脚切换至二极管仿真模式(DCM),提升效率。

二、关键电气参数与性能曲线解析

1. 效率与功率损耗特性

- 峰值效率:在12 V输入、1.8 V输出条件下可达95 %(图6)。

- 损耗分布:

- 开关频率1 MHz时总损耗约7 W(输出电流50 A)(图7)。

- 损耗随输入电压升高而增加(图8),需优化输入滤波设计。

2. 驱动与逻辑电平兼容性

- PWM阈值:

- 上升沿阈值:2.45 V(典型值)

- 下降沿阈值:0.9 V(典型值)

- 三态电压范围:1.8 V(典型值)

- 传播延迟:

- 高边关断延迟:< 15 ns

- 低边开启延迟:< 12 ns

三、功能模块深度剖析

1. PWM三态工作机制

- 双态逻辑(H/L) :PWM高于2.45 V时开启高边MOSFET,低于0.9 V时开启低边MOSFET。

- 三态逻辑:当控制器PWM输出呈高阻态时,若持续时间超过维持时间(tTSHO),则同时关闭高边与低边MOSFET,避免电感振铃导致的负压振荡。

2. 自举电路与供电设计

- 集成 bootstrap 二极管:仅需外接电容(推荐0402封装)即可生成高边驱动电压。

- VDRV去耦:需在引脚29(VDRV)与引脚28(PGND)间并联2.2 μF陶瓷电容,抑制门极噪声耦合。

3. 散热管理与故障响应

- 热警告阈值:

- 标志置位:结温 > 160 °C

- 标志清除:结温 < 135 °C

- 热增强布局:在VIN与PGND焊盘添加Φ8 mil热 relief 过孔,利用内层铜箔散热。

四、PCB布局核心准则

1. 电源层与去耦优化

- VIN/PGND平面:采用重叠平面设计,多层陶瓷电容(1210/0805/0603/0402)需紧靠器件引脚布局,小容量电容(如0402)应最接近VIN引脚。

- 高频环路控制:VSWH覆铜区域需最小化,避免噪声辐射。

2. 信号完整性保护

- 控制信号路由:PWM、ZCD_EN#、DSBL#等信号线需远离功率节点(如VSWH),推荐在内层布线并用地平面屏蔽。

3. 多相并联布局示例

- 6相拓扑(图28-29):所有SiC653A沿X轴紧凑排列,电感紧贴模块输出端。高电流路径(VIN、VSWH、VOUT、PGND)采用全层覆铜并联,降低阻抗与热阻。

五、典型应用场景与选型建议

1. 适用领域

- 服务器CPU/GPU多相稳压器(VRD)

- 高性能计算与网络设备电源

- 工业自动化大电流直流转换

2. 型号对比

| 型号 | 封装 | PWM逻辑 | 特性 |

|---|---|---|---|

| SiC653ACD-T1-GE3 | MLP55-31L | 3.3 V | 高频优化 |

| SiC653ADB | 参考板 | 5 V | 验证平台 |

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MAX639/MAX640/MAX653高效降压DC - DC转换器:技术解析与设计指南2026-03-19 170

-

Vishay SiC544 40A VRPower®集成功率级技术解析与应用指南2025-11-13 856

-

Vishay SiC32309热插拔电子保险丝开关深度技术解析2025-11-12 746

-

Vishay SiC674A 55A VRPower集成功率级技术解析2025-11-11 727

-

Vishay SiC658A集成功率级技术解析:打造高效能同步降压解决方案2025-11-10 879

-

RKV653KL 数据表2023-05-06 371

-

RKV653KP 数据表2023-05-04 471

-

DC653A DC653A评估板2021-07-30 198

-

DC653A-演示手册2021-05-25 873

-

DC653A-模式2021-04-30 428

-

DC653A-设计文件2021-04-11 384

-

基于SiC414设计的6A降压电源稳压技术2010-04-22 1888

全部0条评论

快来发表一下你的评论吧 !