ADS54J40 14 位双路 1.0-GSPS 高速模数转换器(ADC)技术文档总结

描述

该ADS54J40是一款低功耗、宽带宽、14位、1.0GSPS、双通道模数转换器(ADC)。该器件专为高信噪比 (SNR) 而设计,可提供 –158 dBFS/Hz 的本底噪声,适用于在宽瞬时带宽下实现最高动态范围的应用。该器件支持数据速率高达10.0 Gbps的JESD204B串行接口,每个ADC支持两个或四个通道。缓冲模拟输入在宽频率范围内提供均匀的输入阻抗,并最大限度地减少采样保持毛刺能量。每个ADC通道都可以选择连接到宽带数字下变频器(DDC)模块。该ADS54J40在较大的输入频率范围内以极低的功耗提供出色的无杂散动态范围 (SFDR)。

JESD204B接口减少了接口线的数量,从而实现了高系统集成密度。内部锁相环(PLL)将ADC采样时钟相乘,得出用于序列化每个通道的14位数据的位时钟。

*附件:ads54j40.pdf

特性

- 14位分辨率、双通道、1GSPS ADC

- 本底噪声:–158 dBFS/Hz

- 光谱性能(f

在= 170 MHz,–1 dBFS):- 信噪比:69.0 dBFS

- NSD:–155.9 dBFS/Hz

- SFDR:86 dBc(包括交错音调)

- SFDR:89 dBc(HD2、HD3 和交错音调除外)

- 光谱性能(f

在= 350 MHz,–1 dBFS):- 信噪比:66.3 dBFS

- NSD:–153.3 dBFS/Hz

- SFDR:75 dBc

- SFDR:85 dBc(HD2、HD3 和交错音调除外)

- 信道隔离度:100 dBc(f

在= 170兆赫 - 输入满量程:1.9 V

聚丙烯 - 输入带宽 (3 dB):1.2 GHz

- 片上抖动

- 集成宽带 DDC 模块

- JESD204B支持子类 1 的接口:

- 每个 ADC 2 通道,速率为 10.0 Gbps

- 每个ADC4通道,5.0 Gbps

- 支持多芯片同步

- 功耗:1.35 GSPS 时为 1 W/ch

- 封装:72引脚VQFNP(10 mm×10 mm)

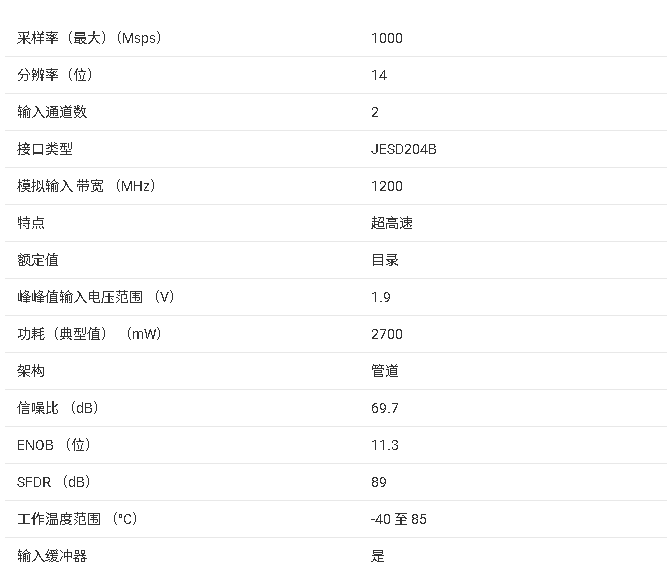

参数

ADS54J40 是德州仪器推出的高速、高精度双通道模数转换器,核心优势是 1.0-GSPS 采样率、14 位分辨率、宽输入带宽及优异的频谱性能,支持 JESD204B 接口与多芯片同步,适用于雷达、宽带无线通信、测试仪器等对高速数据采集和动态范围要求严苛的场景。

一、核心性能与定位

- 精度与频谱性能 :14 位分辨率,噪声基底低至 - 158 dBFS/Hz;170MHz 输入时 SNR 达 68.9 dBFS、SFDR 达 86 dBc(含交织杂散),89 dBc(不含二次 / 三次谐波及交织杂散),通道隔离度 100 dBc,动态范围优异。

- 输入与带宽 :差分输入满量程 1.9 VPP,3dB 输入带宽 1.2 GHz,支持宽频率范围信号采集;内置输入缓冲器,输入阻抗稳定,减少外部驱动电路设计复杂度。

- 速率与功耗 :单通道采样率最高 1.0 GSPS,每通道功耗 1.35 W(1 GSPS 时),支持 2 倍 / 4 倍抽取滤波,平衡速率与功耗需求。

- 环境适应性 :工作温度 - 40℃~85℃,抗静电性能达 HBM±1000V、CDM±500V,满足工业及通信设备可靠性要求。

二、关键功能与硬件特性

1. 集成功能模块

- 内置宽带有源数字下变频器(DDC),支持 2 倍 / 4 倍抽取滤波,提供低通、高通、带通及 IQ 输出模式,可灵活适配不同信号处理需求。

- 支持 JESD204B 串行接口(子类 1),单 ADC 可配置 2 路(10 Gbps / 路)或 4 路(5 Gbps / 路)通道,减少接口线数,支持多芯片同步(SYSREF 信号)。

- 集成交织 mismatch 补偿、DC 偏移校正模块,以及片内抖动功能,提升采样精度与频谱纯净度;提供快速过 range 指示(FOVR),响应延迟仅 18 时钟周期 + 4ns。

2. 工作模式

- 连续采样模式:持续高速采集信号,适用于实时数据传输场景。

- 抽取滤波模式:通过 2 倍 / 4 倍抽取降低输出数据率,提升 SNR 与 SFDR,适配低速后端处理。

- 电源管理模式:支持全局掉电、单通道 ADC / 缓冲器掉电等多档功耗配置,全局掉电功耗低至 0.29 W,兼顾性能与节能。

3. 封装与引脚

- 采用 72 引脚 10mm×10mm VQFNP 封装,含独立模拟电源(AVDD/AVDD3V)、数字电源(DVDD/IOVDD)及接地引脚,热焊盘需连接 AGND 优化散热。

- 引脚包括双路差分模拟输入(INAP/INAM、INBP/INBM)、JESD204B 数据输出(DAxP/DAxM、DBxP/DBxM)、时钟输入(CLKINP/CLKINM)、同步信号(SYSREFP/SYSREFM、SYNC)及 SPI 控制引脚。

三、编程与配置

- 寄存器控制 :通过 SPI 接口访问多页寄存器,配置采样模式、DDC 参数、JESD204B 接口、电源管理及校正功能;支持通道独立配置与广播配置,操作灵活。

- 数据格式与接口 :输出 14 位二进制补码,经 JESD204B 接口串行传输,支持 8b/10b 编码与数据加扰;支持多帧时钟(LMFS)配置,适配不同 lane 数与数据率组合。

- 同步与校正 :SYSREF 信号实现多芯片同步,内置交织补偿、DC 偏移校正模块,支持手动 / 自动校正,可通过寄存器冻结或更新校正参数,适应温度变化带来的性能漂移。

四、典型应用场景

- 雷达与天线阵列、宽带无线通信(DOCSIS 3.1 接收器);

- 通信测试仪器、软件无线电(SDR)、微波接收器;

- 医疗成像、高速数据采集卡(Digitizers)等需要高速、高精度信号转换的设备。

五、设计关键要点

- 电源与去耦 :模拟电源(AVDD 1.9V、AVDD3V 3.0V)与数字电源(DVDD 1.9V、IOVDD 1.15V)需独立供电,各电源引脚就近配置 0.1μF 陶瓷电容 + 10μF 电解电容去耦,减少电源噪声耦合。

- 时钟与同步:采用低抖动时钟源(建议外部时钟抖动尽可能小),CLKIN 差分输入需匹配阻抗;多芯片同步时需保证 SYSREF 信号与采样时钟的时序关系,满足建立 / 保持时间要求。

- 信号接口:模拟输入采用差分布线,长度匹配,串联 5Ω~10Ω 电阻抑制寄生振荡;JESD204B 输出通道需阻抗匹配(100Ω 差分),远离模拟信号路径,减少串扰。

- 布局规范:分离模拟与数字区域,采用完整接地平面;热焊盘可靠接地以优化散热;模拟输入与时钟信号布线避免交叉,减少电磁干扰。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS54J42 14 位 625 MSPS 双通道模数转换器(ADC)技术文档总结2025-11-11 1272

-

ADS54J20 双通道 12 位 1.0-GSPS ADC 核心信息总结2025-11-10 717

-

ADS54J42双通道、14位、625MSPS模数转换器数据表2024-07-29 504

-

ADS54J40双通道14位1.0GSPS模数转换器数据表2024-07-27 590

-

ADS54J20双通道12位、1.0GSPS模数转换器数据表2024-07-26 549

-

AD9208双通道、14位、3 GSPS模数转换器(ADC)英文手册2024-07-17 1085

-

ADS54J60IRMPT模数转换器2019-06-11 897

-

ADS54J40高速ADC和外围电路资料合集免费下载2018-11-19 1002

-

AD9690BCPZ-500 14位 1 GSPS模数转换器(ADC)2018-06-05 1671

全部0条评论

快来发表一下你的评论吧 !