AFE58JD18 16 通道超声模拟前端技术文档总结

描述

该AFE58JD18是高度集成的模拟前端 (AFE) 解决方案,专门用于 专为需要高性能和小尺寸的超声系统而设计。

要索取完整的数据表或其他设计资源:索取AFE58JD18

*附件:afe58jd18.pdf

*附件:afe58jd18.pdf

AFE58JD18共有 16 个通道,每个通道由一个 压控放大器 (VCA),同步采样 14 位和 12 位模数 转换器 (ADC) 和连续波 (CW) 混频器。VCA 包括一个低噪声放大器 (LNA)、一个 压控衰减器(VCAT)、可编程增益放大器(PGA)和低通滤波器 (LPF)。LNA 增益可编程,支持 250mV聚丙烯自 1V聚丙烯输入信号和可编程有源终端。超低噪音 VCAT提供40 dB的衰减控制范围,并改善整体低增益信噪比,从而 有利于谐波和近场成像。PGA 提供 24 dB 和 30 dB 的增益选项。在 ADC的正面,LPF可以配置为10 MHz、15 MHz、20 MHz、 30 MHz、35 MHz 或 50 MHz,支持不同 频率。

该AFE58JD18还集成了低功耗无源混频器和低噪声求和放大器 创建片上 CWD 波束形成器。每个模拟输入可选择 16 个相位延迟 信号。此外,还实现了独特的三阶和五阶谐波抑制滤波器,以 增强 CW 灵敏度

高性能14位ADC可实现75 dBFS SNR。该ADC确保在 低链增益。该器件可以以 65 MSPS 和 80 MSPS 的最大速度运行,提供 14 位 和 12 位输出。

ADC 低压差分信号 (LVDS) 输出支持灵活的系统 小型化系统所需的集成。

该AFE58JD18还包括一个可选的数字解调器和JESD204B数据 12位或14位ADC之后的封装块。数字同相和正交 (I/Q) 解调器 通过可编程小数抽取滤波器,可加速计算密集型算法 低功耗。运行速度高达 5 Gbps 的JESD204B接口进一步减少了电路板布线 高通道数系统面临的挑战。

该AFE58JD18还允许选择各种功率和噪声组合进行优化 系统性能。因此,AFE58JD18是适合两者的超声AFE解决方案 高端和便携式系统。

该AFE58JD18采用 15 毫米× 15 毫米 NFBGA-289 封装(ZBV 封装、 S-PBGA-N289),并指定工作温度范围为 –40°C 至 85°C。 器件引脚排列也类似 到AFE5816设备 家庭。

特性

- 16 通道、完整的模拟前端 (AFE):

- LNA、VCAT、PGA、LPF、ADC和CW混频器

- 具有可编程增益的 LNA:

- 增益:24 dB、18 dB 和 12 dB

- 线性输入范围:0.25 V

聚丙烯, 0.5 伏聚丙烯和 1 V聚丙烯 - 参考输入噪声:

0.63 nV/√Hz、0.7 nV/√Hz 和 0.9 nV/√Hz - 可编程有源端接

- 压控衰减器 (VCAT):40 dB

- 可编程增益放大器(PGA):

24 dB和30 dB - 总信号链增益:54 dB(最大值)

- 三阶线性相位LPF:

- 10 MHz、15 MHz、20 MHz、30 MHz、35 MHz

和 50 MHz

- 10 MHz、15 MHz、20 MHz、30 MHz、35 MHz

- 模数转换器 (ADC):

- 14位ADC:65 MSPS时为75 dBFS SNR

- 12位ADC:80 MSPS时为72 dBFS SNR

- LVDS 接口最大速度为 1 Gbps

- 噪声和功耗优化(全通道):

- 140 mW/Ch,0.75 nV/√Hz,65 MSPS

- 91.5 mW/Ch,1.1 nV/√Hz,40 MSPS

- CW 模式下为 80 mW/Ch

- 出色的器件间增益匹配:

- ±0.5 dB(典型值)和 ±1.1 dB(最大值)

- 低谐波失真

- 快速一致的过载恢复

- CWD 无源混合器:

- 低近相位噪声:

–156 dBc/Hz(1 kHz 时,2.5 MHz 载波) - 相位分辨率:λ / 16

- 支持 16X、8X、4X 和 1X CW 时钟

- CWD 高通滤波器可抑制 1 kHz <不需要的低

频信号

- 低近相位噪声:

- 数字功能:

- ADC后的数字I/Q解调器:

- 分数抽取滤波器 M = 1 至

63,增量步长为 0.25 倍 - 抽取后

数据吞吐量降低 - 片上 RAM,具有 32 个预设配置文件

- 分数抽取滤波器 M = 1 至

- ADC后的数字I/Q解调器:

- 5 Gbps JESD 接口:

- JESD204B 0、1 和 2 子类

- 每个 JESD 通道 2、4 或 8 个通道

- 小封装:15 mm × 15 mm NFBGA-289

参数

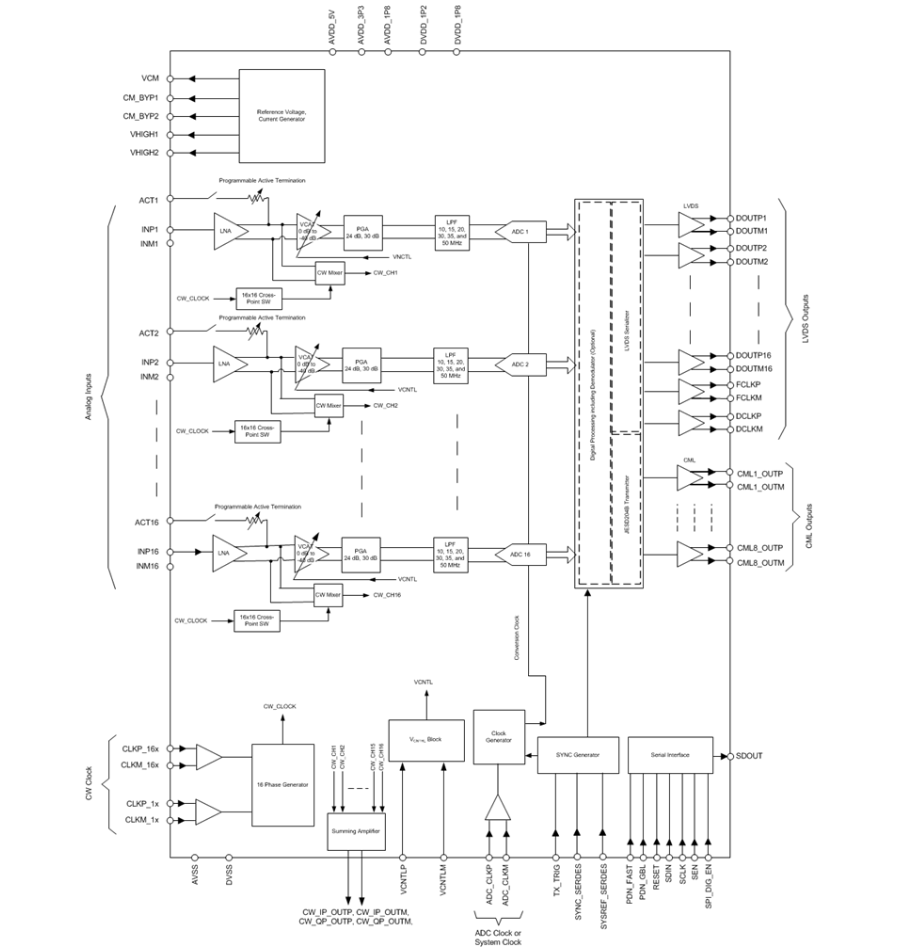

方框图

AFE58JD18 是德州仪器专为超声系统打造的高集成度模拟前端(AFE),核心优势是 16 通道并行采集、宽增益范围(最大 54 dB)、双分辨率 ADC 配置及低相位噪声 CW 模式,搭配 LVDS/JESD204B 双输出接口,适用于医疗超声成像、无损检测、声纳成像等对性能与集成度要求严苛的多通道数据采集场景。

一、核心性能与定位

- 通道与信号调理 :16 通道完整信号链,每通道集成低噪声放大器(LNA)、压控衰减器(VCAT)、可编程增益放大器(PGA)及 3 阶低通滤波器(LPF),总增益最高 54 dB,适配不同超声信号衰减补偿需求。

- ADC 性能 :支持可编程分辨率,14 位模式下采样率 65 MSPS、SNR 75 dBFS;12 位模式下采样率 80 MSPS、SNR 72 dBFS;谐波失真低,过载恢复快速且稳定,保障信号采集完整性。

- 噪声与功耗 :LNA 输入参考噪声低至 0.63 nV/√Hz(24 dB 增益时),线性输入范围可选 0.25 VPP/0.5 VPP/1 VPP;65 MSPS 时功耗 140 mW / 通道,40 MSPS 时低至 91.5 mW / 通道,CW 模式下 80 mW / 通道,平衡性能与功耗。

- 接口与环境 :支持 LVDS(最高 1 Gbps)和 JESD204B 接口(最高 5 Gbps,子类 0/1/2),单 lane 可承载 2/4/8 通道数据;工作温度 -40°C~85°C,满足工业与医疗严苛环境要求。

二、关键功能与硬件特性

1. 集成功能模块

- 灵活信号调理:LNA 增益可选 12 dB/18 dB/24 dB,VCAT 提供 40 dB 衰减范围,PGA 支持 24 dB/30 dB 增益,可精准匹配不同超声探头灵敏度;LPF cutoff 可选 10/15/20/30/35/50 MHz,适配宽频率范围超声应用。

- CW 模式优化:内置无源混频器与 16 相位发生器,支持 1X/4X/8X/16X CW 时钟模式,近载相位噪声低至 -156 dBc/Hz(1 kHz 偏移,2.5 MHz 载波),相位分辨率 λ/16;集成 3/5 次谐波抑制滤波器及 <1 kHz 高通滤波器,提升 CW 多普勒测量灵敏度。

- 数字处理与存储:集成数字 I/Q 解调器、分数抽取滤波器(M=1~63,0.25 增量步进),降低后端数据吞吐量;片上 RAM 存储 32 组预设配置文件,支持快速模式切换,适配多场景应用。

- 一致性与集成:通道间增益匹配典型值 ±0.5 dB、最大值 ±1.1 dB,保证多通道采集一致性;采用 15 mm×15 mm NFBGA-289 封装,引脚布局兼容 AFE5816 系列,便于系统升级与替换。

2. 工作模式

- 脉冲成像模式(TGC 模式):通过 VCAT 与 PGA 实现动态增益补偿,抵消超声信号传播衰减,搭配 LPF 滤除高频噪声,提升深部组织成像质量。

- 连续波模式(CW 模式):针对多普勒血流测量,内置片上波束形成器,16 级相位延迟可实现信号相位校准与叠加,低相位噪声特性保障血流速度测量精度。

- 低功耗模式:ADC 采样率可动态调整,功耗随速率同步优化,非工作时段支持快速掉电(PDN_FAST)与全局掉电(PDN_GBL),适配便携式设备续航需求。

- 校准模式:支持通道增益与相位校准,通过 SPI 接口配置参数,优化多通道一致性,提升成像均匀性。

3. 接口与封装

- 数据接口:LVDS 接口支持点对点高速传输,适配低成本 FPGA;JESD204B 接口减少布线复杂度,5 Gbps 速率降低高通道数系统的板级设计难度。

- 控制接口:通过 SPI 接口(SDIN/SDOUT/SCLK/SEN)配置工作模式、增益、滤波器参数及 ADC 分辨率,支持外部同步(SYNC)与复位(RESET)控制。

- 封装选项:仅提供 NFBGA-289 封装(15 mm×15 mm),焊球材质为 SNAGCU,符合 RoHS 标准,MSL 等级 3(260°C 回流,168 小时)。

三、典型应用场景

- 医疗超声成像:腹部、心血管、产科等超声诊断设备的多通道信号采集;

- 无损检测设备:工业材料缺陷检测、航空航天结构完整性评估;

- 声纳成像:水下目标探测、海洋测绘、水下通信等声纳系统;

- 多通道高速数据采集:其他需要宽增益、低噪声、高集成度的多通道信号调理与数字化场景。

四、设计关键要点

- 供电与去耦 :需按推荐电源轨(1.2 V/1.8 V/3.3 V/5 V)供电,每个通道电源引脚就近配置低 ESR 去耦电容,减少电源噪声耦合,保障低噪声性能。

- 阻抗匹配:LNA 支持可编程有源端接,需匹配超声探头阻抗(50 Ω 左右);JESD204B 接口 lane 需做 100 Ω 差分阻抗匹配,优化高速传输完整性。

- 时序同步:多通道或多芯片工作时,通过 JESD204B 接口的 SYSREF 信号实现同步,确保通道间相位一致性,提升成像或检测精度。

- 散热设计:16 通道并行工作时需合理规划 PCB 散热路径,封装底部热焊盘需可靠接地,避免高温影响性能稳定性。

-

AFE5807 超声模拟前端技术文档总结2025-11-18 1185

-

AFE5803 8 通道超声模拟前端总结2025-11-17 1149

-

AFE58JD16 16 通道超声模拟前端技术文档总结2025-11-11 1545

-

AFE58JD28 技术文档核心内容总结2025-11-07 840

-

AFE58JD32 产品核心信息总结2025-11-06 1781

-

AFE58JD48 12.8 GB JESD204B超声 AFE技术手册2025-11-04 781

-

AFE58JD32LP 32通道超声AFE技术手册2025-11-03 1013

-

AFE58JD32LP 32通道超声波AFE数据表2024-07-31 638

-

AFE5818 16通道超声波模拟前端数据表2024-07-29 749

全部0条评论

快来发表一下你的评论吧 !