开发者必备,10 分钟搞定 RK3588 PCIE 拆分!

描述

前言:

在嵌入式开发中,PCIe 接口的灵活配置直接影响设备扩展能力与性能发挥。RK3588作为旗舰芯片,其 PCIe 拆分机制更是让硬件设计与软件调试拥有了更多可能性。今天这篇技术笔记,就带大家快速吃透 RK3588 PCIE 拆分的核心逻辑、配置步骤与实战技巧,轻松上手!

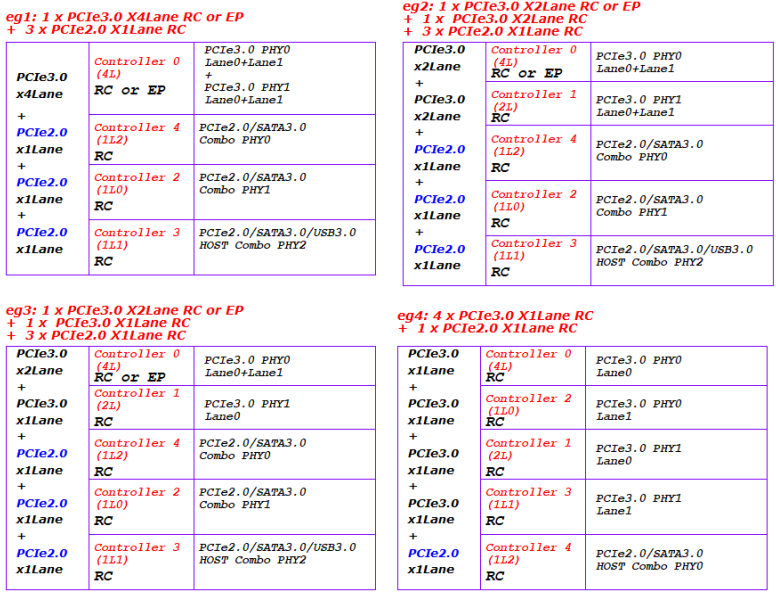

一、RK3588 PCIE拆分映射关系图

PCIE的拆分机制的核心主要在于对于 PCIE PHY 的灵活拆分,并根据实际拆分情况进行PCIE控制器的匹配,从而实现不同 Lane 组合的扩展方案。

RK3588 PCIe 5 个 Controller 和 5 个 PHY 映射关系图:

RK3588 的 PCIe 资源堪称豪华,这也是拆分能力的基础:

5 个 PCIe 控制器:1 个 4Lane DM 模式(支持 RC/EP)、1 个 2Lane RC 模式、3 个 1Lane RC 模式

两类 PHY 资源:PCIe 3.0 PHY(2 个 Port 共 4 个 Lane,支持拆分)+ 3 个 PCIe 2.0 Combo PHY(可与 SATA/USB 共用)

简单说,拆分的本质就是 “把 4 个PCIE 3.0 Lane 按需求拆成不同组合”,比如 4Lane×1、2Lane×2、2Lane+1Lane+1Lane,或是 1Lane×4,再通过设备树(DTS)配置让控制器与拆分后的 Lane 精准对接。

以PCIE 3.0拆分为示例,常见拆分组合直接套用:

4Lane×1:占用 3.0 PHY Port0+Port1 全通道,对接 4Lane 控制器

2Lane×2:Port0、Port1 各占 2Lane,分别对接 4Lane、2Lane 控制器

2Lane+1Lane+1Lane:Port0 占 2Lane,Port1 拆为两个 1Lane,对接 3 个控制器

1Lane×4:Port0、Port1 各拆为两个 1Lane,对接 4 个控制器

注意事项:拆分后若某组 PCIe 未使用,需将其禁用(disabled),但电源必须持续供电,否则会导致 PCIe 异常!

二、实战配置:DTS 配置详解

拆分的核心操作都在设备树(DTS)中完成,无需修改驱动,关键配置分两类:控制器配置和 PHY 配置。

2.1 章控制器常用配置

compatible:指定工作模式(RC/EP),RK3588 需配置为 “rockchip,rk3588-pcie”(RC 模式)或 “rockchip,rk3588-pcie-ep”(EP 模式)

reset-gpios:必配项!设置 PERST# 复位信号,多 Lane 拆分时每个节点需配置不同引脚

num-lanes:Lane 数量,按实际拆分情况配置(如 1、2、4)

phys:指定 PHY 引用,Combo PHY 需同时声明工作模式(如<&combphy1_ps PHY_TYPE_PCIE>)

2.2 PHY 配置核心

PCIe 3.0 PHY 的模式配置是关键,直接决定拆分方式:

&pcie30phy { rockchip,pcie30-phymode =

不同拆分对应的模式参数:

4Lane×1:PHY_MODE_PCIE_AGGREGATION(4)

2Lane×2:PHY_MODE_PCIE_NANBNB(0)

2Lane+1Lane+1Lane:PHY_MODE_PCIE_NANBBI(1)

1Lane×4:PHY_MODE_PCIE_NABIBI(3)

2.3 典型场景配置示例

场景 1:3.0 4Lane RC + 2 个 2.0 1Lane

// 电源配置vcc3v3_pcie30: vcc3v3-pcie30 { compatible = "regulator-fixed"; regulator-name = "vcc3v3_pcie30"; regulator-min-microvolt = <3300000>; regulator-max-microvolt = <3300000>; enable-active-high; gpios = <&gpio3 RK_PC3 GPIO_ACTIVE_HIGH>; startup-delay-us = <5000>; vin-supply = <&vcc12v_dcin>;};// Combo PHY使能&combphy1_ps { status = "okay"; };&combphy2_psu { status = "okay"; };// 1Lane控制器配置&pcie2x1l0 { reset-gpios = <&gpio4 RK_PA5 GPIO_ACTIVE_HIGH>; rockchip,skip-scan-in-resume; status = "okay";};&pcie2x1l1 { reset-gpios = <&gpio4 RK_PA2 GPIO_ACTIVE_HIGH>; pinctrl-names = "default"; pinctrl-0 = <&rtl8111_isolate>; status = "okay";};// 3.0 PHY配置(4Lane模式)&pcie30phy { rockchip,pcie30-phymode = ; status = "okay";};// 4Lane控制器配置&pcie3x4 { reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>; vpcie3v3-supply = <&vcc3v3_pcie30>; status = "okay";};

场景 2:3.0 拆分为 2 个 2Lane + 3 个 2.0 1Lane

核心修改:PHY 模式改为PHY_MODE_PCIE_NANBNB,4Lane 控制器配置num-lanes = <2>,启用 2Lane 控制器(&pcie3x2)。

场景 3:3.0 拆分为 4 个 1Lane + 1 个 2.0 1Lane

核心修改:PHY 模式改为PHY_MODE_PCIE_NABIBI,4Lane、2Lane 控制器均配置num-lanes = <1>,禁用对应 Combo PHY。

三、硬件设计关键要点

软件配置再完美,硬件不匹配也会功亏一篑,这3点必须注意:

1. 物理链路:确保拆分后的 Lane 与控制器的 TX/RX 信号对应,比如 1Lane×4 时,4 个通道需分别连接 PHY 的不同 Lane;RK3588 可支持多种 PCIe 模式的组合,最多可以 5 种模式同时使用。

2. 时钟配置:3.0 的 REFCLKP/N 仅支持输入,4 个 1Lane 拆分时需为每个通道单独提供时钟;2.0 的 REFCLKP/N 支持输入 / 输出,默认由 RK3588 提供;

3. 复位信号:每个拆分节点的 CLKREQ、WAKEN、PERST# 引脚必须独立配置并对应,否则无法稳定建立链路;

四、总结

由此我们可以看到,在RK3588中其PCIe拆分的核心精髓,在于对PCIe 3.0 PHY物理通道的灵活划分,并与对应的控制器进行精准匹配。

成功拆分配置关键在于:

1、硬件设计:需要保证物理链路、时钟、复位信号与拆分之后的通道配置一一对应。拆分本质上其实就是对于PCIE 3.0 PHY进行Lane通道的拆分,并将其与对应的控制器进行匹配和连接。

2、软件设置:需要通过设备树的配置来精确描述硬件链接,核心在于配置好PCIE PHY的相关模式,以及管理好各个控制器节点的复位信号以及使能状态。

通过理解PCIE的资源分配图,了解控制器以及PHYy之间的映射关系,注意DTS设备树的配置方式,便能够在开发过程中快速实现RK3588 PCIE 高速接口方案。

广州眺望电子科技有限公司专注于嵌入式处理器模组的研发与应用,提供从硬件设计到驱动开发,系统解决方案的全流程技术支持。欢迎关注我们的公众号,获取更多嵌入式项目开发实战经验。

-

瑞芯微RK3588开发板RK3588 EVB和RK3588S EVB解读2022-09-22 23267

-

RK3588 PCB推荐叠层及阻抗设计2023-08-10 2056

-

RK3588 EVB开发板原理图讲解【八】 RK3588 power Tree2025-03-01 2330

-

RK3576 vs RK3588:为何越来越多的开发者转向RK3576?2025-05-30 12713

-

RK3588 EVB 开发板介绍2022-03-16 7811

-

RK3588J和RK3588是什么关系?2023-03-13 4896

-

armsom:为何选择rk3588开发与Jetson Nano引脚兼容的嵌入式产品2023-10-18 8902

-

Banana Pi为何选择rk3588开发与Jetson Nano引脚兼容的嵌入式产品2023-11-02 2075

-

瑞芯微Toybrick TB-RK3588X开发板发售!助力开发者高效创新!2022-10-10 4185

-

迅为RK3568/RK3588开发板视频教程 | RKNPU2 从入门到实践一套搞定!2023-06-30 2900

-

rk3588和rk3588s的区别2023-08-15 21135

-

RK3588!黑神话悟空,启动?-迅为电子RK3588开发板2024-08-30 2583

-

三分钟快速上手RK3588开发板2024-11-28 5861

-

一文搞懂 RK3588 PCIe:从硬件资源到拆分配置 + 避坑指南(含脑图)2025-11-20 4866

-

迅为电子RK3568+RK3588开发板资料焕新升级!多维度优化助力开发者效率提升2026-03-26 554

全部0条评论

快来发表一下你的评论吧 !