ADC16DX370 核心产品信息总结

描述

ADC16DX370器件是一款单片双通道高性能模数转换器能够将模拟输入信号转换为采样率为370 MSPS 的 16 位数字字。该转换器采用差分流水线架构,集成输入缓冲器在保持低功耗的同时提供出色的动态性能。

集成的输入缓冲器消除了来自内部开关电容采样电路的电荷反冲噪声,并简化了驱动放大器的系统级设计,抗混叠滤波器和阻抗匹配。输入采样时钟分频器提供整数具有可配置相位选择的分频比,以简化系统时钟。集成低噪声基准电压源简化了板级设计,无需外部去耦 电容器。 输出数字数据通过JESD204B子类 1 接口提供,来自56 引脚、8 mm × 8 mm WQFN 封装。SPI 可用于配置兼容的器件具有 1.2V 至 3V 逻辑。

*附件:adc16dx370.pdf

特性

- 分辨率:16 位

- 转换率:370 MSPS

- 1.7 伏

P-P输入满量程范围 - 性能:

- 输入:150 MHz,–3 dBFS

- 信噪比:69.6 dBFS

- 噪声频谱密度:–152.3 dBFS/Hz

- SFDR:88 分贝

- 非 HD2 和非 HD3 SPUR:–90 dBFS

- 输入:150 MHz,–3 dBFS

- 功耗:800 mW/通道

- 缓冲模拟输入

- 片内精密基准电压源,无需外部旁路

- 具有相位同步功能的输入采样时钟分频器

(除频器为1、2、4或8) - JESD204B 子类 1 串行数据接口

- 通道速率高达 7.4 Gb/s

- 可配置为 1 或 2 通道/通道

- 快速超量程信号

- 4线、1.2V、1.8V、2.5V或3V兼容串行

外设接口(SPI) - 56引脚WQFN封装,(8 × 8 mm,0.5 mm引脚间距)

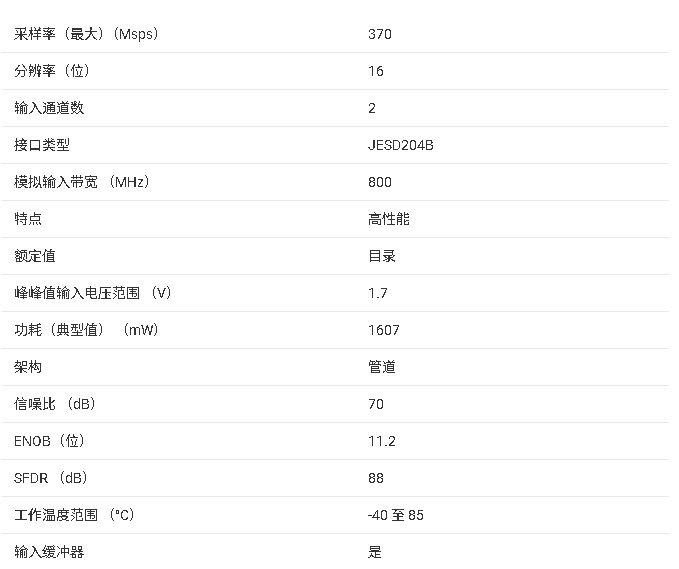

参数

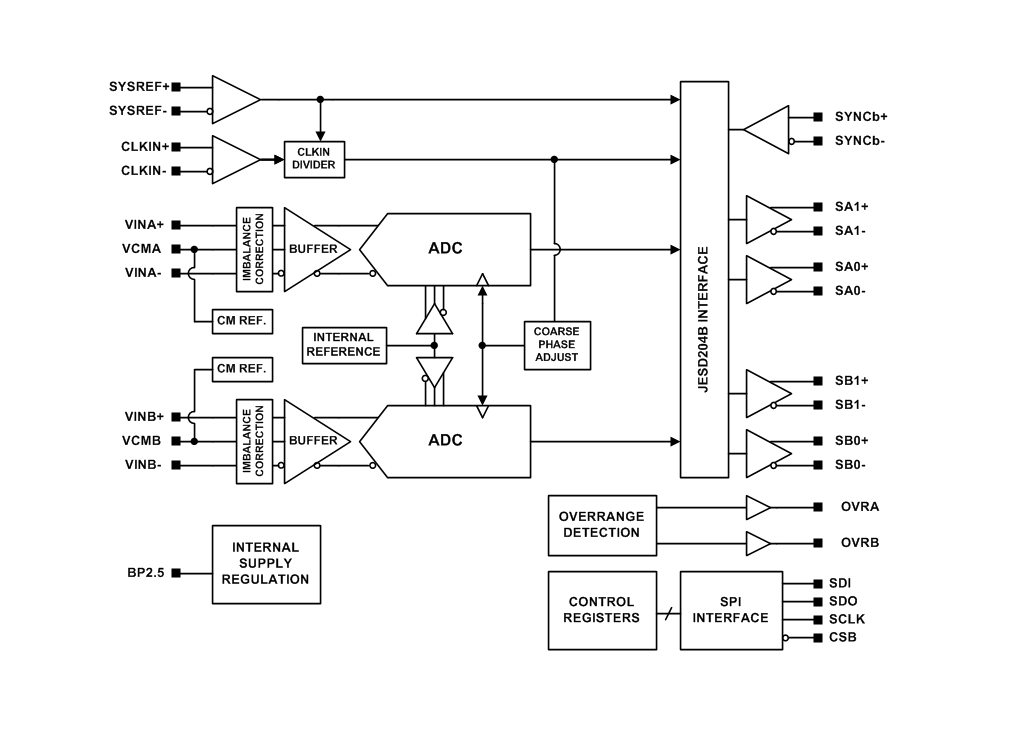

方框图

ADC16DX370 是德州仪器推出的高性能双路 16 位模数转换器(ADC),核心优势为高速采样、高动态性能及标准化 JESD204B 接口,适用于高中频采样接收机、多载波基站、数字预失真等对信号精度和传输速率要求严苛的场景。

一、核心产品参数

1. 基础规格

- 分辨率与通道:16 位分辨率,双路独立通道,每通道支持 1 或 2 路 JESD204B 串行输出 lane

- 采样与数据速率:最高 370 MSPS 采样率,CLKIN 输入频率最高 2000 MHz(分频模式);单 lane 最高 7.4 Gb/s 传输速率

- 封装与温度:56 引脚 WQFN 封装(8.00mm×8.00mm);工作温度 -40°C 至 85°C,结温最高 125°C

- 电源与功耗:多电压供电(1.2V/1.8V/3.0V),单通道典型功耗 800 mW,总功耗典型 1607 mW(单 lane 模式),掉电功耗仅 30 mW

2. 性能特性

- 静态性能:微分非线性(DNL)典型 ±0.65/±0.9 LSB,积分非线性(INL)典型 ±4.5 LSB,无丢失码

- 动态性能:150 MHz 输入、-3 dBFS 时,信噪比(SNR)典型 69.6 dBFS,无杂散动态范围(SFDR)典型 88 dBFS,三阶交调失真(IMD3)典型 -102 dBFS

- 输入特性:差分满量程输入范围 1.7 Vpp,输入带宽 800 MHz,输入电容 3.7 pF,内置 200 Ω 差分终端电阻

- 噪声特性:噪声谱密度(NSD)典型 -152.3 dBFS/Hz,非二次 / 三次谐波杂散典型 -90 dBFS

3. 关键功能参数

- 接口与控制:JESD204B Subclass 1 接口,支持确定性延迟;4 线 SPI 配置接口(1.2V-3.0V 逻辑兼容)

- 时钟与同步:内置时钟分频器(1/2/4/8 分频),支持 SYSREF 信号同步,粗相位调整功能

- 辅助功能:独立通道过范围检测(OVRA/OVRB),输入幅相不平衡校正,DC 偏移校正,8 种输出摆幅(VOD)和去加重(DEM)配置

二、关键功能特性

1. 高速传输与同步

- JESD204B 接口:支持 1 或 2 lane / 通道配置,8b/10b 编码,支持扰码功能,简化多器件同步与数据传输

- 时钟灵活配置:CLKIN 支持 AC/DC 耦合,内置 100 Ω 差分终端,可通过分频器适配高频率时钟输入

- 确定性延迟:通过 SYSREF 信号实现帧时钟与多帧时钟(LMFC)对齐,保证 JESD204B 链路延迟可预测

2. 高动态性能优化

- 输入校正:内置 4 位相位校正和 3 位幅度校正,补偿差分信号幅相不平衡,优化二次谐波失真(HD2)

- 过范围检测:独立通道过范围阈值可编程(-48.16 dBFS 至 0 dBFS),断言延迟仅 7.5 帧时钟周期,支持 0-15 周期保持时间配置

- 低噪声设计:内置高精度参考源(无需外部旁路电容),模拟与数字电源隔离,降低电源噪声干扰

3. 灵活功能扩展

- 测试模式:支持 PRBS7/15/23、斜坡、K28.5、D21.5 等多种测试图案,便于系统调试

- 数据格式:默认二进制补码输出,可选偏移二进制格式,支持 DC 偏移校正(4 档 3-dB 带宽配置)

- 电源管理:支持掉电和睡眠模式,掉电模式恢复需重新校准,睡眠模式快速唤醒无需校准

三、典型应用场景

- 通信系统:多载波基站接收机(GSM/EDGE/CDMA2000/LTE/WiMax)、分集接收、多模多频段接收机

- 测试与测量:高速数据采集设备、通信仪表、便携式测试仪器

- 信号处理:数字预失真(DPD)、中频采样接收机、微波回程链路

四、设计与使用建议

1. 输入与时钟设计

- 输入调理:建议采用差分驱动方案,AC/DC 耦合均可;源阻抗匹配至 50-200 Ω,高频场景可串联 5-10 Ω 电阻抑制谐振

- 时钟配置:CLKIN 输入需保证差分摆幅 250-1000 mV,边沿斜率不低于 2 V/ns;SYSREF 信号需满足与 CLKIN 的建立 / 保持时间要求(320 ps/80 ps)

- 同步配置:多器件同步时启用 SYSREF 脉冲,配置 JESD204B Subclass 1 模式,确保 LMFC 对齐

2. 接口与传输

- JESD204B 配置:根据 FPGA 接口能力选择 lane 数量,单 lane 模式下传输速率 7.4 Gb/s,双 lane 模式下 3.7 Gb/s;建议启用扰码功能降低 EMI

- 输出优化:根据传输距离配置 VOD(0.58V-1.24Vpp)和 DEM(0-6.8 dB),长距离传输优先选择高摆幅和高去加重等级

- SPI 控制:上电后需先配置 SDO 输出逻辑电平(1.2V/1.8V/2.5V/3.0V),再执行读操作;SCLK 频率最高 20 MHz

3. 电源与布线

- 电源配置:严格遵循电源上电顺序(3.0V→1.8V→1.2V 或 3.0V→1.2V→1.8V),各电源引脚就近并联 0.01 μF+0.1 μF 去耦电容,BP2.5 引脚额外并联 10 μF 电容

- PCB 布局:模拟信号与数字信号分区布线,差分线(CLKIN/SYSREF/ 串行 lane)采用 100 Ω 阻抗控制,长度匹配;暴露焊盘需良好接地以优化散热

- 校准与维护:上电后自动校准(约 22.7 ms),修改分频比或采样率后需手动重新校准;宽温场景建议温度变化较大时重新校准以维持性能

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS1148-Q1 核心产品信息总结2025-11-13 693

-

ADC16DX370EVM用户指南2024-12-10 383

-

ADC16DX370 JESD204B串行链路的均衡优化2024-10-09 757

-

ADC16DX370双路16位370MSPS模数转换器(ADC)数据表2024-07-25 466

-

请问能否用KC705 (TSW14J10) 连接ADC16DX370EVM?2019-06-21 1697

-

2017年国微公司产品信息2017-11-24 1641

-

产品信息分类2016-09-27 2191

全部0条评论

快来发表一下你的评论吧 !