DAC3154 双通道、10位、500MSPS数模转换器(DAC)技术手册

描述

DAC3154/DAC3164是双通道 10/12 位、引脚兼容系列,频率为 500 MSPS 数模转换器 (DAC)。DAC3154/DAC3164使用 10/12 位宽 LVDS 数字总线,具有 输入 FIFO。FIFO 输入和输出指针可以在多个设备之间同步,以便 精确的信号同步。DAC输出是电流源,并通过 –0.5 至 1V 的一致性范围。DAC3154/DAC3164 与双通道、14 位、 DAC3174 500 MSPS 数模转换器,以及单通道 14/12-10 位 数模转换器 DAC3171/DAC3161/DAC3151。

这些器件采用QFN-64 PowerPAD封装 在整个工业温度范围(–40°C 至 85°C)内额定。

*附件:dac3154.pdf

特性

- 双通道

- 分辨率

- DAC3154:10 位

- DAC3164:12 位

- 最大采样率:500 MSPS

- 引脚兼容系列,具有DAC3174和

DAC3151/DAC3161/DAC3171 - 输入接口:

- 12位/10位宽LVDS输入

- 内部先进先出

- 芯片到芯片同步

- 功耗:460mW

- 20 MHz IF下的频谱性能

- 信噪比:DAC3154 62 dBFS,DAC3164 72 dBFS

- SFDR:DAC3154 76 dBc,DAC3164 77 dBc

- 当前采购 DAC

- 一致性范围:–0.5V至1V

- 封装:64引脚QFN(9x9mm)

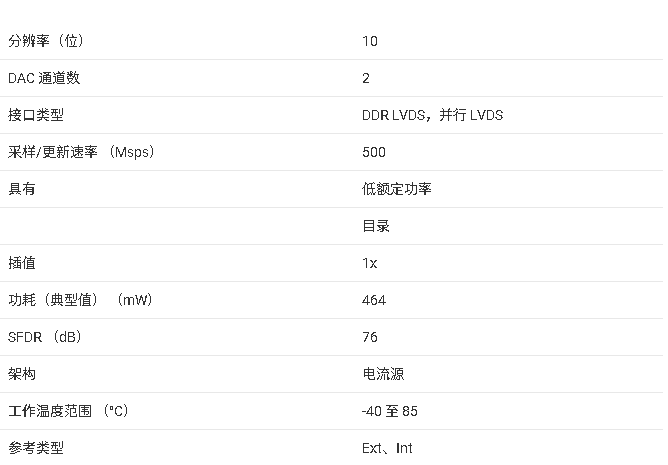

参数

方框图

DAC3154(10 位)与 DAC3164(12 位)是引脚兼容的双通道高速数模转换器(DAC)家族,最高采样率 500 MSPS,支持 LVDS 宽总线输入与多器件同步,具备低功耗、高 spectral 性能特性,专为多载波蜂窝基站、雷达、软件无线电等高频通信与测试场景设计。

核心参数与性能

- 分辨率与采样率 :DAC3154 为 10 位,DAC3164 为 12 位;最高采样率 500 MSPS,支持 DDR/LVDS 输入接口,内置 8 级 FIFO 缓冲。

- 动态性能 :20 MHz 中频输入时,DAC3154 SNR 典型值 62 dBFS、SFDR 典型值 76 dBc;DAC3164 SNR 典型值 72 dBFS、SFDR 典型值 77 dBc;三阶互调失真(IMD3)均≥73.5 dBc(70 MHz 输入)。

- 输出特性 :电流源输出,满量程电流 20 mA,输出 compliance 范围 - 0.5 V 至 1 V;输出电阻 300 kΩ,上升 / 下降时间 200 ps,建立时间 11 ns(0.1% 精度)。

- 功耗与工作条件 :模拟电源(VDDA33)3.15 V-3.45 V,数字 / 时钟电源(VDDA18/CLKVDD18/DIGVDD18)1.71 V-1.89 V;总功耗典型值 464 mW(500 MSPS),睡眠模式功耗低至 26 mW,工作温度 - 40°C 至 85°C。

封装与引脚

- 采用 9 mm×9 mm 64 引脚 QFN(RGC)封装,裸露热焊盘需连接至 PCB 接地平面优化散热。

- 关键引脚包括 LVDS 数据输入(DATA [11:0] P/N)、差分时钟输入(DACCLKP/N/DATACLKP/N)、电流输出(IOUTAP/N/IOUTBP/N)、同步控制(SYNCP/N/ALIGNP/N)及 SPI 配置接口(SCLK/SDIO/SDO/SDENB)。

核心功能与特性

- 灵活输入与同步 :支持双通道 DDR 模式(DATACLK 上升沿传输通道 A、下降沿传输通道 B),内置可编程输入延迟;通过 SYNC/ALIGN 引脚实现多 DAC 精准同步,支持 NORMAL、SYNC ONLY、SIF_SYNC 三种同步模式。

- 低噪声与校准 :内置 1.2 V 参考源(温漂 ±8 ppm/°C),支持外部参考输入;提供通道独立偏移校准(QMC_offset)与增益调整,积分非线性(INL)典型值≤±0.5 LSB。

- 报警与保护 :具备 FIFO 指针碰撞、时钟丢失、数据失配等报警功能,报警状态可通过寄存器或 ALARM 引脚读取; catastrophic 报警时自动关断 DAC 输出,避免错误信号传播。

- 测试与低功耗 :支持 IO 测试模式,可通过寄存器配置 8 组测试图案;提供睡眠 / 掉电模式,单通道睡眠可降低功耗,掉电模式功耗仅 10 mW。

典型应用场景

- 多载波多模式蜂窝基站、雷达系统、信号情报设备、软件定义无线电(SDR)、测试测量仪器、宽带通信发射机。

设计要点

- 电源与去耦 :多电源域需独立供电,各电源引脚就近配置 0.1 μF 陶瓷去耦电容,VDDA33 需额外添加 10 μF bulk 电容,减少电源噪声耦合。

- 时钟与输入设计 :DACCLKP/N(DAC 核心时钟)需 LVPECL 驱动,DATACLKP/N(数据时钟)需 LVDS 驱动,时钟占空比保持 40%-60%;LVDS 输入线对需阻抗匹配(100 Ω),长度误差≤5 mil。

- 布局规范 :模拟地与数字地单点连接,高速 LVDS 走线远离电源路径;热焊盘充分覆铜并通过过孔接地,同步控制引脚(SYNC/ALIGN)走线最短化,避免串扰。

- 配置要点 :通过 SPI 接口配置 FIFO 偏移、输入延迟、同步模式等参数;多器件同步时推荐使用 NORMAL 双同步模式(SYNC 同步写指针,ALIGN 同步读指针),确保相位一致性。

产品型号与供货

- 在售型号包括小卷盘装(250 片 / 卷:DAC3154IRGCT、DAC3164IRGCT)和大卷盘装(2000 片 / 卷:DAC3154IRGCR、DAC3164IRGCR),均符合 RoHS 标准,MSL 等级 3(260°C 回流焊,168 小时湿度敏感)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC3151 10位、500MSPS数模转换器(DAC)技术手册2025-11-14 1268

-

DAC3154/DAC3164双路12/10位500每秒百万次采样(MSPS)数模转换器数据表2024-07-31 566

-

DAC3282双通道16位625数模转换器(DAC)数据表2024-07-27 435

-

DAC5672-EP双通道14位200 MSPS数模转换器数据表2024-07-23 459

-

DAC5687双通道16位高速数模转换器(DAC)数据表2024-07-22 618

-

DAC7612双通道、12位数模转换器(DAC)数据表2024-07-19 623

-

UG-965:评估AD5313R 10位双通道电压输出数模转换器(DAC)2021-05-13 1144

-

高速10位双通道数模转换器DAC1008D750的性能特点和应用2020-08-24 2022

-

DAC3283双通道16位800 MSPS数模转换器的详细资料免费概述2018-05-11 1383

-

德州仪器推出最新款双通道500 MSPS数模转换器2011-11-07 1016

全部0条评论

快来发表一下你的评论吧 !