RK3588平台SSD PCIE调试踩坑记:不插SSD就死机?两步搞定引脚与驱动配置

RK3588平台SSD PCIE调试踩坑记:不插SSD就死机?两步搞定引脚与驱动配置

电子说

描述

最近看好多人因为pcie这个问题困扰,遂再更一版关于pcie调试的文章。

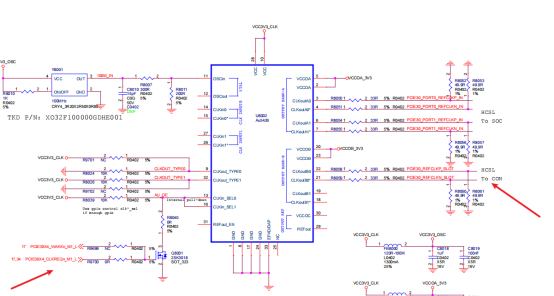

在嵌入式开发中,PCIE 接口的 SSD 因高速读写特性,常作为 RK(瑞芯微)平台的核心存储方案。但调试时难免遇到 “诡异” 问题 —— 比如插入 SSD 时一切正常,不插 SSD 系统就直接起不来,甚至改了配置后还偶发启动失败。

今天结合实际调试文档,拆解这两个典型坑的排查过程与解决方案,帮你避开 PCIe SSD 调试的 “隐形陷阱”。

一、初始坑:不插 SSD,系统直接 “罢工”

1. 现象:插与不插,两种命运

•正常场景:插入 SSD 后,系统启动流畅,SSD 能被正确识别并正常读写;

•异常场景:拔掉 SSD,系统卡在启动阶段,无报错日志,直接 “死机”。

2. 排查:从 “时钟” 定位到 “引脚配置”

一开始怀疑电源或 PCIe 链路问题,逐一排查后发现关键线索:

•测量 PCIe 相关电压(如 vpcie3v3):无论是否插 SSD,电压均稳定在 3.3V,排除电源故障;

•用示波器测 PCIe 时钟信号:不插 SSD 时,时钟引脚无输出,插入后时钟恢复正常—— 问题出在时钟使能的控制逻辑。

进一步核对 DTS(设备树)配置,发现核心控制引脚PCIE30X4_CLKREQn_M1(对应 GPIO4 RK_PB4)的配置存在问题:

|

// 初始错误配置

pcie20x1_0_clkreqn_m1: pcie20x1-0-clkreqn-m1 {

rockchip,pins = <4 RK_PB4 RK_FUNC_GPIO &pcfg_pull_none>; // 浮空状态

};

|

&pcfg_pull_none表示引脚处于浮空状态:插入 SSD 时,SSD 会主动拉低该引脚触发时钟输出;不插 SSD 时,引脚电平悬空,无法触发时钟,导致系统启动卡住。

3. 解决方案:浮空→下拉,让引脚 “有个准信”

只需修改引脚的拉取状态,将“浮空” 改为 “下拉”,确保即使不插 SSD,引脚也能维持稳定电平以触发时钟:

|

// 修改后正确配置

pcie20x1_0_clkreqn_m1: pcie20x1-0-clkreqn-m1 {

rockchip,pins = <4 RK_PB4 RK_FUNC_GPIO &pcfg_pull_down>; // 下拉状态

};

|

重新编译烧录后测试:不插 SSD 时,时钟信号正常输出,系统顺利启动 —— 第一个坑解决!

二、二次坑:改了下拉,仍偶发“死机”

1. 新现象:偶尔启动失败,无规律可循

解决初始问题后,测试中发现新情况:系统约有 10% 概率启动失败,重启几次又能恢复,无固定触发条件,排查难度更高。

2. 根因:驱动加载 “干扰” 引脚电平

再次核对 DTS,发现&pcie3x4(PCIe 控制器节点)中,将之前修改的引脚配置关联到了驱动:

|

// 存在问题的PCIe控制器配置

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

pinctrl-names = "default";

pinctrl-0 = <&pcie20x1_0_clkreqn_m1>; // 引脚关联驱动

status = "okay";

};

|

问题在于:驱动加载时,会动态调整关联引脚的电平,导致PCIE30X4_CLKREQn_M1引脚有时高、有时低,电平不确定性触发 PCIe 链路初始化失败 —— 这也是启动失败 “无规律” 的原因。

查阅 RK 官方原理图与配置说明后确认:该引脚无需关联 PCIe 驱动,需独立控制以保证电平稳定。

3. 终局解决方案:删关联 + 独立配置,彻底稳电平

分两步修改,彻底隔绝驱动对引脚的干扰:

步骤 1:删除 PCIe 驱动与引脚的关联

修改&pcie3x4节点,注释或删除pinctrl-0配置,断开驱动与引脚的绑定:

|

// 修改后的PCIe控制器配置

&pcie3x4 {

reset-gpios = <&gpio4 RK_PB6 GPIO_ACTIVE_HIGH>;

vpcie3v3-supply = <&vcc3v3_pcie30>;

pinctrl-names = "default";

// 注释关联配置:避免驱动干扰引脚电平

// pinctrl-0 = <&pcie20x1_0_clkreqn_m1>;

status = "okay";

};

|

步骤 2:单独配置引脚为 “固定电平调节器”

新增pcie3x4_clkreqn_m1节点,将引脚配置为regulator-fixed(固定调节器)类型,强制拉低并确保启动阶段稳定:

|

// 独立引脚配置(关键)

pcie3x4_clkreqn_m1: pcie3x4-clkreqn-m1{

compatible = "regulator-fixed"; // 固定电平类型

gpio = <&gpio4 RK_PB4 GPIO_ACTIVE_LOW>; // 低电平有效

pinctrl-names = "default";

pinctrl-0 = <&pcie20x1_0_clkreqn_m1>; // 引用下拉配置

regulator-name = "pcie3x4_clkreqn_m1";

enable-active-low; // 使能信号低电平有效

start-delays-us = <5000>; // 启动延迟5000微秒(避免冲击)

off-on-delay-us = <5000>; // 切换延迟5000微秒

regulator-always-on; // 引脚始终保持使能

regulator-boot-on; // 系统启动阶段即开启

};

|

•start-delays-us与off-on-delay-us:避免引脚电平突变导致的链路误判;

•regulator-always-on与regulator-boot-on:确保从系统上电到启动完成,引脚始终维持稳定低电平。

修改后经过百次启动测试:无论是否插 SSD,系统均 100% 正常启动,偶发故障彻底解决!

三、调试核心要点:3 个 “避坑准则”

1.引脚拉取状态:拒绝浮空,优先下拉

PCIe 的CLKREQn类控制引脚(如本文的 GPIO4 RK_PB4),需避免&pcfg_pull_none(浮空),不插设备时会因电平不确定断时钟,下拉(&pcfg_pull_down)是更安全的选择。

2.驱动关联:控制引脚别绑驱动

非 PCIe 核心数据引脚(如时钟控制、复位),无需在&pcie3x4等控制器节点中通过pinctrl-0关联驱动,否则驱动加载会干扰电平稳定性。

3.独立配置:用 regulator-fixed 稳电平

关键控制引脚建议按“固定调节器” 配置,加上延迟参数(如 5000us)和 “始终开启” 属性,从硬件层面杜绝电平波动。

结尾

PCIe 调试常因 “引脚电平”“驱动关联” 这类细节卡壳,看似诡异的故障,往往藏在 DTS 的几行配置里。你在 RK 平台调试 PCIe 设备时,还遇到过哪些 “坑”?欢迎在评论区分享,一起避坑提效!

-

BSP调试#05:MIPI DSI(RK3588)2026-04-17 3623

-

BSP调试#04:HDMI TX(RK3588)2026-04-10 5962

-

BSP调试#03:Ethernet(RK3588)2026-04-03 9981

-

RK3588平台双存储(SPI+PCIE)OTA升级方案教学文档2026-02-01 1767

-

保姆级教程!RK3588 Linux6.1 固件签名完整实现方案(不含rootfs)2026-01-14 2248

-

实战复盘:RK3588 SPI+PCIe3x4方案启动修复,从节点配置到驱动适配全解析2026-01-08 698

-

一文搞懂 RK3588 PCIe:从硬件资源到拆分配置 + 避坑指南(含脑图)2025-11-20 4685

-

开发者必备,10 分钟搞定 RK3588 PCIE 拆分!2025-11-13 1930

-

RK3588 PCIe设备识别失败?一招避坑“非法Class”陷阱2025-08-29 2056

-

Banana Pi BPI-W3 RK3588平台驱动调试篇 [ PCIE篇一 ] - PCIE的开发指南2023-11-02 4727

-

RK3588-MIPI屏幕调试笔记:RK3588-MIPI-DSI2023-06-10 8063

-

RK3588S(Android 12) M.2接口的配置与使用手册指南2022-08-18 4401

-

ROC-RK3588S-PC开发板支持SATA协议的SSD使用2022-07-12 7739

全部0条评论

快来发表一下你的评论吧 !