ADC07D1520 双路 7 位高速模数转换器技术规格与应用总结

描述

该ADC07D1520是一款双通道、低功耗、高性能CMOS模数转换器。该ADC07D1520以高达 1.5 GSPS 的采样率将信号数字化至 7 位分辨率。其功能包括用于系统调试的测试模式输出、时钟相位调整和可选的输出解复用器模式。保证该器件在整个工作温度范围内没有缺失代码。独特的折叠和插值架构、全差分比较器设计、内部采样保持放大器的创新设计以及自校准方案使所有动态参数的响应都超过奈奎斯特,产生高 6.8 有效位数 (ENOB),输入信号为 748 MHz,采样率为 1.5 GHz,同时提供 10^-18^代码错误率 (CER)输出格式为偏置二进制,低压差分信号 (LVDS) 数字输出与 IEEE 1596.3-1996 兼容,但 0.8V 至 1.2V 之间的可调共模电压除外。

*附件:adc07d1520.pdf

每个转换器都有一个可选的输出解复用器,为两个LVDS总线供电。如果选择1:2解复用模式,则每条总线上的输出数据速率将降低到输入采样速率的一半。当选择非解复用模式时,通道DI和DQ上的输出数据速率与输入采样时钟的速率相同。两个转换器可以交错并用作单个 3 GSPS ADC。

该转换器在掉电模式下的功耗通常低于 3.5 mW,采用引线或无铅、128 引脚、热增强型裸焊盘 LQFP,工作温度范围为工业 (–40°C ≤ T 一个 ≤ +85°C)温度范围。

特性

- 单路+1.9V ±0.1V工作电压

- 2倍采样率的交错模式

- 多ADC同步能力

- 调整输入满量程范围、时钟相位和失调

- 选择 SDR 或 DDR 输出时钟

- 1:1 或 1:2 可选输出解复用器

- 第二个DCLK输出

- 占空比校正采样时钟

- 测试模式

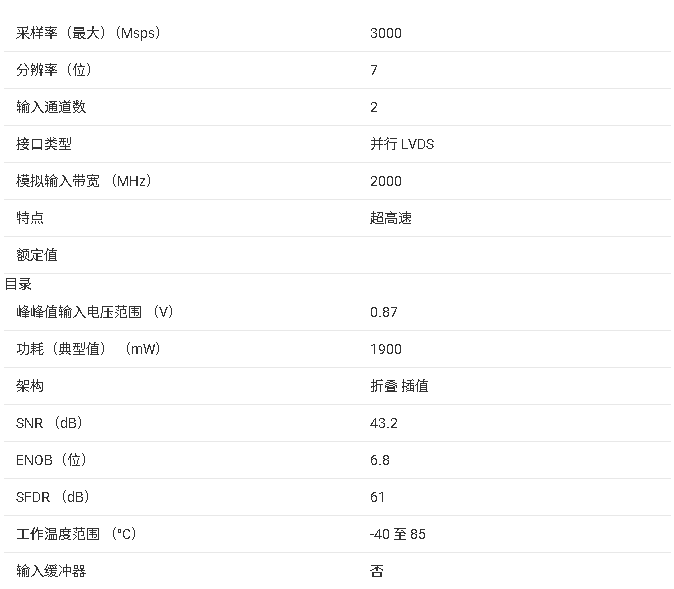

参数

方框图

一、产品概述

ADC07D1520 是德州仪器(TI)推出的低功耗、高性能 CMOS 模数转换器(ADC),核心优势为超高采样率、灵活工作模式与低功耗设计,专为直接射频下变频、数字示波器、卫星机顶盒、通信系统及测试仪器设计。器件采用双路 7 位架构,支持单路 3 GSPS(交错模式)或双路 1.5 GSPS 采样率,通过折叠插值架构与自校准方案实现高动态性能,文档版本为 SLAS881A,发布于 1999-2012 年,采用 128 引脚裸露焊盘 LQFP 封装,工作温度范围 - 40°C 至 85°C。

二、核心参数与性能特性

1. 基础规格

- ADC 性能 :7 位分辨率,无丢失码;差分输入满量程可配置(650 mVpp/870 mVpp),共模输入电压 1.26 V±50 mV;模拟输入带宽最高 2 GHz(非 DES 模式),通道间串扰 - 65 dB。

- 动态性能 :748 MHz 输入时,ENOB 达 6.8 位,SNR 43.2 dB,SFDR 61 dBc,THD 低至 - 60 dB;码错误率(C.E.R.)典型值 10⁻¹⁸,孔径抖动 0.4 ps rms。

- 接口特性 :LVDS 数字输出,兼容 IEEE 1596.3-1996(共模电压 0.8 V-1.2 V 可调);支持 SDR/DDR 输出时钟模式,可选 1:1/1:2/1:4 输出解复用模式。

2. 供电与功耗

- 供电范围 :模拟电源(VA)1.8 V-2.0 V,输出驱动电源(VDR)1.8 V-VA,电源压差≤100 mV。

- 功耗表现 :1:2 解复用模式下典型功耗 1.9 W;断电模式功耗低至 2.5 mW;Q 通道可独立断电,仅 I 通道工作时功耗 1.25 W。

3. 封装与环境适应性

- 封装类型 :128 引脚裸露焊盘 LQFP 封装,结到环境热阻 26 °C/W,结到焊盘热阻 2.8 °C/W,裸露焊盘需焊接至 PCB 接地平面以优化散热。

- 可靠性 :ESD 防护(HBM 2500 V、MM 250 V、CDM 1000 V),存储温度范围 - 65°C 至 150°C,最大结温 130°C,满足工业级长期稳定运行要求。

4. 关键功能特性

- 多工作模式 :支持双沿采样(DES)模式,单通道采样率翻倍至 3 GSPS;非 DES 模式下双路独立工作,1.5 GSPS / 通道;支持 SDR/DDR 输出时钟切换,解复用模式灵活配置。

- 校准与调整 :上电自动校准与手动触发校准,校准周期 1.4×10⁶时钟周期;支持输入满量程(±20%)与偏移(±45 mV)可编程调整,时钟相位精细校准(0.2 ps / 步)。

三、工作模式与功能原理

1. 核心架构

采用 “模拟输入→采样保持→折叠插值 ADC→数字处理→LVDS 输出” 架构,双路 ADC 可独立工作或交错为单路;数字处理模块包含解复用器、校准电路、时钟相位调整单元,LVDS 输出支持多通道同步,通过 DCLK_RST 引脚实现多器件同步。

2. 主要工作模式

| 模式 | 核心配置 | 关键参数 | 适用场景 |

|---|---|---|---|

| 双路非 DES 模式 | 双路独立 1.5 GSPS 采样 | 解复用后输出速率 750 MHz / 通道 | 双路高速数据采集 |

| 单路 DES 模式 | 双路交错采样,3 GSPS 总速率 | 1:4 解复用后输出速率 750 MHz | 超高速率单路信号采集 |

| 断电模式 | 全器件或 Q 通道断电 | 功耗低至 2.5 mW | 低功耗待机场景 |

3. 关键功能细节

- 模式控制 :DES 模式通过引脚或寄存器启用,支持 I/Q 通道选择;解复用模式可配置 1:1(非解复用)、1:2、1:4,降低输出数据率以简化后级处理。

- 校准功能 :校准覆盖输入终端电阻微调、满量程误差、偏移误差、DNL/INL 优化,需在电源稳定后或温度显著变化时重新校准。

- 同步与触发 :支持单端 / 差分 DCLK_RST 信号,实现多 ADC 同步;提供测试模式输出,便于系统调试。

四、应用场景与设计建议

1. 典型应用领域

- 直接射频下变频系统、高速数字示波器、卫星通信机顶盒、无线通信基站、高精度测试仪器、高速数据采集系统。

2. 设计关键要点

- 电源设计 :模拟与数字电源独立布线,每个 VA/VDR 引脚就近并联 0.1 µF 陶瓷电容与 33 µF 钽电容;电源间建议串联铁氧体磁珠,抑制数字噪声耦合。

- 输入与时钟设计 :模拟输入需差分驱动,AC/DC 耦合均可(DC 耦合时共模电压需匹配 VCMO 输出);时钟输入为差分 AC 耦合,支持 LVDS/LVPECL 信号,差分幅度 0.4 Vpp-2.0 Vpp,低抖动时钟源可优化动态性能。

- 布线与散热 :PCB 采用单接地平面,模拟、数字、时钟区域严格分区;LVDS 信号线阻抗控制 100 Ω,长度匹配;裸露热焊盘通过过孔连接至接地平面,建议增加铜皮与散热过孔增强散热。

- 配置优化 :根据信号速率选择解复用模式(高速场景选 1:4 解复用);通过 FSR 引脚或寄存器调整输入满量程,平衡 SNR 与失真性能;高温环境下定期触发校准以维持性能。

-

ADC07D1520评估板的FMC接口是HPC的对吗?2024-12-13 481

-

数模和模数转换器2009-09-16 7942

-

基于HMCAD1520高速低功耗模数转换器的评估套件EKIT01-HMCAD15202019-05-05 2484

-

ADC0809模数转换器主要特性2021-12-02 3634

-

模数转换器ADC简介2022-02-17 1800

-

为什么我们需要模数转换器?哪个ADC转换器更好?2023-02-15 1817

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3657

-

ADC08D1520高性能CMOS模数转换器英文手册2023-06-16 646

-

12位高速逐次逼近寄存器(SAR)模数转换器(ADC)2023-09-25 654

-

ADC08D1520 GSPS模数转换器数据表2024-07-16 496

-

ADC07D1520双通道、低功耗、高性能CMOS模数转换器数据表2024-07-17 477

-

ADC08D1520QML-SP高性能CMOS模数转换器数据表2024-07-22 471

-

ADS7863A双路,12位,2MSPS,模数转换器(ADC)数据表2024-07-30 530

-

AD9251:高性能14位双路模数转换器的深度解析2026-04-01 492

-

AD9627:高性能12位双路模数转换器的深度剖析2026-04-02 450

全部0条评论

快来发表一下你的评论吧 !