【产品介绍】Questa One Sim软件

描述

优势

行业领先的高性能多语言仿真器

用于可测性设计(DFT)向量验证的最快仿真器

高性能、高容量的集成调试环境

覆盖率加速功能,助力更快实现覆盖率收敛

智能编译(SmartCompile)和多核仿真技术,全面提升性能

支持通用验证方法学(UVM)、SystemVerilog、VHDL、SystemC及混合语言

集成的可移植激励标准(PSS)引擎

LRM兼容的参考仿真器

原生编译的单核仿真器技术

代码覆盖率和功能覆盖率

支持System Verilog断言(SVA)和属性规范语言(PSL)

先进优化模式下的仿真

热点分析

C代码调试

X态传播动态仿真

与Questa One Sim Xact原生集成

实数建模

在仿真中进行CDC亚稳态注入

一流的功耗敏感验证技术

通用覆盖率数据库和流程

对64位Linux和Windows的支持

平台支持

Windows11(32位和64位)

Linux–x86-RHEL8和9、Rocky8和9、SLES15SP4(32位和64位)

Linux–AARM64RHEL8和9、Rocky8和9

复杂SoC验证

西门子数字化工业软件旗下西门子EDA的Questa One Sim软件是一款专为应对日益复杂的ASIC、SoC和FPGA设计而打造的仿真器。除了庞大的设计规模以及纳入了多个嵌入式处理器和先进互连系统之外,软件场景的增长以及多平台设计所需的可配置性,致使需要一种功能验证解决方案来统一众多的验证功能。此外,上市时间压力在验证项目中起着主导作用。要按计划交付高质量的设计,必须缩短达到覆盖率和质量目标所需的时间,并提高调试效率。

Questa One Sim的强大新技术有助于极大限度提高模块级和子系统级验证的有效性,从而提升整体生产力。Questa One Sim针对SystemVerilog、VHDL和SystemC,利用强有力的全局编译和仿真优化算法,实现了业界领先的性能和容量。

凭借其独特的智能编译(SmartCompile)能力,Questa One Sim支持极快的周转时间和高效的库管理。Questa One Sim使用并行仿真(ParallelSim)保持高性能,而其集成的调试环境提供高性能、高容量的调试,因而能够在运行大量测试时显著提升回归效率。

先进的验证方法学

设计验证是一个复杂而精密的过程。为了提供一流的能力来应对最严峻的验证挑战,Questa One Sim支持广泛的先进验证方法学,包括新的UVM验证标准。设计完整性通过代码覆盖率和功能覆盖率来衡量,其中包括语句、表达式、条件、翻转和有限状态机覆盖率。

基于断言的验证(ABV)通过插入白盒监视器来提高设计质量,白盒监视器允许在调试窗口内主动监视功能正确性。Questa One Sim通过支持SVA结构和PSL来实现ABV。它还通过断言线程查看器提供强大的调试功能。

Questa可移植激励(QPS)是对Questa One Sim的一项特别强大的增强功能。QPS支持Accellera PSS标准,使工程师能够创建抽象的、可重用的测试意图,这些意图可以自动转换到多种验证环境中,包括用于仿真的UVM序列和用于嵌入式软件测试的C代码。

Questa One Sim还将VHDL集成到其业界领先的约束求解器中,使其能够生成更复杂的VHDL约束随机激励。它还支持将VHDL功能覆盖率数据保存为统一覆盖率数据库(UCDB)格式,使VHDL验证成为Questa One Sim的原生组成部分。UVM已整合这些新功能,以增强已广受欢迎的VHDL验证方法学。

借助并行仿真(ParallelSim)提升仿真性能

在高性能优化的基础上,Questa One Sim通过并行仿真(ParallelSim)功能在多个内核上运行仿真,进一步加速仿真过程。该功能提供易于使用的自动分区,可确定合理分区数量以实现理想性能。内置的限定器可确定设计的适配性,从而灵活地仅对适合并行化的设计启用并行仿真(ParallelSim)。

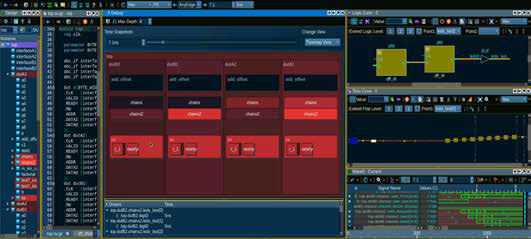

下一代集成调试

Questa One Sim是一个内容感知型集成仿真和调试平台,支持完整的逻辑验证流程。其强大的设计和验证调试功能具有非常直观的特性,可在实时仿真模式或仿真后处理模式下进行调试。Questa One Sim高性能、大容量调试器可快速定位RTL、门级和协议中的错误。它拥有多个为UVM验证平台量身定制的高阶调试窗口。它是基于SystemVerilog类和UVM-aware,即使在当今最复杂的SoC和FPGA上也能缩短总体调试时间。约束调试、X态调试和协议调试等新功能使其成为验证工程师的多用途工具。已完全集成低功耗和UPF调试,并叠加RTL视图。

新的性能分析功能

极大限度提高RTL验证效率通常需要分析仿真运行时的性能,以寻找瓶颈和潜在的可改进之处。Questa One Sim全新、完全重构、直观的性能分析器通过凸显设计或验证平台中性能欠佳且可解决的低效之处,帮助用户自我诊断性能瓶颈。这项新的增强功能支持对单个测试、多个测试甚至整个回归测试进行性能分析。

使用qrun和智能编译(SmartCompile)

的优化流程

Questa One Sim支持旨在显著提高仿真性能的先进优化算法。为了缩短编译、优化和解析周转时间,Questa One Sim支持名为qrun的单个编译命令封装器,其利用智能编译(SmartCompile)功能自动提供增量编译—能够保存和重用预编译部分为预优化设计单元(PDU)并能够保存和重用解析结果。这些功能可以单独或组合使用,以提供定制流程,通过消除不必要的重复处理来缩短周转时间。

X态传播

仿真的主要挑战之一是X态传播。确定传播的X态的来源在验证周期后期需要更多的调试时间,因为工程师必须识别X态的来源、测试设计的初始化并创建显式检查来报告X态。Questa One Sim启用了Xprop的动态仿真包含处理X态传播的机制。其可确保仿真与硅片行为严格匹配,在仿真期间捕获X态的来源,并确保信号解析为已知值(如果可能)。将这些功能与全新的X-Debug功能和热图相结合,可使Questa One Sim调试器实现更高效的X态调试。

实数建模

Questa One Sim支持实数建模。实数建模可以更好地对模拟模块进行建模,并允许这些离散模型用于高性能数字流程中。

借助其他Questa One Sim技术拓展功能

Questa One Sim Power Aware(Questa One Sim PA)支持在RTL级对主动功耗管理进行早期低功耗验证,即使是对于最复杂的设计也是如此。这可确保功耗管理架构和行为正确,并确保设计在主动功耗管理期间正确运行。Questa One Sim PA基于新的行业标准IEEE 1801,支持新的UPF 4.0以及所有用于主动功耗管理的UPF 3.1/3.0/2.1/2.0规范。

在现代SystemVerilog UVM环境中实现覆盖率收敛仍然是一个成本高昂且耗时的过程。Questa One Sim Coverage Acceleration(Questa One Sim CX)是一项覆盖率加速功能,利用创新技术帮助用户更早启动覆盖率收集、更快地提升覆盖率,并以更可预测的方式完成覆盖率收敛。

Questa One Sim DFT Acceleration(Questa One Sim DX)与Tessent Silicon Lifecycle相结合,提供了一个全面的解决方案,可提供sign-off ATPG和MBIST向量验证所需的生产力和性能优势。

Questa One Sim Xact(Sim Xact)通过自动消除烦人的假X态、零延迟竞争条件和库建模错误,同时隔离难以诊断的连接问题,从而更快地调通门级仿真。此外,Sim Xact还支持先进的真实X态根因跟踪工具。

用于功能安全的Questa One Sim Fault Acceleration(Questa One Sim FX)是一款高性能故障仿真器,用于减少随机硬件故障,确保汽车系统的可靠性和安全性。Questa One Sim FX验证设计是否满足ISO 26262汽车安全标准中规定的严格故障注入要求。

Questa One Sim FX也是一款针对DFT的高性能仿真器,用于在DFT中进行功能故障分级,以提高复杂IC的缺陷覆盖率。与市场领先的Tessent TestKompress集成,提供了可实现百万件产品零缺陷的强大解决方案。

-

阿毛FPGA公益学习班第3讲课前视频01--主要内容介绍2013-05-09 5913

-

如何初始化Questa sim env var LM_LICENSE_FILE2018-11-27 3520

-

HackRF One设计介绍2015-12-23 1547

-

工业产品抽屉式SIM卡座SIM-121的详细原理图资料免费下载2018-08-20 2015

-

手机蓝牙和SIM800C中的蓝牙通讯软件免费下载2019-01-17 1092

-

Vivado调用Questa Sim或ModelSim仿真小技巧2021-09-02 10536

-

Questa Sim不支持-novopt问题2022-12-23 7271

-

西门子推出数据驱动型Questa Verification IQ软件 ,助力集成电路验证2023-02-09 1921

-

Vivado调用第三方仿真软件查看波形的过程中存在的一些问题2023-02-10 5632

-

Vivado调用Questa Sim仿真中存在的一些问题2023-05-08 8702

-

NXT4559SIM卡接口级翻译器产品介绍2024-01-03 625

-

西门子推出Questa One智能验证解决方案2025-05-13 1780

-

西门子Questa One验证解决方案引入智能体AI功能2026-03-13 1272

全部0条评论

快来发表一下你的评论吧 !