DAC3162 双通道,12位,500 MSPS 的数字转模拟转换器(DAC)技术文档总结

描述

DAC3152/DAC3162是一种低功耗、低延迟、高动态范围的双通道, 10位/12位引脚兼容的数字转模拟转换器(DAC)系列,采样率同样高 作为500 MSPS。

设备简单(无需软件)、低延迟和低功耗简化了 复杂系统设计。这些DAC与高性能TRF370333模拟设备无缝连接 用于直接上转换架构的正交调制器。

*附件:dac3162.pdf

两个DAC通道的数字数据通过单一LVDS数据总线交错传输,且 芯片内终止。设备的高速输入允许宽带处理 信号。

这些设备被表征为在整个工业温度范围内的工作 温度介于–40°C至85°C之间,采用小型48针7毫米×7毫米QFN封装。

低功耗、小体积、速度、卓越的串扰、简洁且低延迟 DAC3152/DAC3162使它们适合多种应用。

特性

- 低功耗:270毫瓦,500 MSPS

- LVDS输入数据总线

- 交错DDR数据负载

- 高直流精度:±0.25 LSB DNL(10位),

± 0.5 LSB INL(12位) - 低延迟:1.5个时钟周期

- 作简单:无需软件

- 差分可扩展输出:2 mA 至 20 mA

- 片上1.2伏参考

- 1.8伏和3.3伏直流电源

- 节省空间封装:48针7毫米×7毫米QFN接口

- 应用

- 蜂窝基站

- 宽带通信

- 医疗仪器

- 测试与测量

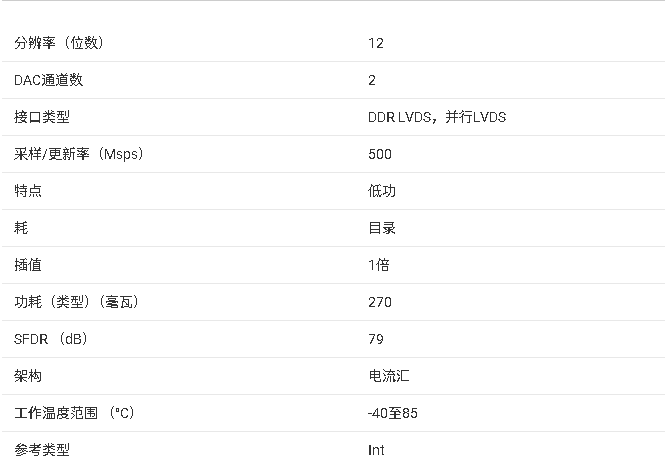

参数

方框图

DAC3152/DAC3162 是德州仪器(TI)推出的引脚兼容双通道高速数模转换器(DAC),分别为 10 位和 12 位分辨率,最高采样率达 500 MSPS,具备低功耗、低延迟、高动态性能特性,无需软件配置,适配蜂窝基站、宽带通信、医疗仪器及测试测量设备,可无缝对接模拟正交调制器实现直接上变频架构。

一、芯片基础信息与核心特性

1. 基础规格

- 型号与定位 :文档编号 SLAS736D,初始发布于 2010 年 11 月,2012 年 8 月修订,DAC3152 为 10 位分辨率,DAC3162 为 12 位分辨率,二者引脚完全兼容。

- 供电与温度 :数字 / 时钟电源 1.7V-1.9V(DVDD18/CLKVDD18),模拟电源 3V-3.6V(AVDD33);工作温度 - 40°C 至 85°C,存储温度 - 65°C 至 150°C。

- 封装形式 :48 引脚 7mm×7mm QFN 封装(型号 RGZ),底部带热焊盘,结到环境热阻 28.9°C/W,适配高密度 PCB 布局。

2. 核心性能指标

- 分辨率与精度 :DAC3152(10 位)的 DNL±0.1 LSB、INL±0.15 LSB;DAC3162(12 位)的 DNL±0.4 LSB、INL±0.5 LSB,增益误差均为 ±1.6% FSR,无失码。

- 动态性能 :500 MSPS 采样率下,SFDR 典型值 78 dBc-79 dBc(10 MHz 输出),IMD3 低至 62 dBc-93 dBc;噪声谱密度(NSD)低至 - 140 dBc/Hz-155 dBc/Hz,相邻信道泄漏比(ACLR)最高 76 dBc。

- 输出特性 :差分电流输出,满量程电流 2 mA-20 mA 可调,输出 compliance 范围 AVDD±0.5 V;输出电阻 300 kΩ,输出电容 5 pF,支持 50 Ω 负载驱动(需配合 RF 变压器)。

- 低功耗与低延迟 :500 MSPS 采样率下功耗仅 270 mW-320 mW,掉电模式功耗 16 mW-25 mW;信号延迟仅 1.5 个 DAC 时钟周期,唤醒 / 休眠时间均为 2 μs。

二、关键功能模块与工作原理

1. 核心功能模块

- 双通道架构 :集成两个独立 DAC 通道(DACA/DACB),通过单路 LVDS 总线接收交织数据(格式为 A0、B0、A1、B1…),数据在 DACCLKP/N 时钟的上升沿和下降沿分别锁存至两个通道。

- 时钟与数据接口 :支持 LVPECL 差分时钟输入(AC 耦合),兼容 LVDS、TTL/CMOS 时钟源;LVDS 数据接口内置终端匹配(85 Ω-135 Ω),数据建立 / 保持时间均为 200 ps,支持 DDR(双沿采样)模式。

- 模拟输出 :每通道提供互补电流输出(IOUTP/IOUTN),通过 BIASJ 引脚外接电阻设定满量程电流(公式:OUT_FS=16×V_BG/R_BIAS);支持通过变压器匹配 50 Ω 负载,1:1 变压器输出 0.5 Vpp,4:1 变压器输出 1 Vpp。

- 灵活控制 :无需软件配置,通过 SLEEPB 引脚控制休眠 / 唤醒(低电平休眠,高电平激活),内部集成 1.2 V 基准源(温漂 ±41 ppm/°C)。

2. 工作原理

- 数字数据以交织格式通过 LVDS 总线输入,由 DDR 时钟(DACCLKP/N)同步锁存至对应通道;内部基准源提供稳定参考电压,通过电阻网络设定输出电流范围;数字信号经 DAC 核心转换为差分电流信号,外部可通过变压器或电阻网络转换为电压信号并匹配负载阻抗。

三、应用场景与设计建议

1. 典型应用

- 通信系统 :蜂窝基站的基带信号生成,与 TRF3703 系列正交调制器对接实现直接上变频,适配 W-CDMA、256-QAM 等调制格式。

- 医疗仪器 :医疗超声等设备的模拟信号生成,满足高带宽、低噪声需求。

- 测试测量 :高速信号发生器的核心模块,提供高保真、高频率模拟输出。

2. 设计注意事项

- 电源与接地 :模拟地与数字地需共地,各电源引脚就近并联 0.1 μF 去耦电容,AVDD33 引脚额外并联大电容降低电源噪声;热焊盘必须焊接至 PCB 接地平面,确保散热。

- 时钟设计 :推荐使用低抖动 LVPECL 时钟源(AC 耦合),差分时钟幅度≥0.2 Vpp;单端时钟需通过电阻网络转换为差分信号,避免时钟抖动影响动态性能。

- 输出匹配 :电流输出需通过 RF 变压器或电阻网络转换为电压信号,匹配 50 Ω 负载;与正交调制器对接时,需通过电阻网络匹配共模电压(1.5 V/1.7 V/3.3 V)。

- ESD 防护 :芯片内置 ESD 防护有限,存储和操作时需将引脚短接或置于导电泡沫中,避免静电损坏。

四、关键应用配置

1. 电源上电序列

- 同时为 DVDD18、CLKVDD18 提供 1.8 V 电源,为所有 AVDD33 引脚提供 3.3 V 电源(可同时上电或任意顺序);

- 提供 DAC 时钟(DACCLKP/N);

- 将 SLEEPB 引脚拉低至少 25 ns 后释放,激活芯片;

- 输入 LVDS 交织数据,芯片开始正常工作。

2. 负载匹配方案

- 50 Ω 负载驱动 :使用 1:1 或 4:1 RF 变压器,变压器初级中心抽头接 AVDD33,实现差分电流到单端电压的转换,同时匹配负载阻抗。

- 正交调制器对接 :通过电阻网络(R1/R2/R3)匹配 DAC 与调制器的共模电压和阻抗,必要时在中间加入基带滤波器抑制镜像信号。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC5688 双通道16位800 MSPS 数字模拟转换器技术文档总结2025-11-26 954

-

DAC3283 双通道 16 位 800 MSPS 数模转换器(DAC)总结2025-11-20 802

-

DAC3152/DAC3162 双通道高速数模转换器技术文档总结2025-11-18 724

-

DAC3151 10位、500MSPS数模转换器(DAC)技术手册2025-11-14 1363

-

DAC7563T 12 位双通道电压输出数模转换器(DAC)技术文档总结2025-11-11 972

-

DAC5672-EP双通道14位200 MSPS数模转换器数据表2024-07-23 478

-

DAC7612双通道、12位数模转换器(DAC)数据表2024-07-19 643

-

DAC3152/DAC3162数模转换器(DAC)数据表2024-06-20 515

-

DAC3152和DAC3162数模转换器的详细资料概述免费下载2018-05-11 1507

-

DUAL12位275 MSPS数字模拟转换器DAC5662的详细资料概述2018-05-10 1994

-

双通道500MSPS数字模拟转换器(DAC)2017-05-18 1231

-

德州仪器推出最新款双通道500 MSPS数模转换器2011-11-07 1028

全部0条评论

快来发表一下你的评论吧 !