AFE7222 宽带混合信号收发器技术文档总结

描述

AFE7225/7222 是一款为全双工或半双工无线电设计的模拟前端。过采样传输12位DAC提供基带到奈奎斯特的输出频率。欠采样接收12位ADC允许基带的模拟输入频率达到~230MHz。AFE7225/7222 内的大多数模块独立控制,以优化功耗与利用率。通过串行接口提供两个辅助控制12位DAC和一个双输入辅助监听12位ADC。数字特性包括QMC(正交调制校正)、插值、减量、均方根/峰值功率计以及带有独立NCO的混频器,用于接收和发射路径。

*附件:afe7222.pdf

AFE7225/7222 提供 64 针 9x9mm QFN 封装(RGC)。AFE7225/7222采用德州仪器的低功耗模拟CMOS工艺制造,并适用于整个工业温度范围(–40°C至85°C)。

特性

- AFE7225

- 双12位250MSPS TX DAC

- 双12位125MSPS RX ADC

- AFE7222

- 双12位130MSPS TX DAC

- 双12位65MSPS RX ADC

- 选项

- 双12位辅助DAC

- 双输入12位辅助ADC

- TX路径插值2或4

- RX路径减2

- 3.0V/1.8V电源,低功率

- 半双工快速唤醒模式

- 粗或细数字混音器

- 正交调制修正

- 时钟输入除法/乘法

- 串行LVDS或交错并行CMOS接口

- 64针QFN封装(9毫米×9毫米)

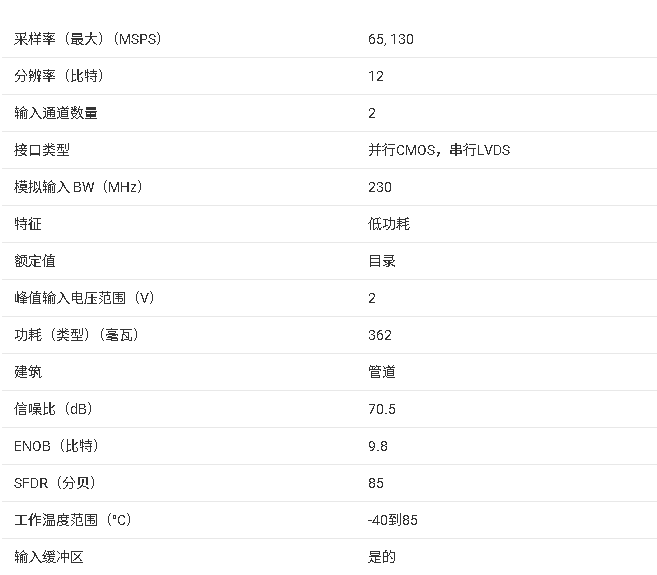

参数

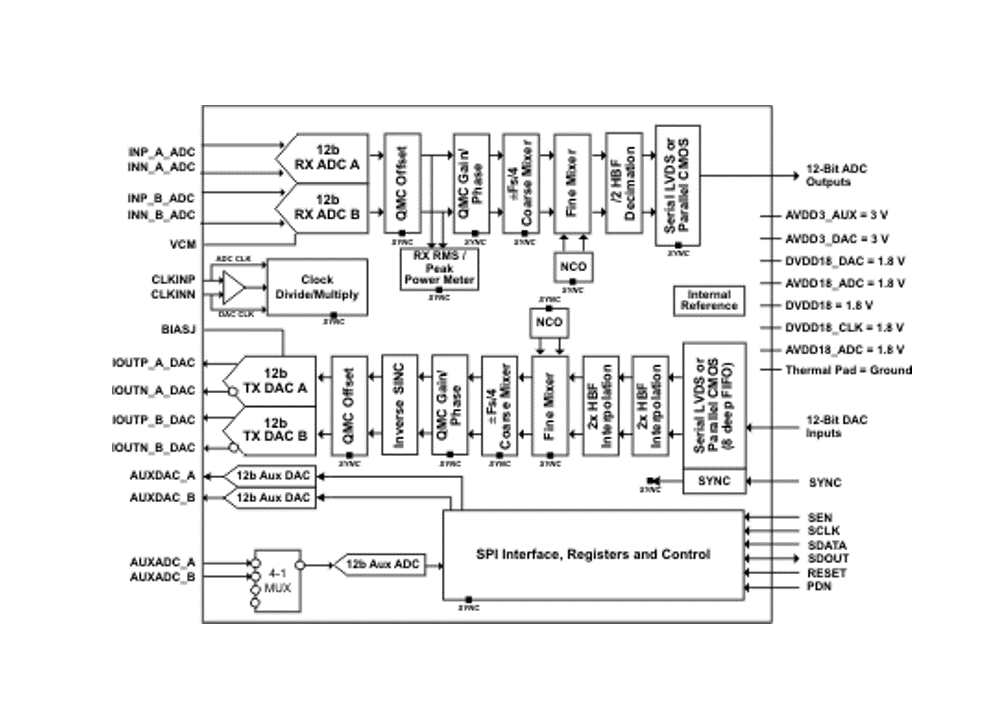

方框图

AFE7222/AFE7225 是德州仪器(TI)推出的引脚兼容宽带混合信号收发器(模拟前端),专为全双工 / 半双工软件无线电设计,集成双路 12 位 ADC、双路 12 位 DAC 及辅助 ADC/DAC,支持灵活的数字信号处理功能,适配便携式无线电、无线基础设施、微微蜂窝基站等场景,以低功耗、小尺寸和高动态性能为核心优势。

一、芯片基础信息与核心特性

1. 基础规格

- 型号差异 :文档编号 SLOS711B,2011 年 11 月发布、2012 年 3 月修订,AFE7222 为低速率版本,AFE7225 为高速率版本,二者引脚完全兼容。

- 供电与温度 :模拟电源 2.85V-3.6V(AVDD3 系列)、1.7V-1.9V(AVDD18 系列),数字电源 1.7V-1.9V(DVDD18 系列);工作温度 - 40°C 至 85°C,存储温度 - 65°C 至 150°C。

- 封装形式 :64 引脚 9mm×9mm QFN 封装(型号 RGC),底部带热焊盘,结到环境热阻 22.8°C/W,适配高密度 PCB 布局。

2. 核心性能指标

- ADC 性能 :AFE7222 最高 65 MSPS 采样率,AFE7225 最高 125 MSPS;差分输入范围 2 Vpp,SNR 典型值 70 dBFS-71.9 dBFS,SFDR 达 79.2 dBc-92.8 dBc,DNL±0.5 LSB、INL±1.7 LSB,模拟输入带宽 550 MHz。

- DAC 性能 :AFE7222 最高 130 MSPS 采样率,AFE7225 最高 250 MSPS;满量程输出电流 2 mA-20 mA 可调,SFDR 典型值 69 dBc-75 dBc,噪声谱密度(NSD)低至 - 130 dBc/Hz 以下,支持 2 倍 / 4 倍插值滤波。

- 辅助模块 :12 位辅助 ADC(最高 100 kSPS),双路 12 位辅助 DAC(最高 3.33 MSPS),用于电压监测和板级校准。

- 功耗优化 :全双工模式功耗 398 mW(CMOS 接口)-650 mW(LVDS 接口),支持全局掉电、快速唤醒掉电等多模式功耗控制,半双工 / 单通道模式可进一步降低功耗。

二、关键功能模块与工作原理

1. 核心功能模块

- 收发通道架构 :

- 接收路径:双路 ADC + 1/2 抽取滤波器 + 正交调制校正(QMC) + 粗 / 细混频器 + RMS / 峰值功率计,支持中频欠采样(最高 230 MHz)。

- 发射路径:双路 DAC + 2 倍 / 4 倍插值滤波器 + 逆 sinc 滤波器 + 8 级 FIFO + QMC + 粗 / 细混频器,FIFO 用于跨时钟域数据缓冲。

- 数字信号处理 :内置独立数控振荡器(NCO),支持频率搬移;QMC 模块校正 I/Q 通道增益 / 相位 / 偏移失衡;粗混频器支持 ±Fs/4 频率偏移,细混频器可灵活配置混频增益。

- 接口特性 :支持 LVDS/CMOS 双接口模式,LVDS 支持 1 线 / 2 线 DDR/SDR 传输,CMOS 支持交织并行 DDR 传输;通过 SPI 接口实现寄存器配置、数据读写及辅助模块控制。

- 辅助模块 :辅助 ADC 支持 2 路外部输入,用于电压监测;辅助 DAC 为电流输出(2.5 mA-7.5 mA),用于校准或控制。

2. 工作原理

- 接收链路:模拟信号经 ADC 采样后,通过抽取滤波器降低数据率,经 QMC 校正失衡,再由混频器完成频率搬移,最终通过数字接口输出;功率计实时监测信号峰值 / RMS 功率。

- 发射链路:数字信号经 FIFO 缓冲后,通过插值滤波器提升采样率,经 QMC 和混频器处理,由 DAC 转换为差分电流信号输出;FIFO 可避免跨时钟域数据冲突。

- 功耗控制:各功能模块可独立上电 / 掉电,支持半双工模式下的 TX/RX 快速切换,全局掉电功耗低至 3 mW,快速唤醒时间仅 4 μs-5 μs。

三、应用场景与设计建议

1. 典型应用

- 无线通信 :微微蜂窝基站、无线回程设备,支持宽带信号收发与中频处理。

- 测试测量 :宽带信号发生器、接收机,利用高带宽和高动态范围实现精准信号转换。

- 便携式设备 :低功耗设计适配电池供电场景,小尺寸封装满足小型化需求。

2. 设计注意事项

- 电源与接地 :模拟地与数字地需共地,各电源引脚就近并联 0.1 μF 去耦电容;热焊盘必须焊接至 PCB 接地平面,确保散热效率。

- 时钟设计 :支持差分 / LVDS/CMOS 时钟输入,高速模式(ADC>65 MSPS)建议启用占空比校正(DCC);优先采用高速率时钟分频方案,避免 PLL 倍频引入额外抖动。

- 信号匹配 :ADC 输入共模电压需匹配 0.95 V(VCM 引脚输出),DAC 电流输出需通过电阻或变压器匹配负载,建议参考 TI 推荐的 50 Ω 负载匹配电路。

- ESD 防护 :芯片内置 ESD 防护有限(HBM 2 kV),存储和操作时需将引脚短接或置于导电泡沫中,避免静电损坏。

四、关键配置与操作要点

1. 核心数字功能配置

- 信号处理配置 :通过寄存器选择 ADC 抽取率(1/2)、DAC 插值率(1/2/4);QMC 模块可配置 I/Q 通道增益(0-1.999 倍)、相位(-0.125 至 0.12475)及偏移(±256 LSB)。

- 接口配置 :CMOS 模式支持 DDR 交织并行传输,LVDS 模式支持 1 线 / 2 线传输,通过寄存器选择数据格式(2 补码 / 偏移二进制)、位序(MSB/LSB 优先)。

- 功耗控制 :PDN 引脚或寄存器可配置全局掉电、快速掉电、单通道掉电等模式,半双工模式下可通过寄存器实现 TX/RX 切换。

2. 典型操作流程

- 上电序列 :同时或按任意顺序启动 3V 和 1.8V 电源,通过 RESET 引脚输入≥100 ns 高脉冲复位芯片,配置 SPI 接口后启用目标功能模块。

- SPI 操作 :采用 20 位传输格式(12 位地址 + 8 位数据),支持寄存器读写、辅助 ADC 采样、辅助 DAC 数据更新,SCLK 最高频率 40 MHz。

- 多芯片同步 :通过 SYNC 引脚实现多芯片时钟分频器、FIFO、混频器相位同步,确保多通道一致性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入解析AFE7953:高性能多通道收发器的技术剖析与应用前景2026-01-26 471

-

AFE7222/AFE7225 宽带混合信号收发器技术文档总结2025-11-18 820

-

AFE8030 技术文档总结2025-10-30 796

-

AFE8004射频采样收发器技术文档总结2025-10-29 649

-

AFE8190 16 通道射频收发器技术文档总结2025-10-24 1044

-

AFE8192技术文档完整总结2025-10-21 669

-

宽带收发器IC ADI ADRV9040用户手册文档详解2025-03-25 1763

-

AFE7222的AD输入前段有26MHz的66倍谐波输出,怎么解决?2025-02-12 412

-

AFE8092IABJ 宽带宽多通道收发器的中文资料2021-12-16 2095

-

AD9863 12位混合信号前端(MxFE®)宽带应用基带收发器产品手册2021-05-09 880

-

RadioVerse生态系统中的宽带收发器分享!2019-09-17 2453

-

AFE7222 模拟前端宽带混合信号收发器2018-11-02 298

-

RadioVerse生态系统中的宽带收发器2018-08-16 2519

全部0条评论

快来发表一下你的评论吧 !