CPCI技术下对伺服卡WDM设计与研究

描述

引言

在当前光电子学系统中,以PC104 作为伺服控制分系统,体积庞大,不便于系统管理。 开发具有伺服控制能力的处理卡,用一块板卡替代原来的系统,能简化系统结构,提高系统 的集成度,使电子学系统最终成为一个高度集成的控制平台。

CPCI(CompactPCI)总线在PCI 总线基础之上,采用了欧洲卡结构,抛弃金手指式互 连方式,改用2mm 密度的针孔连接器,并具有可热插拔性,使其具有了更高的可靠性和开放 性,并且能适应恶劣的工作环境,在工业控制、航空航天等领域得到广泛应用。自行开发的 伺服控制卡基于CPCI 总线,以DSP 作为卡上控制CPU,与FPGA 结合实现控制。本论文以该 伺服控制卡为依托,在概述其硬件平台结构的基础上,介绍了在Windows 2000 下CPCI 设备 驱动程序的设计与开发,重点阐述了桥接芯片PCI9054 的DMA 数据传输实现及中断处理机制。

1.伺服控制卡的系统结构与硬件实现方案

伺服控制卡以 TI 公司的TMS320F2812 DSP 作为核心处理器,与FPGA 结合来实现整 个板卡的控制功能,通过CPCI 总线完成与上位PC 机的通信,其系统功能框图如图1 所示:

图 1 伺服控制卡硬件结构图

FPGA 选用Altera 公司的EPF10K30A,它内嵌1536Byte 的RAM,此RAM 为主机与DSP 共享,用于上位机与DSP 之间的高速数据缓冲,FPGA 负责接收上位机传递的命令和参数 等数据,经处理后发送给DSP 进行相应的控制操作,同时反馈信息给上位机。 TMS32F2812 的主要任务就是完成复杂的伺服控制算法,特别是位置控制和速度控制。

FPGA 通过2812 的外部中断XINT1 和XINT2 来触发2812 接收控制命令和参数,2812 接收 到命令后,根据自身定义的工作协议进入相应的工作状态。

系统设计中采用 PLX 公司的PCI9054 作为总线接口芯片,实现CPCI 局部总线与FPGA 的通信。PCI9054 采用C 模式,在该模式下,PCI 的数据线与地址线是非复用的,设计时只 需关注9054 的本地端总线。

2.WDM 驱动程序设计

在Windows 环境下,位于用户态的应用程序不能之间访问硬件资源,而要通过执行核 心态的驱动程序来间接完成对硬件资源的访问,因此,对于上位机上的应用程序,要对伺服 控制卡进行访问,必须要为其开发驱动程序。

WDM 驱动程序是一种Pnp 驱动程序,它能够实现Windows 98 与Windows 2000 、 Windows XP 之间的源代码级兼容。Windows 2000 性能稳定,在调试自行开发的板卡时,仍 然是首选的操作系统。在Windows 2000 中,所有对驱动程序的I/O 请求都转化为I/O 请求 包(IRP)来表示,IRP 是I/O 管理器在响应I/O 请求时从非分页系统内存中分配的一个可变 大小的数据结构,I/O 管理器负责产生代表一次I/O 操作的IRP,并将IRP 传至正确的设备 驱动程序,并通过分层的驱动程序传递给物理设备。设备驱动程序则接收IRP,执行相应的 操作,完成后再将IRP 传送回I/O 管理器,表示I/O 操作的完成或者通过I/O 管理器将其传 递给其他的驱动程序进行进一步的处理。

3.伺服控制卡的WDM 驱动程序设计与实现

驱动程序的开发环境常用的有微软的DDK、Jungo 的WinDriver 和Numega 的Driver Studio。Driver Studio 把DDK 封装成类,包含完善的代码生成和调试工具,并且提供对WDM 驱动的完全支持,利用它开发的核心态驱动程序运行效率也很高。本系统在VC 环境下利用 Driver Studio 开发驱动程序。

接口芯片 PCI9054 支持主模式、从模式和DMA 模式三种数据传输方式。DMA 传输不 通过处理器,直接进行数据交换,可以节省CPU 资源;并且DMA 模式还支持CPCI 总线与本 地总线之间的高效突发。

3.1 DMA 数据传输实现

PCI9054 集成了两个互相独立的DMA 通道,每一个通道由一个DMA 控制器和一个专 用双向FIFO 组成,都支持块DMA 和分散/集中DMA 操作,这里选用DMA 通道0,采用块 DMA 方式实现传输。在Driver Works 中提供了三个类来实现DMA传输,分别是KDmaAdapter 类、KDmaTransfer 类和KCommonDmaBuffer 类。

3.1.1.DMA 适配器

对于DMA 传输,驱动程序需要创建一个DMA 适配器,来表明一个DMA 通道的特性 和提供串行化访问的服务。KDmaAdapter 类实现对DMA 适配器的操作。在它的初始化函数 Initialize(PDEVICE_DESCRIPTION pDesc,PDEVICE_OBJECT pPdo)中第一个参数是一个 DEVICE_DESCRIPTION 结构的指针,这个参数用于对DMA 通道的属性进行设置。

3.1.2. DMA 控制器

采用 DMA 方式时,CPU 要放弃对系统总线的使用权,主存储器和外部设备是被控制的对 象,它们之间没有相互控制的能力,需要利用DMA 控制器来代替CPU 完成控制功能。

在用DriverWorks 开发驱动时, KDmaTransfer 类用于控制DMA 的传输;它可以启动一个DMA 传 输,指定DMA 传输的方向,DMA 传输数据缓冲区的物理地址和要传输的字节数。 KDmaTransfer 类的Initiate()函数用于初始化一个KDmaTransfer 对象;在成功初始化 一个KDmaTransfer 类对象后,将会调用DMA 准备就绪回调例程OnDmaReady,在该例程中获 取要传输的内存的地址和字节数,并调用StartDMA 例程开始DMA 传输。

与中断结合的DMA 传输在一次传输结束后会再次调用 KDmaTransfer 类的Continue()函数发起下一次的DMA 传输操作,直到传输完成。

3.1.3. DMA 公共缓冲区

在DriverWorks 中KCommonDmaBuffer 类实现对公用缓冲区的操作。在实际使用时,声 明一个KCommonDmaBuffer 类对象并初始化。在传输结束后,释放公共缓冲区,以防止内存 丢失。

3.1.4. 寄存器设置

PCI9054 在DMA 模式下传输,驱动程序要通过I/O 指令设置DMA 控制器内部的寄存器 以实现两总线间的数据传送,需要设置的内部寄存器及其具体功能如下表1 所示:

3.2 驱动开发中的中断处理机制及实现

本系统的驱动程序采用块DMA 与中断结合的方式来实现主机与伺服控制卡之间的数 据传输。以读操作为例,每次DMA 传输完后,都会产生一个DMA 中断,中断处理程序应 答中断,并获取公共缓冲区中的数据,通知主机端有数据到达;可以看出,高效的DMA 处 理依赖于高效的中断处理过程。

中断处理完成 CPU 与I/O 设备之间的信息交换,在为硬件板卡开发驱动程序时需要为 中断配置相应的驱动处理。在处理中断之前要对中断资源进行配置,首先定义并初始化一个 中断对象,在初始化阶段,提取IRP 资源中的中断级别、中断模式、中断向量、共享模式 等信息。利用上面获得的参数来连接中断,连接中断操作的主要目的是注册设备驱动的中断 服务例程(ISR),以便在中断发生后中断服务例程能够被调用。在DriverWorks 中用KInterrupt 类实现对硬件中断的处理。

status = m_Irq.InitializeAndConnect(pResListTranslated, LinkTo(Isr_Irq), this)

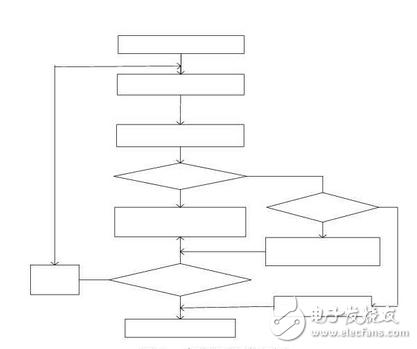

当硬件发生中断时,硬件抽象层(HAL)把中断级别(IRQL)提升到合适的中断级别, 然后调用中断服务例程(ISR)。CPCI 总线是中断共享的,因此,ISR 首先确定是哪一个设 备发生了中断, 如果不是当前设备的中断,立即返回FALSE ,以便HAL 把中断发送给其 他设备的驱动程序。如果是当前设备的中断,则在清除该中断,并做相应的处理。中断处理 的整个过程如下图2 所示:

ISR 执行在高于DISPATCH_LEVEL 的IRQL 上,它冻结了其CPU 上所有低于或等于该 IRQL 上的其他活动,为了提高系统性能,ISR 例程应该尽可能快的完成;此外,ISR 中使 用的所有代码和数据必须存在于非分页内存中,能调用的内核模式函数也十分有限。

图2:中断处理流程图

Windows 2000 提供了延迟过程调用(DPC)机制来解决这个问题,ISR 决定当前请求的 完成并请求一个DPC,之后,内核在DISPATCH_LEVEL 级上调用这个DPC 例程。当有当 前设备的中断到来时,把一个DPC 插入到DPC 队列中。实现代码如下:

m_DpcFor_Irq.Setup(LinkTo(DpcFor_Irq), this);//创建一个DPC m_DpcFor_Irq.Request(NULL, NULL)// 把一个DPC 插入到DPC 队列等待执行

4. 应用程序与驱动程序的通信

4.1 通信的实现策略

应用程序采用Win32 事件通知的方式与驱动程序进行通信:应用程序调用API 函数 CreatFile 打开设备,调用CreateEvent 创建事件句柄hEvent 并置为无信号态,把hEvent 作为 函数DeviceIoControl 的参数传递给驱动程序,同时调用CreateThread 创建等待线程;WDM 驱动程序接收事件句柄hEven,初始化KEvent 类对象m_hEvent,当中断发生时,在DPC 中 执行m_hEvent-》Set(),将事件设置为信号态,唤醒应用程序中的等待线程,然后调用 DeviceIoControl 完成数据传输。

4.2 数据传输速率测量

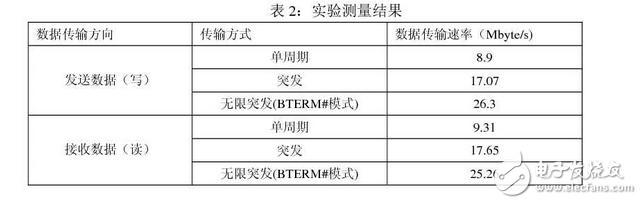

在实际测量时,采用了硬件测量法,应用程序不断向DSP 处理卡发送数据/接收数据, 利用示波器来观测BLAST#和ADS#信号的变化周期,得出每组数据的传输时间。该DSP 卡本地端总线为8 位,在DMA 模式下,测得的发送/接收时的测量结果如下表2 所示:

从以上结果可以看出,无限突发 DMA 模式传输速率最高,可达26.3Mbyte/s,若本地端总线 为32 位,则数据传输速率可以达到26.3*4=105.2Mbyte/s ,接近32 位PCI 总线的极限传输速率133Mbyte/s,能够满足大部分高速数据传输要求。

结束语

自行开发的伺服控制卡,基于高速的CPCI 总线,以DSP 作为卡上处理器,以FPGA 实现逻辑处理,能够作为一个独立的单元替代原来的工控机子系统,大大简化了当前光电子 学系统结构;利用Driver Studio 为其开发的底层驱动程序,能使板卡在Windows2000 下稳 定地工作,在与中断结合的DMA 数据传输模式下,数据传输速率能够满足伺服控制卡的精 度和实时性要求。

-

CPCI转PCI载板转接卡2024-09-07 507

-

pmc转cpci载板转接卡2024-09-06 460

-

CPCI 接口反射内存卡2024-09-05 1326

-

怎么实现基于CPCI总线的多网口卡设计?2021-06-02 1714

-

TFF型WDM器件技术原理2020-05-18 3220

-

Windows 2000下WDM驱动程序的研究与开发2016-04-18 872

-

CPCI高速采集回放卡2011-05-13 1329

-

基于CPCI总线的多网口卡设计2010-09-10 2095

-

IP over WDM,IP over WDM技术是什么意思2010-04-07 2512

-

基于CPCI总线的伺服控制卡的设计和实现2009-12-19 931

-

Windows环境下开发PCI接口卡DMA应用的WDM编程技2009-10-06 583

-

基于CPCI的伺服卡的DMA和中断研究2009-08-17 904

-

WINDOWS下PCI接口卡WDM驱动程序的DMA编程技术2009-08-07 655

全部0条评论

快来发表一下你的评论吧 !