ADC12D500RF 12 位中高速 RF 采样 ADC 技术文档总结

描述

12位1.6/1.0 GSPS ADC12D800/500RF是一种射频采样GSPS的ADC,可以直接实现 采样输入频率最高可达2.7 GHz及以上。ADC12D800/500RF增强了非常大的 TI GSPS ADC 的奈奎斯特区,在射频下具有优异的噪声和线性性能, 将可用航程扩展到7^th^奈奎斯特区

ADC12D800/500RF提供灵活的LVDS接口,支持多个SPI。 可编程选项用于促进板设计和FPGA/ASIC数据采集。LVDS输出为 兼容IEEE 1596.3-1996,并支持可编程共模电压。乘积为 采用无铅292球热增强BGA封装,覆盖在工业级 温度范围为-40°C至+85°C。

*附件:adc12d500rf.pdf

特性

- 噪声和线性表现优异,最高可达f。

在= 2.7 GHz - 可配置为1.6/1.0 GSPS交错式或800/500 MSPS双ADC

- 为高带宽、高采样率应用推出新的DESCLKIQ模式

- 与ADC1xD1x00针脚兼容

- 多芯片同步自动同步功能

- 内部终端缓冲差分模拟输入

- 交错正时自动与手动倾斜调节

- 系统调试输出端的测试模式

- 捕捉外部触发的时间戳功能

- 可编程增益、偏移和

广告调整功能 - 1:1 非多工或 1:2 去多工 LVDS 输出

- 主要规格

- 分辨率 12位

- 交错 1.6/1.0 GSPS ADCIMD

3(fin = 2.7GHz @ -13dBFS):-63/-61 dBc(类型)IMD3(Fin = 2.7GHz @ -16dBFS):-71/-69 dBc(典型) 噪声底:-152.2/-150.5 dBm/Hz(典型) 噪声功率比:50.4/50.7 dB(典型) 功率:2.50/2.02 W(典型) - 双800/500 MSPS ADC,Fin = 498 MHz ENOB:9.5/9.6 Bits(类型) SNR:59.7/59.7 dB(类型) SFDR:71.2/72 dBc(类型) 每通道功率:1.25/1.01 W(类型)

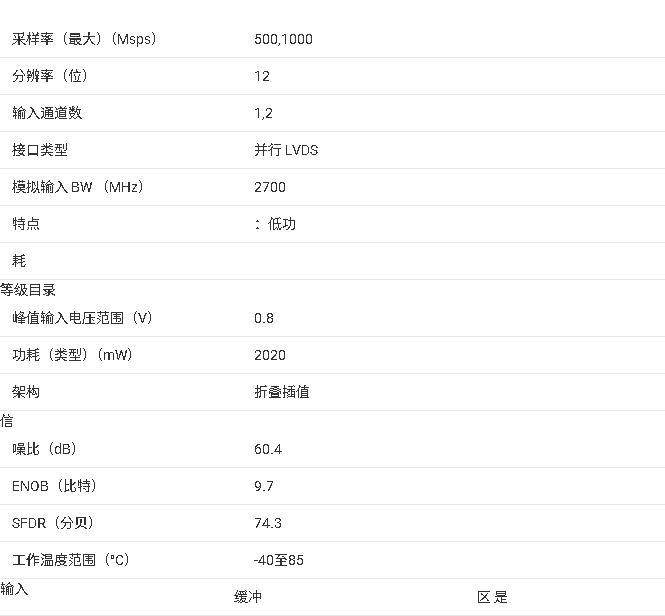

参数

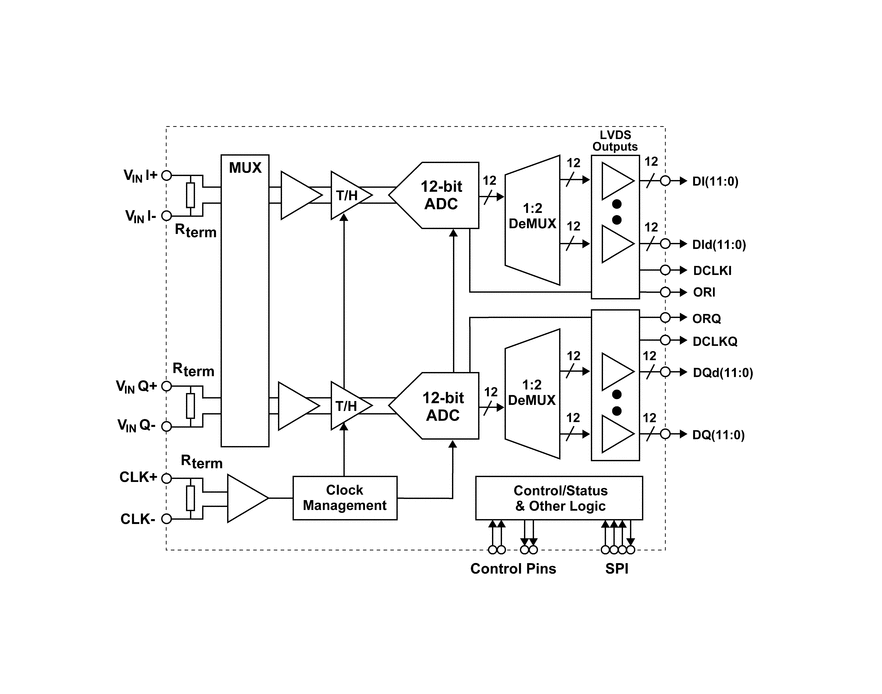

方框图

ADC12D500RF/800RF 是德州仪器(TI)推出的两款 12 位中高速 RF 采样 ADC,ADC12D500RF 最高采样率 1.0 GSPS(交织模式)/500 MSPS(双通道模式),ADC12D800RF 最高 1.6 GSPS(交织模式)/800 MSPS(双通道模式),支持直接采样 2.7 GHz 以上 RF 信号,兼具低功耗、高线性度与灵活配置特性,适用于 3G/4G 基站、宽带微波回程、软件无线电、雷达 / LIDAR 等中高频数据采集场景。

一、芯片基础信息与核心特性

1. 基础规格

- 文档与型号 :文档编号 SNAS502E,2011 年 7 月发布、2013 年 3 月修订;两款型号核心差异为采样率,ADC12D500RF 面向中速场景,ADC12D800RF 面向高速场景。

- 供电与温度 :多电源供电,模拟电源(V_A/V_TC/V_E)1.8V-2.0V,数字驱动电源(V_DR)1.8V-V_A;工作温度 - 40°C 至 85°C,存储温度 - 65°C 至 150°C,满足工业级环境要求。

- 封装与散热 :292 引脚 BGA 封装(27.00mm×27.00mm),结到环境热阻 16°C/W,结到底部外壳热阻 2.5°C/W,中心接地引脚需焊接至 PCB 接地平面以优化散热。

2. 核心性能指标

- 分辨率与精度 :12 位分辨率,无失码;INL±2.5 LSB-±7.25 LSB,DNL±0.4 LSB-±0.95 LSB,偏移误差 ±5 LSB,正负满刻度误差均为 ±30 mV,线性度表现稳定。

- 采样与动态性能 :ADC12D800RF 交织模式 1.6 GSPS、双通道 800 MSPS,ADC12D500RF 对应 1.0 GSPS/500 MSPS;2.7 GHz 输入时 IMD3 低至 - 87 dBFS,噪声底 - 150.5 dBm/Hz,SNR 最高 59.7 dB,SFDR 最高 74.3 dBc,ENOB 最高 9.7 Bits,动态性能优异。

- 输入与带宽 :内置 100Ω 差分输入终端,支持 AC/DC 耦合,输入带宽最高 4 GHz(-12 dB),可直接采样超高频 RF 信号,无需前端混频电路。

- ESD 与可靠性 :人体放电模型(HBM)±2500 V,带电器件模型(CDM)±1000 V,机械模型(MM)±250 V,静电防护能力强;连续输入电流 ±50 mA,脉冲电流 ±20 mA,工作稳定性可靠。

二、关键功能模块与工作原理

1. 核心功能模块

- 双通道多模式架构 :

- 支持交织模式(DES)与非交织模式(Non-DES),DES 模式下单通道采样率翻倍(如 ADC12D800RF 达 1.6 GSPS),通过 I/Q 通道交替采样实现;Non-DES 模式下为独立双通道(800 MSPS/500 MSPS 每通道)。

- 输出支持 1:1 非解复用(数据率 = 采样率)和 1:2 解复用(数据率 = 采样率 / 2),LVDS 接口兼容 IEEE 1596.3,支持 DDR/SDR 模式,可灵活适配 FPGA/ASIC 数据采集。

- 灵活配置接口 :

- 支持非扩展控制模式(Non-ECM,引脚直接控制)和扩展控制模式(ECM,SPI 接口配置),ECM 模式下通过 16 个寄存器实现增益、偏移、采样相位等参数精细化调节。

- 内置 AutoSync 多芯片同步功能,支持主从模式组网,可通过 RCLK 接口实现多 ADC 同步采样,同步延迟低至 4 个采样时钟周期。

- 校准与优化功能 :

- 支持上电自动校准与手动触发校准,校准涵盖输入终端电阻、时钟电阻及内部线性度,校准后可显著降低 INL/DNL 误差。

- 具备采样时钟相位调节(最大 825 ps 延迟)、DES 时序调整、自动占空比校正等功能,可补偿系统时钟偏差与通道间 skew。

2. 工作原理

- 采用校准折叠插值架构,通过折叠放大器减少比较器数量,结合插值技术降低前端放大器负载,在中高速采样率下实现低功耗与高线性度平衡。

- 模拟信号经差分输入缓冲后,由采样保持电路捕获,经 12 位 ADC 转换为数字信号,通过解复用器输出至 LVDS 总线;采样时钟支持双沿采样(DES 模式),可在单一时钟周期内完成两次采样,实现采样率翻倍。

- 数字部分支持偏移二进制 / 二进制补码输出格式,内置测试图案生成器与时间戳功能,便于系统调试与外部触发事件捕获。

三、应用场景与设计建议

1. 典型应用

- 无线通信 :3G/4G 基站接收路径与 DPD 路径,宽带微波回程设备,支持高频信号直接采样,简化射频前端设计。

- 国防与测试测量 :软件无线电(SDR)、军事通信、信号情报(SIGINT)、雷达 / LIDAR,适配中高频、中高速数据采集需求。

- 消费电子与工业 :高端测试仪器、宽带通信设备,可替代传统 “混频 + ADC” 架构,降低系统复杂度与成本。

2. 设计注意事项

- 电源与去耦 :多电源需独立供电,V_A/V_TC/V_E/V_DR 需分别并联 0.1 µF 陶瓷电容与 100 nF 钽电容,电容就近布局,减少电源噪声耦合。

- 输入与时钟设计 :

- 模拟输入需差分阻抗匹配(100Ω 差分 / 50Ω 单端),AC 耦合时选用合适电容保证低频信号完整性; unused 通道需按模式 terminated(AC 耦合接 AC 地、DC 耦合接 V_CMO)。

- 采样时钟需差分 AC 耦合输入(0.4 V_P-P-2.0 V_P-P),时钟源抖动需控制在 0.2 ps(rms)以内,推荐使用 TI LMX2531 等低相噪时钟芯片。

- 布局与散热 :

- 采用多层 PCB 设计,模拟地与数字地共面且通过多过孔连接,高速信号(时钟 / 数据)短距走线、阻抗控制,远离模拟区域。

- 中心散热焊盘需与 PCB 接地平面紧密连接,大面积敷铜增强散热,避免结温超过 135°C 额定值。

- 校准与同步 :上电后需等待电源稳定再启动校准,模式切换(如 DES/Non-DES)或温度变化较大时需重新校准;多芯片同步优先使用 AutoSync 功能,主从 ADC 时钟路径长度需严格一致。

四、关键配置与操作要点

1. 核心功能配置

- 工作模式选择 :

- 采样模式:DES 模式(单通道高速)或 Non-DES 模式(双通道独立),通过 DES 引脚或寄存器(Addr:0h Bit7)配置,DES 模式需确保 I/Q 通道均上电。

- 输出模式:解复用模式(NDM 引脚低)或非解复用模式(NDM 引脚高),DDR 模式支持 0°/90° 相位关系,可通过 DDRPh 引脚或寄存器(Addr:0h Bit14)选择。

- 参数调节 :

- 满量程范围(V_IN_FSR):Non-ECM 模式通过 FSR 引脚选择(600 mV_P-P/800 mV_P-P),ECM 模式可通过寄存器(Addr:3h/Bh)实现 15 位精度调节(600 mV_P-P-1000 mV_P-P)。

- 偏移调节:ECM 模式下通过寄存器(Addr:2h/Ah)实现 ±45 mV 偏移调整,步长约 11 µV,可补偿系统输入偏移。

2. 操作流程

- 校准操作 :上电后自动校准(CalDly 引脚选择延迟时间),或通过 CAL 引脚 / 寄存器触发手动校准,校准期间数字输出置低,校准完成后需等待 60 个采样时钟周期使数据有效。

- 多芯片同步 :配置主 ADC 为 Master 模式,从 ADC 为 Slave 模式,通过主 ADC 的 RCOut 输出时钟至从 ADC 的 RCLK 输入,利用 AutoSync 寄存器(Addr:Eh)调节延迟,实现多 ADC DCLK 同步。

- 低功耗优化 :支持 I/Q 通道独立掉电(PDI/PDQ 引脚或寄存器控制),未使用通道掉电后可降低总功耗,重新上电后需执行校准以恢复性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

12位高速IF采样ADC——AD9433的技术解析与应用指南2026-04-08 174

-

ADC12D500RF/800RF 12 位高速 RF 采样 ADC 产品总结2025-11-19 628

-

ADC12D1000RF 12 位高采样率 RF 采样 ADC 技术文档总结2025-11-18 1016

-

ADC12J1600 12位、1.6GSPS、RF采样模数转换器(ADC)技术手册2025-11-12 687

-

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册2025-11-01 1471

-

ADC12DJ4000RF RF采样12位ADC技术手册2025-10-31 838

-

ADC12D500RF是积分型的AD转换器吗,还是别的什么类型的?2025-02-10 392

-

ADC12D1600和ADC12D1600RF这两种型号之间有什么区别?2025-01-10 321

-

ADC12D1x00RF 12位、3.2 GSPS和2 GSPS RF采样ADC数据表2024-07-22 507

-

ADC12DJ5200RF双通道、12位射频采样模数转换器(ADC)数据表2024-07-19 718

-

ADC12D800/500RF射频采样GSPS ADC英文手册2023-09-20 502

-

ADC12D1600RFIUT/NOPB 12 位、2.0/3.2 GSPS 射频采样 ADC订货2018-07-30 961

全部0条评论

快来发表一下你的评论吧 !