ADS41B25 12 位超低功耗 ADC 产品总结

描述

该ADS41B25属于超低功耗ADS4xxx模拟转数字转换器(ADC)系列,集成了模拟输入缓冲器。该设备采用创新设计技术,实现高动态性能,同时功耗极低。模拟输入引脚带有缓冲区,其优点是稳定的性能和在宽频范围内的输入阻抗。该设备非常适合多载波宽带宽通信应用,如PA线性化。

*附件:ads41b25.pdf

ADS41B25具备数字增益和偏移校正等功能。增益选项可用于提升SFDR在较低全刻度输入范围,尤其是高输入频率下的性能。集成的直流偏移校正环路可用于估计和取消ADC偏移。在较低采样率下,ADC自动以降低功率运行,且性能不损耗。

该设备支持双倍数据速率(DDR)低电压差分信号(LVDS)和并行CMOS数字输出接口。DDR LVDS接口的低数据速率(最高500MBPS)使得使用基于FPGA的低成本现场可编程门阵列(FPGA)接收成为可能。该设备具有低摆幅LVDS模式,可用于进一步降低功耗。LVDS输出缓冲器的强度也可以提高,以支持50Ω差分终端。

该设备采用紧凑型QFN-48封装,适用于工业温度范围(–40°C至+85°C)。

特性

- 分辨率:12位,125MSPS

- 集成高阻抗模拟输入缓冲器:

- 直流输入电容:3.5pF

- 直流输入电阻:10kΩ

- 最大采样率:125MSPS

- 超低功率:

- 1.8V模拟功率:114mW

- 3.3V 缓冲功率:96mW

- 输入输出功率:100mW(DDR LVDS)

- 高动态性能:

- 信噪比:170MHz时68.3dBFS

- SFDR:170MHz时87dBc

- 输出接口:

- 双倍数据率(DDR)LVDS,具备可编程摆动和强度:

- 标准摆幅:350mV

- 低摆幅:200mV

- 默认强度:100Ω 终端

- 2倍强度:50Ω终端

- 还支持 1.8V 并行 CMOS 接口

- 双倍数据率(DDR)LVDS,具备可编程摆动和强度:

- 可编程增益用于信噪比/SFDR权衡

- 直流偏移校正

- 支持低输入时钟幅度

- 包装:QFN-48(7毫米×7毫米)

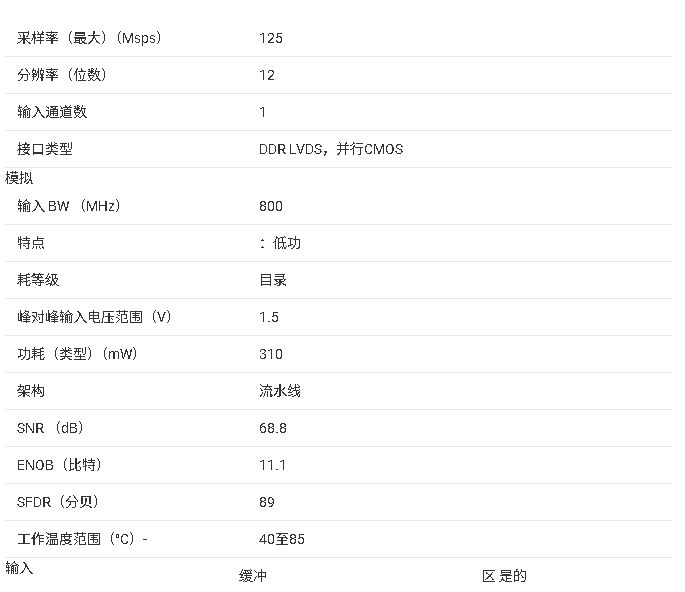

参数

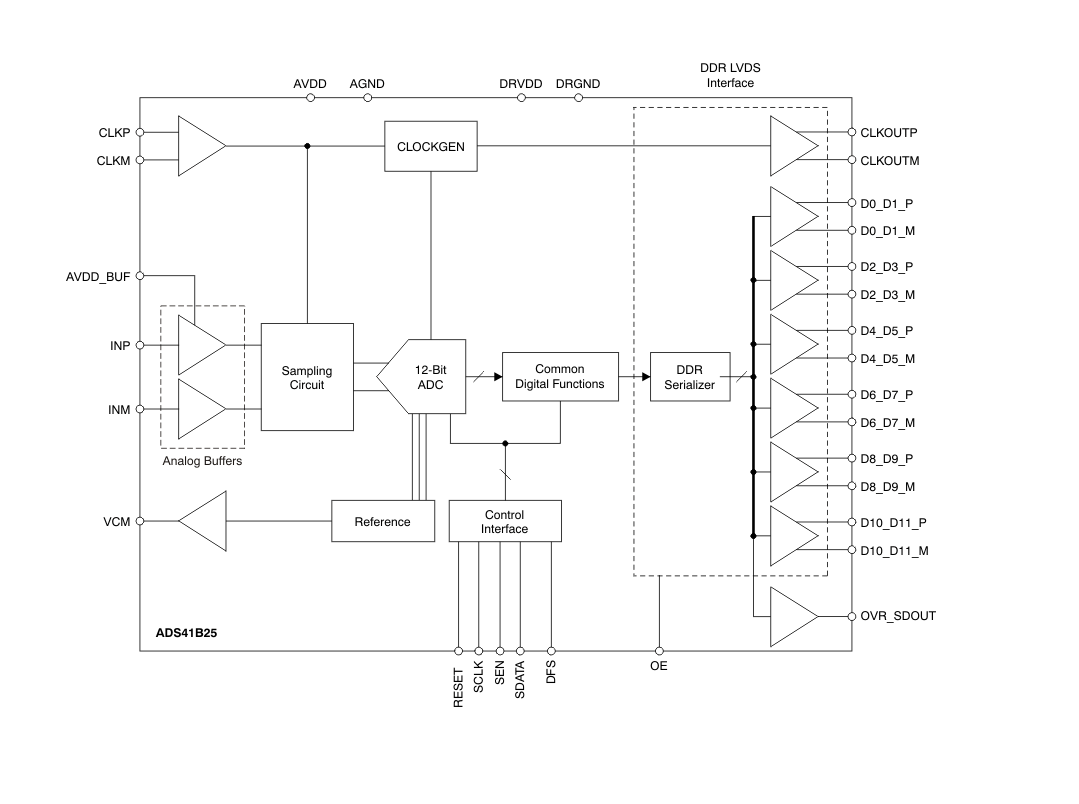

方框图

一、产品概述

ADS41B25 是德州仪器(TI)推出的 12 位、最高 125MSPS 采样率的超低功耗模数转换器(ADC),集成模拟输入缓冲器,采用创新设计实现高动态性能与低功耗的平衡。其高阻抗输入特性和宽频率范围内的稳定性能,使其适用于多载波、宽带通信等场景,尤其适配功率放大器线性化(PA linearization)应用,工作温度范围覆盖工业级(-40°C 至 85°C)。

二、核心技术参数

1. 基础性能指标

- 分辨率与采样率 :12 位分辨率,最高采样率 125MSPS,支持低速模式(≤80MSPS)自动降功耗,无性能损失。

- 功耗表现 :1.8V 模拟电源功耗 114mW,3.3V 缓冲器功耗 96mW,DDR LVDS 接口 I/O 功耗 100mW,总功耗低至 310mW(典型值)。

- 封装与热特性 :采用 48 引脚 QFN 封装(7mm×7mm),结到环境热阻 27.9°C/W,暴露热焊盘(PowerPAD)需焊接至地平面以优化散热。

- 输入与输出 :模拟输入缓冲器提供 10kΩ 直流电阻、3.5pF 输入电容,支持 1.5VPP 差分输入;输出接口可选 DDR LVDS(350mV/200mV 可编程摆幅)或 1.8V 并行 CMOS。

2. 动态性能(典型值,f_IN=170MHz)

- SNR(信噪比) :68.3dBFS;

- SFDR(无杂散动态范围) :87dBc;

- THD(总谐波失真) :83dBc;

- ENOB(有效位数) :11.1 位;

- 三阶互调失真(IMD) :-86dBFS(双音输入 185MHz/190MHz)。

三、关键功能特性

1. 灵活配置与性能优化

- 可编程增益 :支持 0dB~3.5dB 步进 0.5dB 的数字增益调节,可在低满量程输入时提升 SFDR 性能,实现 SNR 与 SFDR 的灵活权衡。

- 高绩效模式 :通过寄存器配置可启用两种高绩效模式,Mode 1 适配全频率范围最优性能,Mode 2 针对 230MHz 以上高频输入优化。

- 直流偏移校正 :内置偏移校正环路,支持 ±10mV 偏移补偿,可通过寄存器启用 / 冻结校正功能,校正时间常数可编程(1M~2G 时钟周期)。

2. 输入与输出特性

- 模拟输入缓冲 :集成高阻抗缓冲器,隔离外部驱动源与采样电路,降低驱动难度,输入带宽最高达 800MHz(-3dB)。

- 多输出接口 :DDR LVDS 模式支持 100Ω/50Ω 终端匹配,数据速率最高 500MBPS,适配低成本 FPGA;CMOS 模式提供 12 位并行输出,需控制负载电容≤5pF 以减少噪声耦合。

- 过压指示 :OVR 引脚实时指示输入过压状态,过压时输出固定满量程码(偏移二进制:000h/-FS、FFFh/+FS)。

3. 电源管理与控制

- 功耗模式 :支持全局掉电(功耗≈7mW)、待机(仅 ADC 掉电,唤醒时间 5μs)、输出缓冲禁用三种低功耗模式,时钟频率<1MSPS 时自动进入低功耗。

- 控制接口 :支持 SPI 串行接口(最高 20MHz 时钟)配置寄存器,也可通过 DFS/OE/SDATA 引脚快速配置输出格式、接口类型及待机状态。

四、应用与设计要点

1. 典型应用场景

- 多载波宽带通信、功率放大器线性化;

- 软件定义无线电(SDR)、无线通信基础设施;

- 测试测量设备、中频信号采集系统。

2. 硬件设计建议

- 模拟输入驱动 :推荐差分驱动,串联 5~10Ω 电阻抑制寄生振荡,高频输入(>奈奎斯特频率)建议采用背对背变压器减少谐波失真。

- 时钟设计 :支持差分(正弦波、LVPECL、LVDS)或单端(LVCMOS)时钟输入,AC 耦合,差分阻抗匹配 100Ω,建议使用低抖动时钟源(如 TI LMX 系列 PLL)。

- 电源与布局 :模拟电源(AVDD)、缓冲器电源(AVDD_BUF)、数字电源(DRVDD)需分离供电,就近放置去耦电容;PCB 采用单接地平面,模拟 / 数字 / 时钟区域分区布局,暴露热焊盘可靠接地。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS41B29/ADS41B49 高速低功耗模数转换器产品总结2025-11-20 698

-

ADS58B18/ADS58B19 超低功耗高速 ADC 产品总结2025-11-19 839

-

ADS4249 双通道 14 位 250 MSPS 超低功耗 ADC 技术文档总结2025-11-18 1101

-

ADS7042超低功耗、超小尺寸、12位、1-MSPS、SAR ADC数据表2024-09-13 667

-

ADS7056超低功耗、超小尺寸14位高速SAR ADC数据表2024-07-30 747

-

ADS41B25具有模拟缓冲器的12位125MSPS超低功耗ADC数据表2024-07-27 458

-

ADS794x超低功耗、12/10/8位双通道SAR ADC数据表2024-07-25 507

-

ADS7044超低功耗、超小尺寸、12位、1MSPS、SAR ADC数据表2024-07-23 525

-

ADS4128 12位200MSPS超低功耗ADC数据表2024-07-17 522

-

模数转换器ADS41B25的特点性能及作用分析2020-10-27 1322

全部0条评论

快来发表一下你的评论吧 !