UALink协议引领人工智能计算领域变革

描述

本文翻译转载于:Cadence Blog

作者:Sangeeta Soni

今年 4 月 25 日,UALink 联盟正式发布了 UALink 200G 1.0 规范,在众多超大规模市场核心参与者的支持下,这一成果成为了该领域的重要的里程碑。该规范打造了一种低延迟、高带宽的通信架构,能够在一个机柜中支持数百个加速器,还能让加载-存储语义实现变得更加简洁高效。

UALink 诞生的诱因

人工智能和机器学习的飞速发展,正推动着对高性能计算资源的需求达到前所未有的程度。以近期爆火的“吉卜力风格”热潮为例,它需要动用惊人的 1 万亿次浮点运算来生成 AI 图像——这充分凸显了现代工作负载的计算密集特性。这些工作负载需要可扩展的互连技术,以针对高带宽、低延迟和硬件资源的高效利用进行优化。尽管存在专有接口,但行业缺乏能满足这些需求的开放标准。为了填补这一空白,UALink 应运而生,成为首个支持加速器无缝向上扩展集成(scale-up)的开放标准,为人工智能计算领域带来了范式变革。

协议快速解析

UALink 提出了一种非一致性互连解决方案,利用四路 200G 以太网物理层,实现了每个端口 800Gbps 的速率。值得注意的是,高层通道经过优化,可满足向上扩展(scale-up)应用的需求。

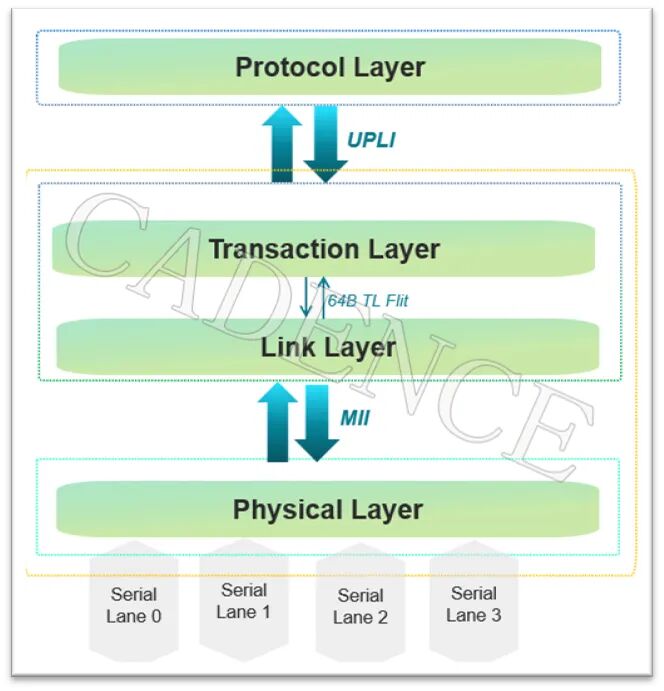

UALink 被设计为分层协议栈,包含四个不同且定义清晰的功能层:

协议层:用于数据和控制交换的简单对称协议接口

事务层:定义 64G 数据分片的封装、数据包格式以及流控机制

数据链路层:包括错误恢复功能,包括数据分片重放以及 RAS 特性

物理层:基于 802.3dj 以太网物理层,进行了部分特定修改

Cadence 的 UALink 验证 IP

Cadence 为高性能计算和人工智能市场提供前沿的协议支持,助力我们的客户率先推出下一代创新解决方案。Cadence 验证 IP 在人工智能和高性能计算领域的片上系统的可靠一站式验证领域处于领先地位。我们已实现对 PCle 7.0、CXL 4.0 以及 PCle 和 CXL 完整性与数据加密的成熟支持,如今又新增对 UEC 和 UALink VIP 的支持,在全面验证方案领域引领行业发展。

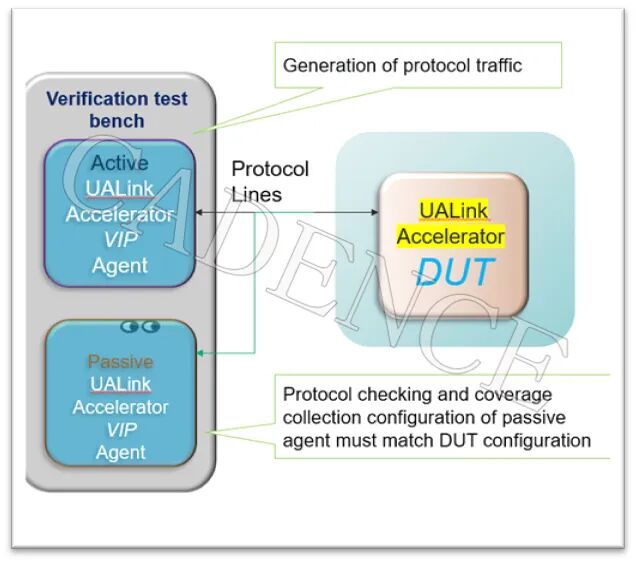

UALink VIP 遵循协议定义的分层架构,为用户提供灵活的使用体验。这种模块化架构支持在模板和协议栈层面使用该 VIP。VIP 在逻辑协议交互点提出回调支持和错误注入功能,便于调试、覆盖率分析、计分板统计及其他测试平台需求的实现。下图展示了采用该验证 IP 的参考验证拓扑结构:

Cadence 正与早期采用者开展合作,并期待随着 UALink 生态系统的发展,能与更多客户展开合作。

-

CES Asia 2025蓄势待发,聚焦低空经济与AI,引领未来产业新变革2025-07-09 4711

-

人工智能已经进入医疗领域2017-05-24 5159

-

人工智能会把人类从劳动中解放出来吗2017-09-15 5200

-

数据对人工智能发展的重要性2017-10-09 5467

-

人工智能的影响超乎你想象2018-06-22 4672

-

什么是基于云计算的人工智能服务?2019-09-11 5703

-

人工智能的应用领域有哪些?2020-10-23 4996

-

人工智能在英语教育领域2020-12-14 2332

-

AI全球格局之人工智能即将变革的三大领域 相关资料分享2021-07-06 2476

-

物联网人工智能是什么?2021-09-09 5191

-

寒武纪陈天石:5G补齐AI致命短板 引领人工智能时代变革2018-09-25 5161

-

5G的到来,将引领人工智能时代变革2018-10-01 1100

-

类脑智能引领人工智能发展带来新机遇2019-01-15 5150

-

用“科技向善”理念引领人工智能发展2019-07-03 792

-

博世持续引领人工智能的应用与开发2025-06-27 867

全部0条评论

快来发表一下你的评论吧 !