运用平衡放大技术实现读卡器末级功率放大器的设计

描述

随着860 MHz~960 MHz(UHF)频段远距离射频识别(RFID)技术的快速发展,UHF频段读卡器在高速公路自动收费、停车场管理等领域得到广泛的应用。UHF频段读卡器的一个最大优点是读卡距离远。此处的卡为无源卡,需要接收读卡器的发射功率作为能量,获得能量才能正常工作从而把卡号发给读卡器。因此影响读卡器读卡距离远近的重要因素是发射功率的大小。读卡器一般工作在跳频模式,即在一定的时间内载波频率以250 kHz为间隔从902 MHz跳到928 MHz。在这种工作模式下,要求读卡器的末级功率放大器带内增益波动必须小。如果功率放大器的带内增益平坦度很差,则在某些频点上输出功率较小,这样就会导致在这些频点上读卡器有可能读不到卡或读卡距离很近,以致读卡器的读卡距离性能受到严重影响。所以读卡器末级功率放大器设计的主要目标就是在工作频带内实现平坦的功率增益,同时为了便于前级和后级电路的独立设计也要求具有较好的输入、输出驻波比。就目前来说,有补偿匹配、负反馈电路和平衡放大3种技术可以实现频带内平坦的功率增益。补偿匹配电路技术是通过在放大电路中设计失配的输入和输出匹配网络,来补偿射频晶体管正向电压传输系数| S21 |随频率的变化,从而实现频带范围内功率增益的平坦。在使用频率补偿网络时,由于在一些频段匹配电路处于阻抗失配状态,会导致放大电路的输入或者输出端口的驻波系数VSWR的增加,不利于前级和后级电路的设计。负反馈电路技术虽然可以在整个频带内获得平坦的功率增益并且还可以降低输入和输出驻波系数,但是会增大放大电路的噪声系数而且还会使放大电路的功率增益大幅度降低[1]。与前2种技术相比,平衡放大技术的优点是:可以独立设计射频放大电路;获得平坦的功率增益和噪声系数;不必过多地考虑输入和输出端口的阻抗失配问题;具有更高的稳定性和可靠性;容易实现级联工作并且具有2倍于单个放大电路的功率输出[2]。

1 平衡放大器工作原理

平衡放大电路采用2个3 dB混合耦合器和2个射频放大芯片构成对称电路,通过隔离入射信号和反射信号,从而实现频带范围内功率增益的平坦和降低输入、输出端口的驻波比,电路结构框图如图1所示[3]。

因为平衡放大电路中包含了3 dB耦合器,所以有必要先分析一下3 dB耦合器的传输特性。参考图1来描述3 dB耦合器的传输特性:(1)如果射频信号从1端口输入其他端口连接匹配负载,则1端口入射的射频信号的功率被平均分配到2端口和3端口输出并且输出信号的相位在2端口相对于3端口超前П/2,在4端口由于信号抵消而没有功率输出;(2)如果2端口和3端口输入相同幅度的射频信号,并且在相位上2端口的射频信号超前3端口射频信号П/2,则射频功率在4端口输出并且功率为输入功率之和,在1端口由于信号抵消没有功率输出。

根据上述3 dB分支耦合器的传输特性,1端口入射的射频信号经过3 dB耦合器后,被平均分配到2个放大器芯片T1和T2的输入端口,其中2端口的射频信号超前3端口П/2。假设2个放大电路的特性完全一致,则放大器芯片T1和T2反射的射频信号幅度相同,反射信号将进入3 dB分支耦合器。由于反射信号在2端口的相位超前3端口П/2,按照3 dB分支耦合器的特性,合成功率在4端口输出被50 Ω的匹配电阻吸收,而在1端口则没有输出。因此,即使2个放大电路在输入端产生很大的反射,在平衡放大电路的射频输入端可以没有射频信号的反射,实现很低的输入驻波系数。同理,经过放大电路后的输出信号会在放大电路的输出端口合成,而反射信号则被50 Ω的匹配电阻吸收,可以大幅度降低放大电路的输出驻波系数。

2 放大器设计及优化

2.1 设计指标

频率范围:902 MHz~928 MHz;输入功率:19 dBm;输出功率:32 dBm;增益:13 dB;增益平坦度≤±0.5 dB;二次谐波分量≤-30 dBc;输入、输出驻波比≤1.5。

2.2 器件的选择

平衡功率放大器的设计需要2个3 dB正交耦合器和2个放大器芯片,由于电路结构完全对称,所以上下2个放大器芯片完全相同。3 dB正交耦合器的选择主要考虑其输入、输出驻波比。放大器芯片的选择主要考虑其1 dB增益压缩点。本设计选择了Anaren公司的3 dB正交耦合器XC0900A-03。该耦合器工作频段在811 MHz~1 000 MHz,驻波比都在1.5以下。放大器芯片为WJ公司的FP31QF,该放大器芯片的工作频段为50 MHz~4 000 MHz,在915 MHz时1 dB压缩点的输出功率可达34 dBm。上述器件的特性指标都满足设计要求,因此这些器件可以很好地应用在平衡功率放大器的设计中。

2.3 直流工作点的确定

在晶体管的技术参数中,半导体厂家通常会给出放大器芯片的直流工作电压和电流。本设计的放大器芯片FP31QF采用技术参数给定的(Vds=9 V,Ids=450 mA)直流工作点来设计直流偏置电路。

2.4 直流偏置电路的设计

良好的直流偏置设计目标是选择适当的静态工作点,并在晶体管参数和温度变化的范围内,保持静态工作点的恒定[4]。本功放采取先对直流供电并联不同值的滤波电容用以滤除供电电压中不同频率的纹波,再通过射频扼流圈把直流电压馈入放大器。射频扼流圈对直流相当于短路,对射频信号相当于开路防止射频信号泄露。实际中用电感代替射频扼流圈能够起到相同的作用。

2.5 匹配网络的设计

本文的输入、输出匹配网络是根据数据手册给定的器件S参数,按照小信号放大器的设计方法来设计的[5]。由于平衡功率放大器的结构是完全对称的,所以只需要对一个放大器芯片进行输入、输出匹配网络的设计。

整个放大器的源阻抗和负载阻抗均按50 Ω设计[6]。首先,设计放大器芯片的输入匹配。根据器件数据手册给定,工作频率为1 000 MHz时放大器芯片S11=0.9∠-160.54参数,采用集总参数匹配中的T型匹配网络利用Smith圆图把放大器芯片的S11匹配到50 Ω。其次,设计放大器芯片的输出匹配网络。根据数据手册给定,工作频率1 000 MHz时第二阶放大器S22=0.49∠-162.14参数。采用集总参数匹配中的L型匹配网络利用Smith圆图把S22匹配到圆图的中心。L型匹配网络中的串联电容直接放在放大器芯片输出端,既起到隔直作用,又起到匹配作用。整个放大器的匹配网络都是根据器件数据手册提供的工作频率在1 000 MHz时的S参数设计的,而放大器的实际中心工作频率为915 MHz。之后会通过仿真优化消除匹配网络设计所带来的误差。

2.6 仿真优化

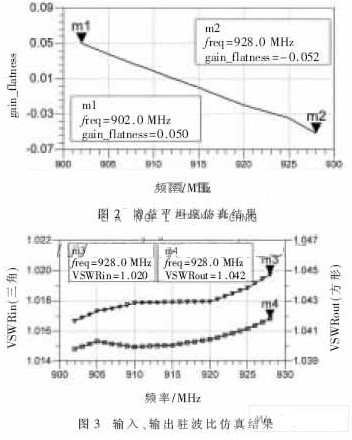

选择器件的S参数模型,采用Agilent公司的仿真软件ADS2008对设计完成的整个平衡功率放大器进行仿真优化。优化目标设在902 MHz~928 MHz频段内,放大器的增益平坦度≤±0.5 dB;输入、输出驻波比≤1.5。仿真优化结果如图2、图3所示。

图2中的m1表示在902 MHz~928 MHz频段内,放大器最大增益偏离平均值0.05 dB,m2表示最小增益偏离平均值为-0.052 dB;图3中的m3和m4分别表示在整个频段内放大器的输入驻波比最大为1.02,放大器的输出驻波比最大为1.047。

仿真结果表明,整个工作频段内放大器的增益平坦度≤±0.1,输入、输出驻波比≤1.1,完全满足设计指标要求。

3 实际测试

电路板加工完成后,进行焊接。在焊接时,一定要注意放大器芯片和耦合器底部的散热片与PCB板散热片的充分接触。如果散热片没有充分接触,则会导致放大器芯片和耦合器的结温过高,从而使放大器和耦合器不能正常工作。电路板焊接完成后,需对放大器进行实际的测试。

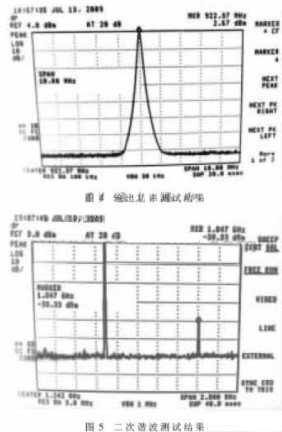

采用惠普公司的HP8594E频谱分析仪对放大器的输出功率、二次谐波分量参数进行测量。测试前需给放大器提供-1 V的栅极和9 V的漏极直流偏置电压,使放大器正常工作。放大器的输入端输入一个频率为922.375 MHz、功率为19 dBm的已调波信号。由于频谱分析仪最大的输入功率为30 dBm。为了防止频谱仪的损坏,测试时频谱仪的输入端需加一个衰减器,衰减值应保证大于放大器额定输出功率与频谱仪最大输入功率的差值。本设计使用了一个30 dB衰减器,测试结果如图4、图5所示。

图4为放大器的输出功率测试结果。由图中的标记可以看出,在输入功率为19 dBm、频谱仪输入端加30 dB衰减的条件下,放大器的输出功率为2.67 dBm。由此可以推断出放大器的实际输出功率为32.67 dBm,同时可得放大器在该频点的功率增益达13 dB。图5为放大器的二次谐波分量测试结果。放大器的输入频率为922.375 MHz,则放大器的二次谐波频率为1 845 MHz。图中标记显示在输入功率为19 dBm,频谱仪输入端加30 dB衰减的条件下,放大器的二次谐波输出功率为-38.33 dBm。二次谐波分量为放大器的二次谐波分量输出功率减去基波分量输出功率。由此可得二次谐波分量为-41 dBc。

由上述测试结果可得放大器的输出功率为32.67 dBm,二次谐波分量为-41 dBc功率增益达到13 dB,完全满足设计指标所要求的输出功率32 dB、二次谐波≤-30 dBc、增益为13 dB。

本文在分析平衡功率放大器电路结构和工作原理的基础上,清楚、直观地演示了运用平衡放大技术来设计读卡器末级功率放大器的过程。仿真和实际测试结果显示,所设计的功率放大器实现了工作频带内低增益平坦度和良好的输入、输出驻波比等要求。

-

低频功率放大器工作原理2023-02-17 1122

-

高频功率放大器知识分享2022-11-29 1429

-

低频功率放大器的工作原理2022-09-20 13040

-

RF功率放大器的设计2021-12-22 12737

-

一款简单的末级功率放大器资料分享2021-05-10 1860

-

短波宽带功率放大器2020-02-07 2127

-

末级功率放大器原理是什么?2019-09-12 2293

-

射频功率放大器的全面介绍2019-06-28 4354

-

盘点常用的几类功率放大器芯片2019-04-12 9698

-

功率放大器类型有哪些?功率放大器如何选择厂家2017-10-17 4403

-

功率放大器的性能指标,功率放大器的应用2017-05-12 4107

-

射频功率放大器简介2011-11-18 6585

-

末级功率放大器原理及电路2010-04-16 5915

-

线性功率放大器设计和乙类和丙类功率放大器设计2008-08-17 9486

全部0条评论

快来发表一下你的评论吧 !