VSP5610/11/12 4 通道 16 位 CCD/CMOS 传感器模拟前端(AFE)总结

描述

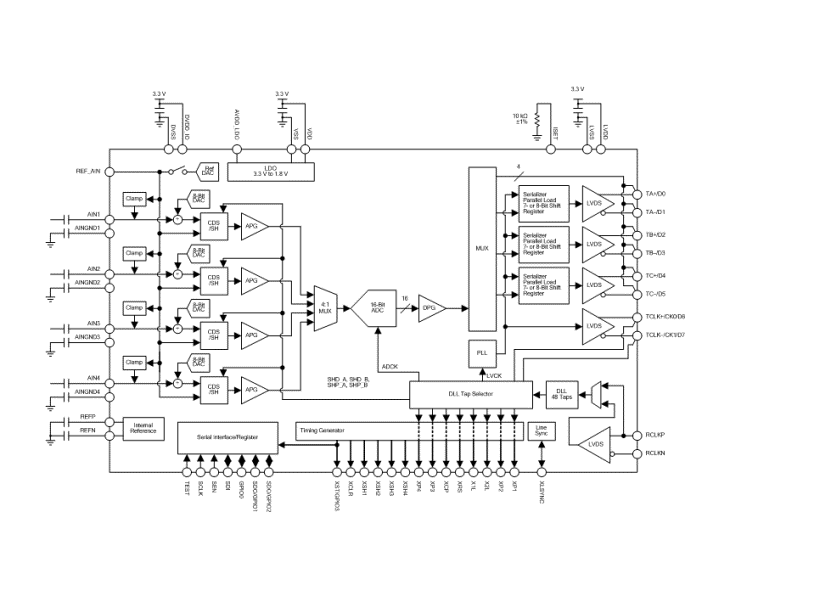

VSP5610/11/12是高速、高性能的16位模数转换器(ADC),拥有四个独立采样电路通道,用于多输出电荷耦合器件(CCD)和互补金属氧化物半导体(CMOS)线传感器。传感器的像素数据通过采样/保持(SH)或相关双采样器(CDS)电路采样,然后由ADC转换为数字数据。数据输出可在低电压差分信令(LVDS)或CMOS模式下选择。

*附件:vsp5610.pdf

VSP5610/11/12 包含可编程增益,以支持亮度引起的像素级曲折。集成的数字转模拟转换器(DAC)可用于调整模拟输入信号的偏移电平。此外,这些设备集成了定时发生器(TG)用于传感器工作控制。

VSP5610/11/12 的磁芯电压为1.65V至1.95V,I/O电压为3.0V至3.6V。铁芯电压由内置低压衰减器(LDO)提供。

特性

- 四通道CCD/CMOS信号:可选择2通道、3通道和4通道

- 电源:仅3.3 V,类型

(内置LDO,3.3 V至1.8 V) - 最大转化率:

- VSP5610:35 MSPS

- VSP5611:50 MSPS

- VSP5612:70 MSPS

- 16位分辨率

- CDS/SH 可选择

- 最大输入信号范围:2.0 V

- 模拟与数字混合增益:

- 模拟增益:0.5 V/V 到 3.5 V/V,每

3/64 V/V 步进 - 数字增益:1 V/V到2 V/V,每

1/256 V/V步进

- 模拟增益:0.5 V/V 到 3.5 V/V,每

- 偏移校正DAC:±250 mV,8位

- 标准LVDS/CMOS可选输出:

- LVDS:数据通道:2通道,3通道时钟通道:1通道8位/7位串行器可选

- CMOS:4位×4,8位×2位

- 定时发生器:

- 快速传输时钟:八个信号

- 慢传时钟:六个信号

- 时序调整分辨率:t

MCLK/48 - 输入钳位/输入参考电平 内部/外部可选

- 参考DAC:0.5 V,1.1 V,1.5 V,2 V

- SPI™:三线串行

- GPIO:四端口

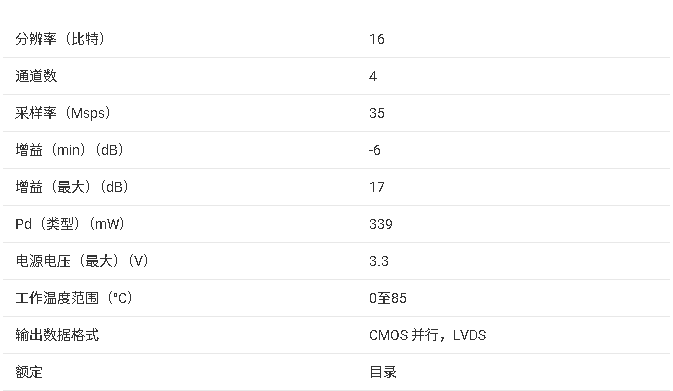

参数

方框图

VSP5610/11/12 是德州仪器(TI)推出的高性能多通道模拟前端芯片系列,核心优势为 16 位高分辨率、2~4 通道灵活配置、集成采样保持 / 相关双采样(SH/CDS)、可编程增益与时序发生器,支持 LVDS/CMOS 双输出模式,是复印机、传真机、扫描仪等办公自动化设备中 CCD/CMOS 线传感器信号采集的专用解决方案。

一、核心产品参数

1. 基础性能指标

- 分辨率与转换率 :16 位分辨率(无失码),三型号核心差异为最大转换率 ——VSP5610(35 MSPS)、VSP5611(50 MSPS)、VSP5612(70 MSPS),单通道最高速率分别达 11.66/16.66/23.33 MHz。

- 静态精度 :微分非线性(DNL)±0.5 LSB,积分非线性(INL)±2 LSB;总绝对增益误差 ±10%,信号完整性优异。

- 信号调理能力 :模拟增益 0.5

3.5 V/V(63 级步进),数字增益 1.02.0 V/V(255 级步进);8 位偏移校正 DAC(±250 mV 范围),适配不同传感器信号幅度。 - 动态性能 :信噪比(SNR)最高 76 dB,通道串扰≤±15 LSB,输入等效噪声低至 0.91 nV/rtHz,弱信号采集能力强。

2. 环境与封装

- 工作温度:0°C~85°C,适配办公设备常规工作环境;

- 封装形式:56 引脚 QFN(RSH 封装),带裸露热焊盘,RoHS 兼容,MSL 等级 3(260°C 回流焊 168 小时);

- 功耗表现:VSP5612 LVDS 输出模式功耗 542 mW,待机模式仅 15 mW,功耗与性能均衡;

- 供电电压:单 3.3 V 供电,内置 LDO 将核心电压转换为 1.8 V,简化供电设计。

二、关键功能特性

1. 采样与信号调理

- 采样模式:支持 CDS(相关双采样)与 SH(采样保持)模式,CDS 可抑制 CCD 复位噪声,SH 适配 CMOS/CCD 传感器,通道独立配置。

- 输入钳位:支持像素钳位、行钳位、无钳位三种模式,钳位电平可选择固定 2.2 V、内部 DAC 输出(0.5/1.1/1.5/2.0 V)或外部输入,适配不同传感器偏置需求。

- 参考与偏移校正:内置参考 DAC(输出精度 ±10%),8 位偏移 DAC 可校正输入信号直流偏移,温度漂移 ±2%,稳定性强。

2. 输出与控制

- 输出接口:支持 LVDS(2

3 通道数据 + 1 通道时钟)与 CMOS(4 位 ×4/8 位 ×2)双模式,LVDS 差分输出电压 300400 mV,抗干扰能力强。 - 时序发生器(TG):集成 8 路快速传输时钟、6 路慢速传输时钟,时序调整分辨率 tMCLK/48,可直接驱动传感器工作,无需外部时序芯片。

- 串行接口:3 线 SPI 控制,支持寄存器读写配置;4 路 GPIO,扩展灵活。

三、产品差异与选型

| 型号 | 最大转换率 | 单通道最高速率 | 典型功耗(LVDS 模式) | 核心适配场景 |

|---|---|---|---|---|

| VSP5610 | 35 MSPS | 11.66 MHz | 339 mW | 低速率扫描仪、入门级复印机 |

| VSP5611 | 50 MSPS | 16.66 MHz | 426 mW | 中速办公设备、传真机 |

| VSP5612 | 70 MSPS | 23.33 MHz | 542 mW | 高速扫描仪、高端复印机 |

四、应用与设计要点

1. 典型应用场景

- 办公自动化:复印机、传真机、平板扫描仪的线阵 CCD/CMOS 传感器信号采集;

- 工业检测:低速率工业条码扫描、小型图像采集模块。

2. 硬件设计建议

- 外部元件 :VDD/DVDD_IO/LVDD 引脚需就近并联 0.1 μF 去耦电容;ISET 引脚外接 10 kΩ±1% 电阻,稳定内部参考电压。

- 信号布线:模拟输入(AINx)与地(AINGNDx)差分布线,减少串扰;LVDS 输出线对长度匹配,降低信号失真。

- 通道配置:根据传感器通道数选择 2/3/4 通道模式,通过 AIN_CH_SEL 寄存器配置;CDS 模式适配 CCD,SH 模式适配 CMOS,按需切换。

3. 软件与配置

- 增益选择:弱信号场景选高模拟增益(如 3.5 V/V),避免数字增益引入噪声;强信号场景选低增益,防止信号饱和。

- 时序配置:通过内部寄存器设置 TG 时钟参数,同步传感器的行周期与像素周期;CLPDM 周期配置在虚拟像素或光学黑像素区间,提升钳位稳定性。

五、产品优势与适配性

- 核心优势:高度集成 SH/CDS、增益调节、时序发生器,减少外部元件;支持 LVDS/CMOS 双输出,适配不同后端处理芯片;单电源供电,简化系统设计。

- 选型建议:根据设备扫描速率需求选择型号 —— 低速设备选 VSP5610,中高速设备选 VSP5611/12;需长距离传输选 LVDS 输出,短距离低成本场景选 CMOS 输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

LM98722 3 通道 16 位 45MSPS 模拟前端(AFE)产品手册总结2025-11-21 1401

-

VSP5621 16 位 4 通道 CCD/CMOS 传感器模拟前端技术文档总结2025-11-18 932

-

AFE2256 256 通道模拟前端技术文档总结2025-11-11 757

-

类比半导体的模拟前端AFE型号有哪些2025-10-31 607

-

AFE539A4 10 位智能模拟前端技术总结2025-10-28 648

-

Texas Instruments AFE159x 4通道24位模拟前端(AFE)数据手册2025-07-06 1023

-

在做CCD的模拟信号采集硬件电路的设计?2025-01-21 390

-

VSP5610/VSP5611/VSP5612 16位 4通道CCD/CMOS传感器模拟前端数据表2024-07-31 521

-

LMP90080-Q1多通道16位传感器模拟前端(AFE)数据表2024-07-26 441

-

VSP5000双通道CCD信号前端数据表2024-07-23 428

-

VSP2582用于数码相机的CCD模拟前端数据表2024-07-22 446

-

用于成像信号的四通道模拟前端VSP7500和VSP7502的详细资料概述2018-05-11 1304

-

基于lm9822的3通道42位彩色扫描仪前端模拟2017-05-18 998

全部0条评论

快来发表一下你的评论吧 !