一种X波段到7mm波段的毫米波宽带四倍频器的设计

描述

引言

毫米波宽带倍频器是毫米波频率合成的关键器件之一,有着广泛的应用背景。倍频器基本都是利用半导体器件的非线性特性产生输入信号的多次谐波,同时配合Balun电桥、谐波提取电路等实现多次倍频信号的输出。目前,半导体器件的非线性电阻或电抗特性是构成倍频器的基础,而容性非线性电抗在实际电路中得到的应用较多,变容二极管、阶跃恢复二极管和FET三端器件都是倍频电路中广泛采用的器件。本文在简要分析非线性倍频理论的基础上,介绍了一种毫米波宽带倍频器的工程设计方法。

1 方案分析

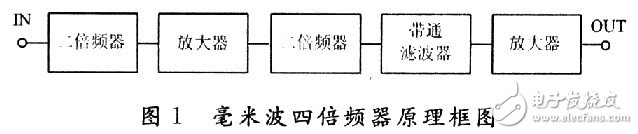

本文主要讨论X波段到7 mm波段的毫米波宽带四倍频器,其指标如下:输入频率8.25~12.5 GHz,功率10~17 dBm;输出频率33~50 GHz,功率大于10 dBm;谐波抑制大于20 dBc;电源+12 V/600 mA;输入接头为SMA-K,输出接头为WR22标准波导,输入、输出相互垂直。

根据指标要求进行分析:在输入功率10~17 dBm时直接实现X波段到7 mm波段的四倍频,倍频损耗太大,提取四次谐波并放大到要求的输出功率难度较大,所以设计采用两次二倍频实现。这样对于每次倍频后需提取的谐波,倍频损耗较少,对放大器要求降低;同时分两次二倍频也有助于提高最后输出的杂波抑制。

四倍频后的输出采用微带到波导的探针过渡,整个倍频器设计在一个小型密封腔体内,由倍频、放大、滤波等多个模块级联而成,便于维修及调试。经过以上分析,最后得到整个毫米波宽带倍频器的原理框图如图1所示。

2 关键电路设计

2.1 二倍频电路

按照方案设计,整个倍频器包含两个二倍频模块,其原理和电路结构相同,这里以8.25~12.5 GHz到16.5~25 GHz的倍频模块为例,介绍二倍频电路的设计方法。

选用二极管作为倍频器件,根据倍频理论,在微波电路中只要并联或串联一个二极管,都会因为其非线性电抗产生倍频作用,配合相应的匹配电路和滤波电路就构成了一个基本的倍频器。但是,这样的倍频器效率较低,实际的倍频器通常都采用多个二极管构成平衡结构,以增强对不需要谐波的抑制,提高倍频效率。

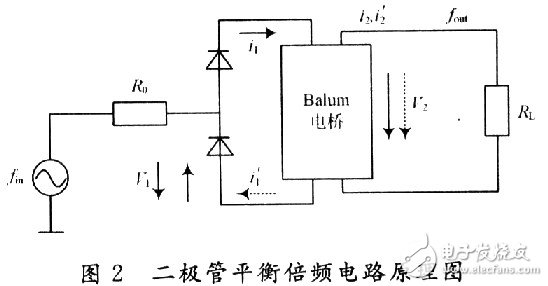

本文也采用平衡倍频电路,两只同样的二极管相对于输入和输出信号分别以反向并联和串联形式接入,原理如图2所示。

该电路实际上是一种全波整流电路,其中输入信号的前半个周期上面一只二极管导通,后半个周期下面一只二极管导通,流经每个二级管的电流分别为

由此可见,输出电流中只包含输入频率的偶次谐波分量,实现了对输入频率偶次倍频。当然以上结果是在电路绝对平衡的情况下得到的,实际电路不可能绝对平衡,电路的性能就会变差。

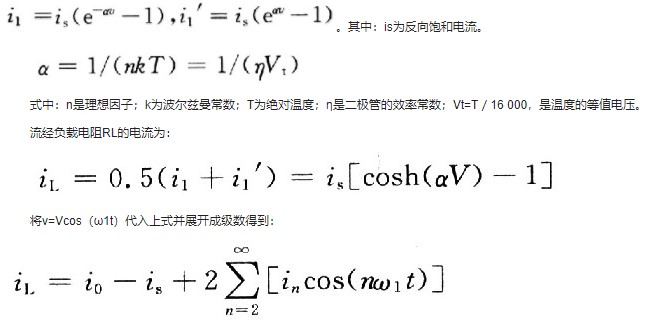

要实现原理图所示的平衡二倍频器,关键电路就是安装反向并联二极管的平衡电路,以及将平衡电路转换成单端输出的Balun电桥。

采用CPW作为安装并联器件的平衡电路,为了与CPW配合,使用槽线到微带的过渡实现Balun电桥。整个电路分上下两面,采用薄膜工艺制作在陶瓷基片上,如图3所示。实线为正面电路,虚线为背面电路。电路尺寸通过在三维仿真软件建模优化得到。

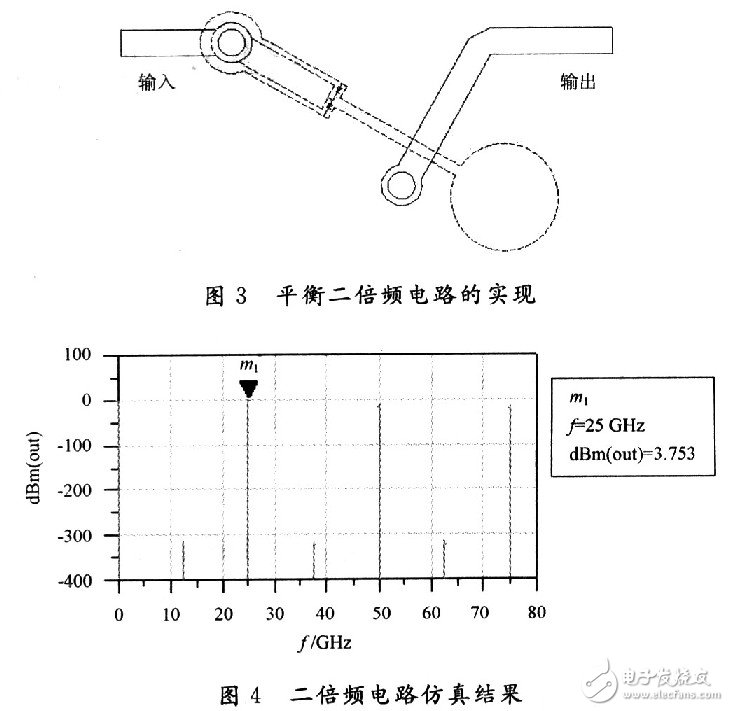

为了提高二极管的一致性以及便于安装,选用T字型封装的梁式引线二极管对,安装在背面CPW和槽线连接处。将整个结构在ADS中进行仿真、优化,结果如图4所示(其中横轴表示输出信号对应的频率,单位:GHz;纵轴表示输出信号的功率,单位:dBm)。

图4的仿真结果是在输入功率+13 dBm情况下得到的,由此可算出倍频损耗为10 dB,满足图1中方案设计的要求。同时由仿真结果可以看出,奇次谐波得到很好的抑制,与理论分析结果一致。

2.2 微带到波导的探针过渡

整个倍频器通过混合集成的工艺实现,最后输出的33~50 GHz信号通过探针过渡,实现微带到波导的输出并保证电路的密封要求。

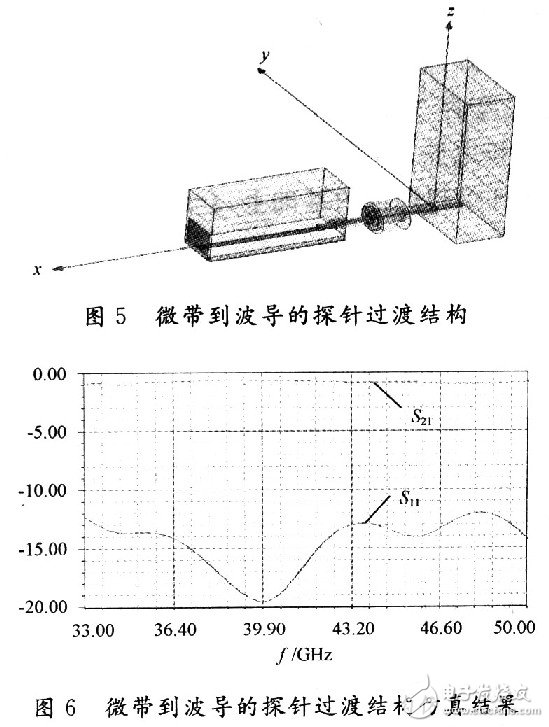

探针过渡结构比较成熟,在HFSS中针对输出频段建模并仿真,即可得到所需的尺寸,如图5、图6所示。

图6中上面一条曲线表示探针过渡结构的S21(dB),下面一条曲线表示探针过渡结构的S11(dB),横轴表示仿真频率33~50 GHz。得到实物后,再根据测试结果做一定调试,就能得到比较满意的结果。

3 测试结果及分析

完成上述关键电路的设计后,再配合模块化的放大器和滤波器,就得到了整个毫米波四倍频器,如图7所示。

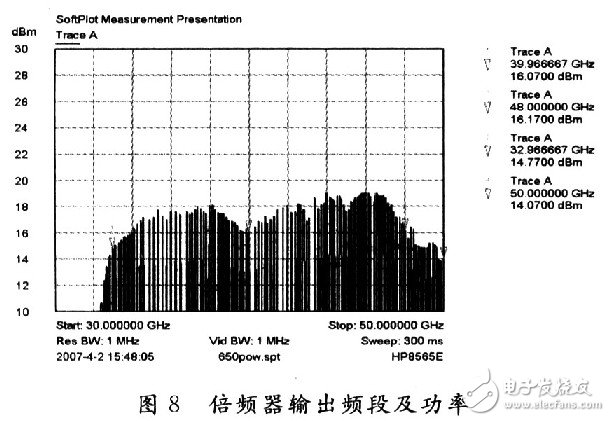

对其关键指标测试,工作带宽及输出功率测试结果如图8所示。

其中横轴表示测试的频率范围为30~50 GHz,纵轴表示输出频谱的功率dBm。可见,该倍频器实现了33~50 GHz频段内的四倍频输出,并且全频段的输出功率均大于10 dBm,满足指标要求。

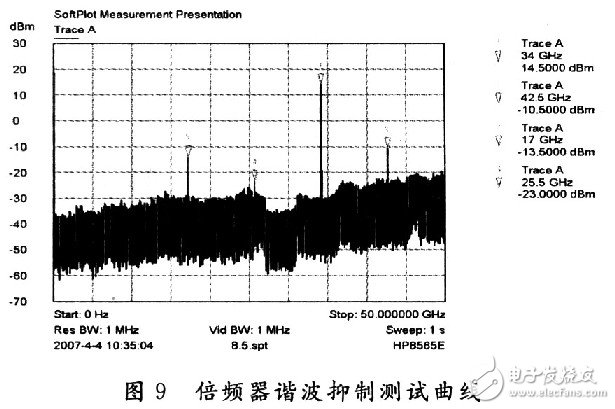

谐波抑制方面,因为该倍频器工作频带较宽,所以低端输入频率的五次谐波会落入工作频带以内,其谐波抑制应该最差,对最差的这种情况进行测试,结果如图9所示。横轴表示输出信号的频率GHz,纵轴表示输出信号的功率dBm。可见,此时的谐波抑制为23 dBc,满足设计要求。

-

E波段毫米波雷达的功率2023-05-04 5730

-

光栅莫尔信号四倍频细分电路模块的设计与仿真研究2022-12-13 3395

-

求大佬分享一种毫米波宽带倍频器的工程设计方法2021-05-31 1765

-

怎么设计220GHz无源三倍频器?2019-08-21 2869

-

基于波导H面的Ka波段宽带功率合成网络分析设计2019-06-19 1977

-

毫米波 W波段检测(FOD)机场跑道异物方案2018-08-04 5267

-

TGC4546-SM具有四倍频器的变频器详细资料免费下载2018-08-02 1157

-

多层LCP技术的毫米波段超宽带槽天线设计2018-03-14 8169

-

W波段宽带倍频器的设计与仿真2013-03-15 1415

-

MMIC毫米波四倍频器研究2011-05-23 959

-

四倍频乘法电路图2009-05-18 802

-

四倍频电路2009-04-26 5280

-

四倍频器电路图2009-04-09 1982

-

Ka波段二倍频器的研究与设计2008-11-17 1405

全部0条评论

快来发表一下你的评论吧 !