ADC16DV160 16 位双通道高速模数转换器(ADC)产品手册总结

描述

该ADC16DV160为单片双通道高性能CMOS 模拟转数字转换器,能够将模拟输入信号转换为16位数字字,在 最高可达160兆采样/秒(MSPS)。该转换器采用差速管式流水线 采用数字纠错和片上采样保持电路以最小化功耗的架构 耗电和外部元件占用率,同时提供出色的动态性能。自动 启动校准实现了卓越的动态性能,并减少了零件间的差异, ADC16DV160可随时通过三线串行外围接口重新校准 (SPI)。集成的低噪声稳定电压参考和差分参考缓冲器 放大器简化了板级设计。片上占空比稳定器,具有低加量抖动 允许广泛的输入时钟占空比范围,同时不影响动态性能。一个独特的 采样保持阶段可提供1.4 GHz的全功率带宽。接口 ADC16DV160和接收模块可以通过固定模式生成轻松验证和优化 以及输出时钟位置特征。数字数据通过双数据率LVDS输出提供—— 这使得68针、10毫米×10毫米的VQFN封装成为可能。ADC16DV160采用双功率运行 电源为+1.8V和+3.0V,并具停电功能以降低功耗至极低 同时允许快速恢复到完全运行。

*附件:adc16dv160.pdf

特性

- 低功耗

- 片上精密参考与采样保持电路

- 芯片上自动校准

- 双数据速率 LVDS 输出端口

- 双电源:1.8V和3.0V工作

- 可选输入范围:2.4 和 2.0 V

PP - 使用时钟分频器(Clock Divider by 2)选项进行采样边缘翻转

- 内部时钟除以1或2

- 片上低抖动值比稳定器

- 关机和睡眠模式

- 输出固定模式生成

- 输出时钟位置调整

- 三线SPI

- 偏移二进制或2补码数据格式

- 68针VQFN封装(10x10x0.8,0.5毫米针距)

主要规格

- 分辨率:16位

- 转换率:160 MSPS

- 信噪比(@FIN = 30 MHz):78 dBFS(典型)

- 信噪比(@FIN = 197 MHz):76 dBFS(典型)

- SFDR(@FIN = 30 MHz):95 dBFS(典型)

- SFDR(@FIN = 197 MHz):89 dBFS(典型)

- 全功率带宽:1.4 GHz(典型)

- 功耗:

- 每信道核心:612 mW(典型)

- LVDS驱动单元:117 mW(典型)

- 总计:1.3W(类型)

- 工作温度范围(-40°C ~ 85°C)

参数

方框图

一、产品核心概述

ADC16DV160 是德州仪器推出的高性能双通道模数转换器(ADC),核心优势为 16 位高分辨率、160 MSPS 高采样率与宽频带特性,适用于多载波多标准基站接收机、高中频采样接收机、分集信道接收机、测试测量设备及通信仪表等场景,工作温度范围为–40°C 至 + 85°C,采用 68 引脚 VQFN 封装(10mm×10mm×0.8mm,引脚间距 0.5mm),支持双电源供电(模拟 3.0V、1.8V,输出驱动 1.8V),集成片内精密基准、采样保持电路及自动校准功能,通过 DDR LVDS 接口输出数据,动态性能优异。

二、关键特性与规格

1. 核心性能参数

- 分辨率与线性度 :16 位分辨率,无丢失码;积分非线性误差(INL)±2.5 LSB,差分非线性误差(DNL)+0.7/-0.2 LSB;偏移误差 0.1% FS,增益误差 ±1.0% FS。

- 动态性能 :30MHz 输入时信噪比(SNR)典型值 78 dBFS,197MHz 输入时典型值 76 dBFS;30MHz 输入时无杂散动态范围(SFDR)典型值 95 dBFS,197MHz 输入时典型值 89 dBFS;总谐波失真(THD)低至–85 dBFS(197MHz 输入),全功率带宽 1.4 GHz。

- 时序与噪声 :采样时钟频率范围 20

160 MSPS,孔径抖动 80 fs rms;流水线延迟 11.5 个时钟周期,数据建立时间 1.57 ns,保持时间 1.55 ns;LVDS 输出差分电压 175325 mV,偏移电压 1.1~1.3 V。 - 功耗与电源 :典型总功耗 1.34 W(160 MSPS),核心每通道功耗 612 mW,LVDS 驱动功耗 117 mW;掉电模式功耗 4.4 mW,休眠模式功耗 60 mW,功耗控制灵活。

2. 核心功能

- 输入与采样:双差分模拟输入,可选输入范围 2.4 VPP 或 2.0 VPP;内置低抖动占空比稳定器,支持 30%~70% 宽输入时钟占空比,无需额外调整。

- 校准与基准:上电自动校准,支持通过 SPI 随时重新校准,降低器件间差异;内置 1.2V 精密电压基准,支持外部基准输入,基准引脚需就近配置去耦电容优化性能。

- 数据输出与格式:DDR LVDS 输出接口,16 位数据分奇偶位双沿传输,需在传输线末端配置 100Ω 终端电阻;支持偏移二进制或二进制补码数据格式,输出时钟(OUTCLK)与采样时钟同频,用于同步数据捕获。

- 控制与扩展:3 线 SPI 接口用于配置寄存器,支持时钟分频(1 或 2 分频)、采样沿翻转、输出时钟相位调整(31°~143°);内置固定模式生成功能,支持 6 种硬件固定模式与 2 种用户自定义模式,便于链路连通性测试。

三、封装与引脚

1. 封装信息

- 68 引脚 VQFN 封装(型号 NKE0068A):尺寸 10mm×10mm×0.8mm,引脚间距 0.5mm,底部裸露焊盘需焊接至接地平面以保证散热与电气性能;MSL 等级 4(260°C 回流焊,72 小时暴露限制),结到环境热阻 19.1 °C/W,结到壳热阻 1.0 °C/W。

2. 关键引脚功能

- 电源与地:VA3.0(模拟 3.0V 供电)、VA1.8(模拟 1.8V 供电)、VDR(输出驱动 1.8V 供电);AGND(模拟地)、DRGND(数字驱动地),裸露焊盘(Pin 0)需接地。

- 模拟输入:VIN+I/VIN-I、VIN+Q/VIN-Q(双通道差分模拟输入);VRPI/VRNI、VRPQ/VRNQ(参考电压输出)、VRM(共模参考电压,典型 1.15V)、VREF(内部 1.2V 基准输出 / 外部基准输入)。

- 时钟与控制:CLK+/CLK-(差分时钟输入,支持单端 AC 耦合驱动);SCLK(SPI 时钟)、SDIO(SPI 数据输入 / 输出)、CSB(SPI 片选,低有效)。

- 数字输出:D1/0±I

D15/14±I、D1/0±QD15/14±Q(LVDS 数据输出);OUTCLK+/OUTCLK-(LVDS 输出时钟)。

四、应用场景与设计支持

1. 典型应用

- 通信系统:多载波 GSM/EDGE、CDMA2000、UMTS、LTE 及 WiMAX 基站接收机,高中频采样接收机,分集信道接收机,满足宽频带、高动态范围信号采样需求。

- 测试测量:便携式仪器、通信仪表,适配高速、高精度信号采集场景,支持宽频率范围信号转换。

2. 设计资源

- 电源与基准:模拟电源需独立供电,VA3.0 应先于 VA1.8 和 VDR 上电,避免过大浪涌电流;各电源引脚就近配置 0.1μF 低 ESL 去耦电容,VREF 引脚去耦电容不得超过 0.1μF,VRP/VRN/VRM 引脚需并联 0.1μF 与 10μF 去耦电容。

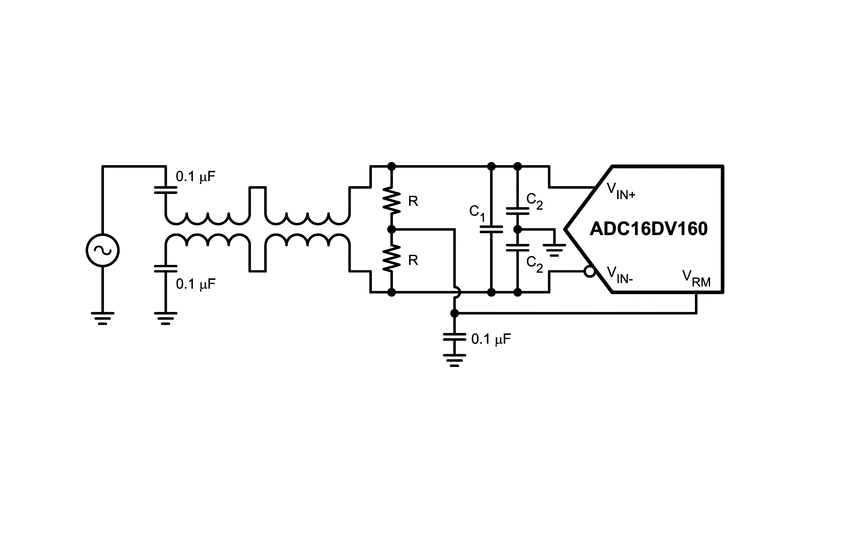

- 输入与时钟:模拟输入推荐使用变压器驱动,低频率场景用磁通变压器,高频率场景用传输线变压器,确保阻抗匹配;时钟输入支持差分或单端驱动,差分驱动可提升抗干扰能力,时钟路径需远离数字信号线,避免噪声耦合。

- 布局与接地:严格分离模拟区与数字区,ADC 置于两区之间;模拟地与数字地单点连接,关键模拟信号(输入、基准、时钟)路径需短且远离数字输出线;变压器等磁性元件避免相邻放置,防止磁耦合。

- 校准与配置:上电自动校准(典型 32 ms@160 MSPS),时钟频率变更后建议重新校准;通过 SPI 配置工作模式(正常、休眠、掉电、固定模式)、输入范围、数据格式等参数,SPI 操作期间需避免噪声耦合影响 ADC 性能。

五、可靠性与订单信息

- 可靠性保障:ESD 防护等级 HBM 2000V、CDM 1250V、MM 200V;存储温度范围–65°C 至 + 150°C,最大结温 150°C,满足工业级应用需求。

- 可订购型号:提供托盘装(168 片 / 盘)、小卷盘装(250 片 / 卷)、大卷盘装(2000 片 / 卷),型号包括 ADC16DV160CILQ/NO.A、ADC16DV160CILQE/NOPB、ADC16DV160CILQX/NOPB 等,均为 RoHS 兼容产品,引脚标识 ADC16DV160。

-

ADC3569 单通道高速模数转换器(ADC)产品文档总结2025-10-23 1285

-

Analog Devices Inc. AD4630-16/AD4632-16双通道16位SAR ADC数据手册2025-06-25 1253

-

ADC16DV160直流分量很大,为什么?2025-01-03 429

-

CBM16AD125-16位,125 MSPS,1.8 V,双通道模数转换器(ADC)2024-09-12 2164

-

ADS8363双通道、16位、1 MSPS模数转换器(ADC)数据表2024-07-30 946

-

ADC32RF45 14位3.0GSPS双通道模数转换器(ADC)数据表2024-07-29 482

-

ADC16V130 16位、130 MSPS模数转换器数据表2024-07-23 552

-

ADC16DV160单芯片双通道高性能CMOS模数转换器数据表2024-07-22 632

-

AD9208双通道、14位、3 GSPS模数转换器(ADC)英文手册2024-07-17 1053

-

ADS8342 4通道、16位模数转换器(ADC)数据表2024-07-16 544

-

LTC2436-1: 双通道差分输入 16 位无延迟 ΔΣ 模数转换器 数据手册2021-03-22 979

-

AD9268: 16位、80 MSPS/105 MSPS/125 MSPS、1.8 V双通道模数转换器(ADC)2021-03-21 1324

-

基于高速双通道模数转换器ADC16DV160芯片的性能特点和应用分析2020-08-10 4669

-

ADS5485 采样率200MSPS 16位单通道模数转换器2008-09-25 2175

全部0条评论

快来发表一下你的评论吧 !