新型低噪声、低失调的电压放大器设计

描述

1 引 言

当今集成电路产业发展日新月异, 芯片尺寸不断缩小, 性能不断优化, 使得对电路中各种基本单元的要求越来越高。对于普遍存在的放大器结构也提出了更高的要求。在差分电容式加速度计传感器中, 放大器噪声和失调电压严重影响着传感器的性能, 设计一种新型低噪声、低失调的电压放大器迫在眉睫。

根据经验可知, 有几种设计方法可以达到低噪声、低失调要求。自动调零技术是最普遍的方法。但它最主要的缺点在于开关的不对称或者补偿不充分。使得开关的非线性不够理想, 导致传感器性能下降。因此需要一种简洁的利用连续时间技术, 在考虑到电路结构及对称性的情况下完成放大器设计。

2 加速度计基本工作原理及放大器对系统性能影响

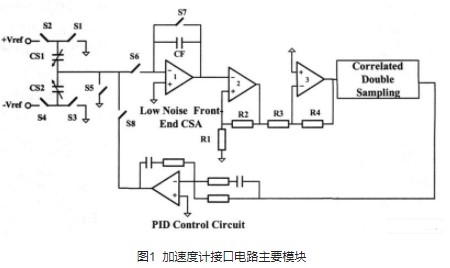

图1给出的电容式加速度计是一个二阶动态系统, 其动态方程为:

其中m 为活动质量块质量, R 为阻尼系数, k 为弹性系数, a 为该系统产生的加速度。

图1 加速度计接口电路主要模块

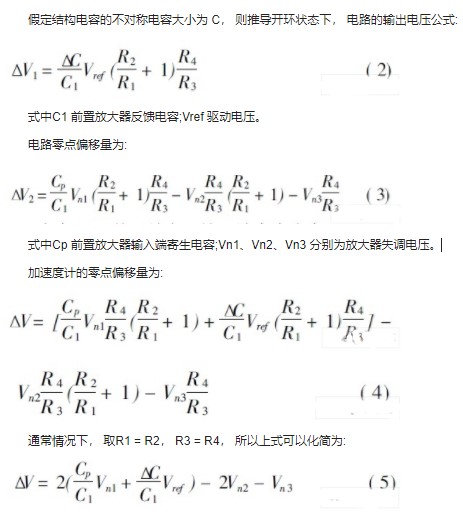

由于放大器的失调和寄生电容的影响, ASIC电路会产生零点失调。而工艺误差, 会引起结构电容不对称, 误差电容一般为几个pF。

Cp 一般为10pF左右, C1 = 5pF, Vref = 9V, C 大概为静态电容的1%。由式( 4)可以看到, 零点偏移量的温度特性和积分电容、寄生电容、误差电容以及运放的失调电压的温度特性有关。积分电容C1 的温度特性与选用材质和工艺参数有关, 不同材质的电容温度特性不同, 采用的多晶硅电容, 相比金属电容, 具有更好的温度特性和较小的漏电流。由于放大器的失调存在于上式中的每一项, 使得它对系统失调有着不可忽略的影响。

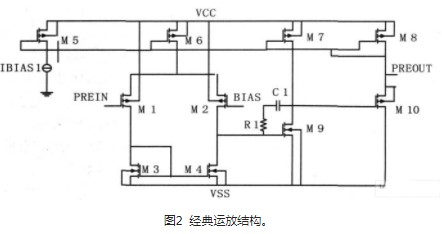

图2中经典运放的结构为经典的两级CMOS差分, 共有三部分组成双端输入单端输出的差分输入级, 反相器输出级, 源跟随级。接5pF负载电容, 开环增益为81. 718dB, 相位裕度60. 018°。

图2 经典运放结构。

重点考虑当放大器产生失调电压和噪声时对系统的影响。

( 1)失调电压。

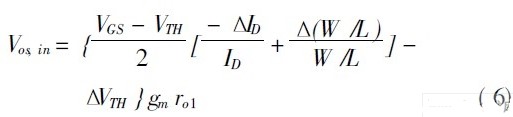

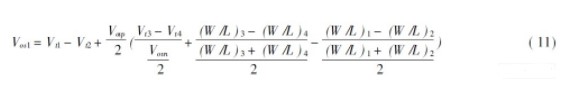

在考虑宽长和阈值电压矢配情况下, 经过计算可得出放大器的输入失调电压为:

它显示了Vos, in对器件失配与偏执条件的依赖关系, 从中可以得出:

a. 晶体管尺寸失配对失调的影响随着平衡过驱动电压的增大而增大。

b. 阈值电压失配直接折合到输入。

( 2)噪声。

放大器器噪声*有2部分组成: 热噪声和1 / f噪声。其中1 / f噪声占主导地位。

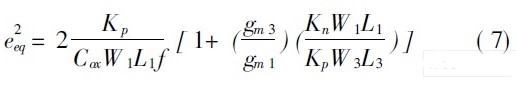

由于第二级和第三级的噪声分量被第一级的增益相除, 因此可以忽略, 等效输入电压的噪声谱密度可近似地表示为:

3 低失调、低噪声放大器

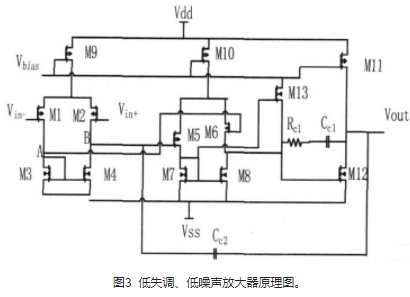

图3为所设计放大器原理图。放大器共有三级组成。第一级(M1- M 4和M9)与第二级(M5- M8和M10)是标准的差分输入单端输出放大器, 第三级为class- A 输出级。从图中可以看到第一级的输出被第二增益级钳位, 使得它们构成了一个比较复杂的增益级。这种钳位使得M5 与M 6管的直流工作点相近, 因此, 第二级使得第一级输出节点电压VA 和VB 的值基本相同。这样一个复杂的增益级形成了一个跟踪系统, 使得放大器的失调电压减小,从而改善了由于外界环境变化所导致的系统不稳定。第一级的负载与第二级形成共源共栅结构, 它们的优点有以下几点: # 在不使用共模反馈的情况下, 节点B的直流偏置就是确定的。高增益的开环钳位电路可以有效的抑制静态工作点失调。? 由于第一级产生的共模信号可以被第二增益级抵消, 从而有效的增加共模抑制比( CMRR)。% 第一和第二级构成的差分结构可确保由晶体管漏电流产生的共模失调会被抵消。

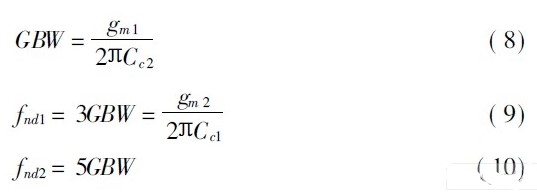

放大器利用2 个补偿电容CC1 和CC2 构成Nested- M iller补偿。

其中:

fnd代表极点, GBW 为单位增益带宽。

电容RC1是用来改善放大器的相位裕度。在输出级的晶体管M13可有效增大大信号的摆率。

4 电路主要参数设计

( 1)低失调电压设计。

由于非理想因素的存在, 电路失调不可避免。

因此, 给出由第一级产生的系统输入失调电压为:

其中Vti是晶体管M i 的阈值电压。Vovp和Vovn分别是差分P管和N 管的过驱动电压。通过公式可以得出若使失调电压下降, 可选择大尺寸的M1和M 2管, 并且减小它们的过驱动电压, 同时再增大M3与M4管的过驱动电压。同理可以得出第二级的失调电压。除了电路参数的设计外, 版图的对称性也会影响失调电压的大小。在版图设计中经常用单位晶体管代替组合晶体管, 这样可有效的减小失调。

较大的晶体管一般会分解成多个单位晶体管。拥有共同质心的单位晶体管会按一个方向放置, 并且对称管会放在相同的井内用以形成相同的外部环境。

( 2)噪声的最佳化。

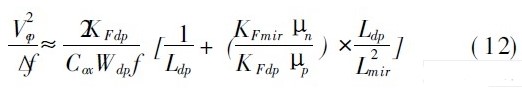

CMOS放大器的噪声由热噪声和1 / f噪声组成。一般1 / f噪声比热噪声要大得多, 因此主要考虑1 / f噪声。由图1结构可得出噪声主要来自系统的第一级, 给出第一级的等效输入噪声:

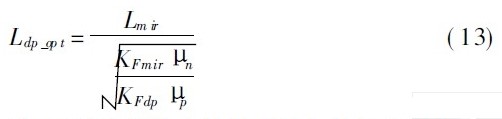

其中脚标n、p分别代表n、p沟道器件, dp代表差分对, m ir代表电流镜。根据公式可以得出Lm ir和Wdp的值越大, 则1 / f噪声越小。在上式中对Ldp求导, 求得的Ldp值就是使输入噪声电压最小的Ldp:

因此, 通过选择恰当的差分输入管的沟道长度,以及较大的Lm ir和Wdp, 就会得到输入参考1 / f噪声的最小值。

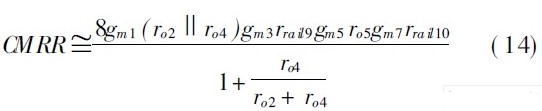

( 3)共模抑制比( CMRR)。

共模抑制比分为静态和动态两种。静态CMRR与电路结构有关, 而动态CMRR 主要于对称器件的不对称性。标准差分放大器的CMRR 大概在60- 80dB, 这是由于一般的不匹配因素在0. 1% 这样的量级上。为了使CMRR 达到100dB 以上, 电路中采用第一级输出与第二级输入构成共源共删, 并使用对称的版图结构。因此, 电路给出的静态CMRR 为:

为了减小适配因素对CMRR的影响, 版图设计中采用共质心的方法, 通过增加版图面积来达到较好对称性的要求。

5 测试及验证

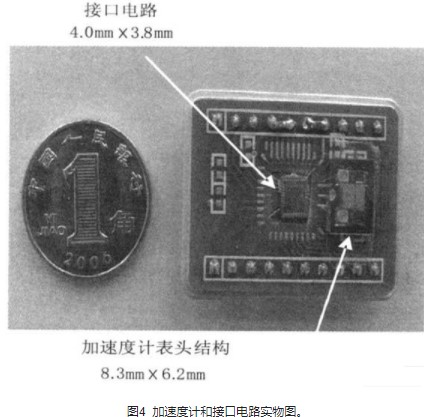

加速度计电路采用0. 5 m 2层多晶2层金属标准模拟CMOS工艺进行了版图设计, 芯片照片如图4所示, 芯片面积为15. 2mm2。

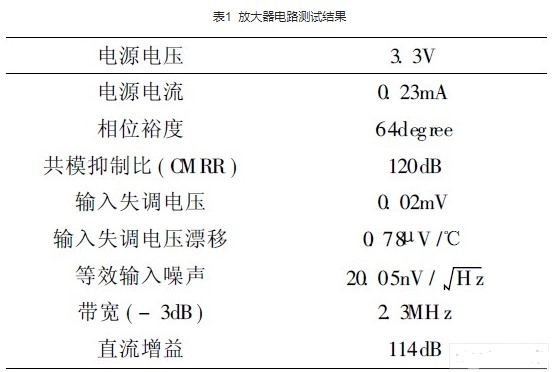

测试结果表明, 放大器在工作电压为3. 3V 时,实测电源电流为0. 23mA。带宽为2. 3MH z, 共模抑制比为120dB, 。在- 45 - 80 , 对放大器的失调电压漂移进行了测试, 可以得出失调电压的温度漂移非常低, 输入参考噪声为20. 05nV /√H z。加速度计的噪声特性和温漂结果得到改善, 采用低噪声放大器使得加速度计的噪声密度为8 g /√ H z, 加速度计在全温区零点变化量在0. 5mV /°C。总体测试结果如表1所示。

6 结束语

为了降低加速度计零点漂移和系统噪声, 设计了一种低失调、低噪声的放大器。芯片采用0. 5 mCMOS工艺实现, 测试结果表明, 放大器输入失调电压温漂为0. 78 V /°C, 等效输入噪声20. 05nV /√Hz, 加速度计噪声仅为8 g / √H z, 全温区零点变化量在0. 5mV/°C, 达到了预期要求。

-

电压放大器的主要指标是什么意思2025-06-12 2784

-

ATA-2082电压放大器,电压放大器指标2017-09-13 2322

-

【转帖】正确选择低噪声放大器2018-12-19 3820

-

BA4510xxx低噪声运算放大器实现0.007%总谐波失真2019-04-02 3112

-

新型宽带低噪声放大器电路设计2019-07-09 2287

-

OP227:双路、低噪声、低失调仪表运算放大器2021-04-22 1413

-

OP227:双路、低噪声、低失调仪表运算放大器数据表2021-05-08 1836

-

安泰电压放大器原理(电压放大器和电荷放大器的优缺点)2022-11-14 2820

-

电压放大器原理(电压放大器适用于什么场合使用)2022-11-17 2574

-

一文解读电压放大器(电压放大器原理)2023-02-27 7143

-

一文带你看懂电压放大器和功率放大器的区别2023-03-22 3993

-

LNLD SP1004差分电压放大器特点2023-03-28 1307

-

电压放大器的用途有哪些2023-08-25 1560

-

Aigtek:电压放大器应用原理介绍2024-12-12 1181

-

MAX4239:低失调/漂移、低噪声的精密SOT23放大器2026-01-26 848

全部0条评论

快来发表一下你的评论吧 !