采用SCL结构的模拟电路设计宽分频比CMOS可编程分频器设计

描述

高速、宽分频范围的可编程频率分频器设计一直是射频频率综合器设计中的难点,它的工作速度限制了频率合成器输出信号的最高频率,它的相位噪声影响频率合成器的带内相位噪声。文中设计的可编程分频器应用于移动数字电视接收机调谐芯片,该芯片兼容了DVB-H、DAB标准,接收的频段覆盖了460~900 MHz,1 400~1 500 MHz这两个频段。根据整个芯片的系统方案设计,可编程分频器的工作频率为2.4~4.0 GHz,实现的分频比范围为240~400,且为连续的。目前高速可编程分频器主要包括基于双模预分频的吞脉冲分频器和基于基本分频单元的多模分频器两种结构,前者因高速、结构简单等特点,被广泛应用在射频频率综合器当中,同时,整个可编程分频器单元模块都采用基于源极耦合(SCL)结构的模拟电路实现,相对于在低频分频部分采用数字标准单元具有噪声低、版图面积小等优点。检测和置数逻辑时序的设计是可编程分频器设计的重点,它直接影响到分频器的工作频率。本文中提出一种新的检测和置数逻辑及电路实现,使得整个可编程分频器的工作频率提高了1倍。本文首先给出r可编程分频器设计的整体结构,着重描述了可编程分频器检测和置数逻辑电路的改进方案;最后,给出了版图设计以及电路后仿真结果。

1 可编程分频器的结构

1.1 整体结构设计

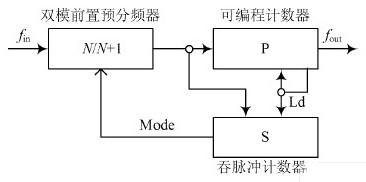

基于双模预分频器的可编程分频器结构如图1所示,它由3部分构成:N/N+1双模前置预分频器、可编程计数器、吞脉冲计数器。

输入的频率首先经过预分频器进行分频,分频比由吞脉冲计数器S给出一个信号Mode进行控制。可编程计数器P和吞脉冲计数器S同时开始减计数,当S计数器减计数减为0时,双模预分频器分频比由N+1变为N,S计数器停止计数,P计数器继续减计数;当P计数器减计数到0时,通过反馈回路使P,S计数器重新置数,开始新一轮的计数。因此在每一次计数过程中首先进行了S次N+1分频,再进行了P-S次N分频,故输出信号为:

分频比M=PN+S。

根据调谐器芯片系统所需要的频率合成范围及精度要求以及采用的TSMC 0.13/μm工艺,该设计将双模前置分频器设计为4/5双模分频器,P计数器为7位、S计数器为2位。因此该可编程分频器可实现的最大分频比为515。

1.2 4/5预分频器结构

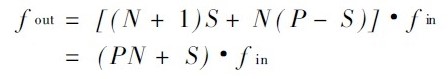

4/5预分频器采用同步计数结构,其结构如图2所示,由3个SCL结构的D触发器和两个与非门构成。Mode信号为分频比控制信号,当Mode为“1”时,预分频器分频比为5,当Mode为“0”时,预分频器分频比为4。由于4/5预分频器直接工作在VCO的输出频率下,是整个可编程分频器工作频率最高的部分,因此这部分的电路设计主要偏重于速度,其功耗是最高的。这部分电路采用SCL结构的模拟电路来实现,SCL结构的电路由开关管对尾电流的导通控制来实现逻辑电平的转换,其工作速度高,满足设计的要求。D触发器由时钟反连的2个D锁存器构成,同时为了减少门延迟以提高工作速度以及降低功耗,将与非逻辑门集成于D触发器内,带有与非逻辑的D触发器电路如图3所示。

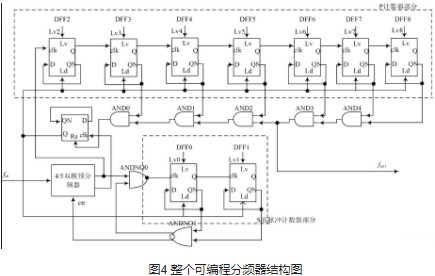

1.3 可编程计数器和吞脉冲计数器设计

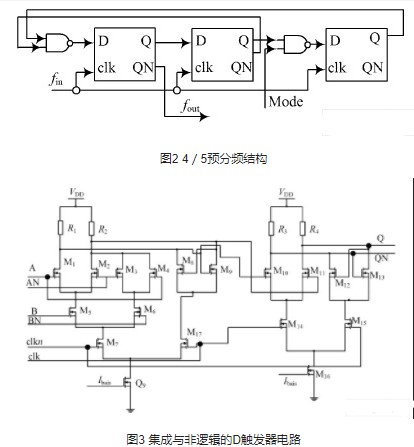

可编程计数器P和吞脉冲计数器S工作在分频器频率较低的频段,采用简单的异步计数器结构实现分频功能。这部分的电路一般有两种实现方式:模拟电路和数字电路,在该设计采用基于SCL的模拟电路来实现,相对于数字电路实现虽然消耗了一定的静态功耗,但电路噪声很低,版图面积小,性能更加好。整个可编程分频器结构如图4所示。

其中P计数器部分由7个带置数功能的D触发器构成;S计数器部分由2个相同的D触发器构成,另外包括2个与非门构成反馈逻辑控制预分频器的分频比;检测和置数逻辑电路由5个与门和1个或门构成。D触发器和逻辑门电路都是由基于SCL结构的模拟电路实现,全差分结构。在P计数器和S计数器中,每个D触发器构成一个2分频器,每个2分频器再级联。检测和置数逻辑的功能是使得P计数器和S计数器计数完后自动置数,这部分的设计很关键,直接影响了整个分频器的工作频率,在本文中提出了一种新的检测和置数逻辑,提高了分频器的工作性能和工作频率。以下通过对比传统的检测置数逻辑和改进后的检测与置数逻辑来说明改进后的优势。

1.3.1 传统的检测与置数逻辑设计

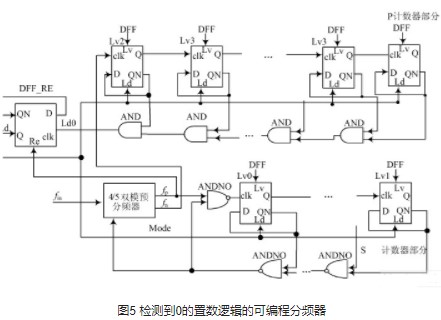

在传统的基于双模分频器的可编程分频器设计中,是对P计数器减计数到0时检测,并通过一定的时序逻辑产生一个置数使能信号使得P计数器和S计数器进行置数。其检测与置数逻辑电路如图5所示,当P计数器减计数到0时,P计数器中每个D触发器Qn端输出都为1,这时级联的与门逻辑输出从0跳变到1,形成一个上升沿(为一个检测信号)。这个上升沿作为带有复位功能的D触发器(DFF-RE)时钟输入,DFF-RE的复位端由4/5预分频器输出控制,即在严格的时序控制下,当检测到P计数器减计数到0时产生一个上升沿信号,此时DFF-RE打开,这个上升沿信号使得DFF-RE输出从0变为1,一段时间后DFF-RE关闭,故形成了一个置数脉冲,使得计数器重新置数。

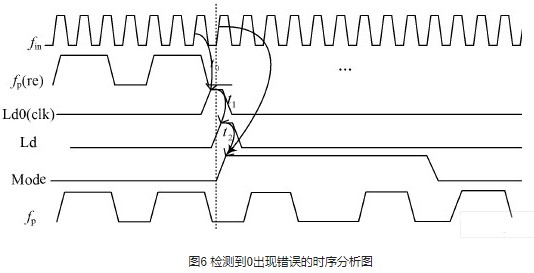

在这种结构中,检测和置数的整个过程必须在输入信号的一个周期内完成,从而限制了分频器的工作频率。下面通过对传统检测置数逻辑的时序分析来说明在输入频率较高时出现掉脉冲的现象,其时序图如图6所示,其中fin为分频器的输入信号,fp为4/5分频器的输出信号,同时作为DFF-RE的复位信号,Ld0为P计数器计数到0时的检测组合逻辑电路输出的信号,Ld为置数使能信号,即DFF-RE的输出信号,Mode为控制4/5分频器分频数的信号。由图中可知,在P计数器减计数到0时,检测逻辑输出一个脉冲(Ld0),从P计数到0到检测脉冲信号产生有一个门延迟的t0,检测脉冲到置数脉冲(Ld)的产生延迟时间为t1,Mode信号的产生延迟为t2。故从检测到Mode信号上升沿的总延迟时间为t0+t1+t2,若这个总延迟时间大于了一个输入信号的周期,如图6所示,Mode信号控制的4/5预分频器本该2次5分频变为1次5分频和1次4分频,从而出现了掉脉冲的现象,最终导致整个分频比错误。

1.3.2 改进的检测与置数逻辑设计

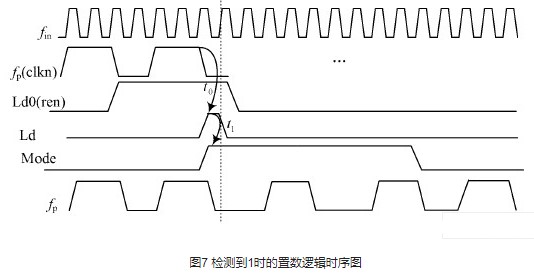

根据系统设计要求,分频器工作的最高频率需达到4.0 GHz,基于传统的检测置数逻辑的分频器很难稳定的工作在此频率下。因此,在该设计采用在P计数器减计数到1检测,通过一定的时序控制下,当P计数器计数到0时置数,这样检测和置数的过程在2个输入脉冲周期内完成,相对于计数到0检测的分频器,工作频率可以提高2倍。以下具体分析改进后的检测置数逻辑时序。在改进后的检测置数逻辑中,如图4所示,当P计数器减计数到0000001时,P计数器中DFF3~DFF7的QN端输出都为1,因此AND0输出由0变为1,AND0输出反相信号作为DFF-RE复位端信号,而4/5分频器输出的反相信号作为DFF-RE的时钟信号。其检测和置数时序逻辑图如图7所示,当检测到P计数到1后,DFF-RE便打开,置数脉冲的产生延迟为t0,Mode信号的产生延迟为t1,故由检测到Mode上升沿信号的总延迟为t1+t2,相比图6,少了一个门延迟,使得4/5预分频器正确的进行了2次5分频,避免了掉脉冲的现象。从对改进的检测置数逻辑时序分析可知,改进后的设计使得可编程分频器能够工作在更高的频率下。

2 电路版图设计及仿真结果

2.1 可编程分频器版图设计

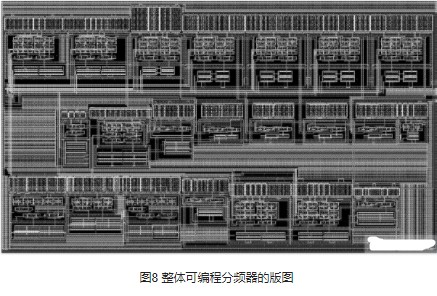

整体可编程分频器的版图如图8所示,由于分频器中各单元电路都是差分结构,需要考虑到器件的匹配设计,同时对单元电路需要合理布局,以减小关键路径的连线延迟和节省版图面积。

2.2 可编程分频器仿真结果

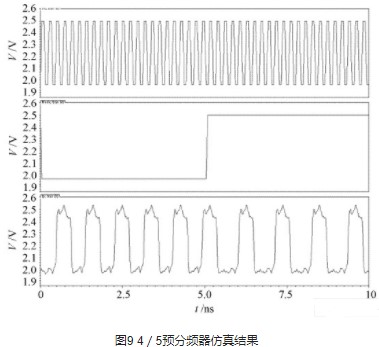

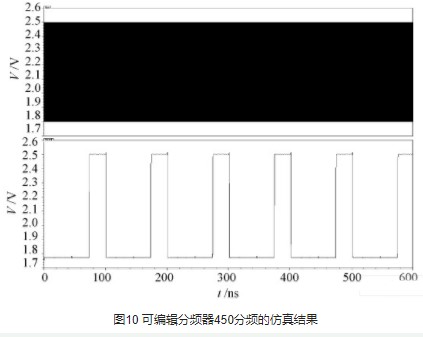

本文的仿真结果是在提取版图寄生参数后,进行后仿真得到的结果。最高工作频率可达4.5 GHz,在工作电压2.5 V下消耗功率约为19 mW。图9是工作频率在4.5 GHz下,4/5分频器的后仿真波形。图10是可编程分频器在4.5 GHz下,分频比为450,P计数器预置数112,S计数器预置数2时的工作波形。从图中可看出整个可编程分频器能够在4.5 GHz下实现正确的分频。

3 结语

对于射频频段的频率综合器,分频器成为了制约环路速度的一个瓶颈。本文通过对吞脉冲结构的可编程分频器的检测和置数逻辑电路的改进,使得分频器的工作速度可以达到4.5 GHz,满足了多标准移动数字电视接收机调谐芯片的系统设计指标,同时由于该分频器具有连续的宽分频比,使其也可应用于其他射频无线收发芯片中。同时,采用SCL结构的模拟电路实现整个可编程分频器使得芯片面积较小,约为106 μm×187μm。

-

SN74LS292和SN74LS294可编程分频器与数字定时器的技术解析2026-03-11 754

-

FPGA学习-分频器设计2023-11-03 3618

-

怎么把小数分频控制字与整数分频控制字结合起来去控制可编程分频器?2021-06-24 1097

-

HMC862A:0.1 GHz至24 GHz,低噪声,可编程分频器数据表2021-04-28 859

-

CD4541可编程分频器参数和电路 电子资料2021-04-14 1852

-

分频器是什么东西_音箱分频器的结构、特点2018-05-25 16094

-

FPGA实现小数分频器2011-11-29 868

-

采用新触发器的高速CMOS前置分频器2011-07-26 753

-

2.4GHz频率合成器可编程分频器设计与实现2010-05-11 935

-

一种通用的可编程双模分频器2010-04-23 687

-

HT49 MCU的可编程分频器(PFD)使用指南2010-03-25 1324

-

可编程分频器电路2010-01-12 4005

-

5G8630输出频率可编程分频器的原理与应用2009-04-28 741

-

CMOS可编程N分频计数器电路图2009-03-29 1142

全部0条评论

快来发表一下你的评论吧 !