采用DDS技术实现无线数据传输系统的数字调制功能设计

描述

DDS 技术是近几年来迅速发展的频率合成技术, 它采用全数字化的技术, 具有集成度高、体积小、相对带宽宽、频率分辨率高、跳频时间短、相位连续性好、可以宽带正交输出、可以外加调制的优点, 并方便与控制器接口构成智能化的频率源。由于基准时钟的频率一般固定, 因此相位累加器的位数决定了频率分辨率, 位数越多, 分辨率越高。基于DDS 诸多优点, 本系统采用DDS技术来实现数字调制功能, 充分发挥DDS 的优势, 使系统结构简单、功能强大。

1 硬件实现及工作原理

本系统为一套无线数据传输系统, 硬件电路分为发射机电路和接收机电路两部分。

1.1 发射机电路

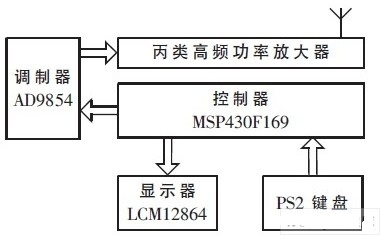

如图1 所示,发射机硬件电路主要由控制器、调制电路、高频功率放大器、天线、显示电路与电源部分组成。

图1 发射机组成图

控制器以TI 公司高性能混合信号处理器MSP430F169为核心, 完成对DDS 、键盘、LCD 显示器的控制和信息处理的功能。MSP430F169 为16 bit 具有精简指令集的超低功耗混合信号处理器(Mixed Signal Processor) , 采用1.8 V~3.6 V 电源电压, 在1 MHz 的时钟条件下运行时,芯片的电流在200 μA~400 μA, 时钟关断模式的最低功耗只有0.2 μA,在8 MHz 晶体驱动下指令周期为125 ns。

且MSP430F169 具有丰富的片上外围模块, 如看门狗、模拟比较器、定时器、串口、硬件乘法器等。在本系统中,MSP430F169 工作在3.3 V 电压、8 MHz 主频下。

调制电路以ADI 公司单片DDS 芯片AD9854 为核心。该芯片最高系统时钟为300 MHz , 理论输出信号频率范围为直流到150 MHz,最高并行编程速率为100 MHz,采用3.3 V 单电源供电, 与上述控制器芯片匹配, 无需加电平转换电路,从而实现控制器与调制器的无缝接口。

AD9854 支持10 MHz 串行通信方式和100 MHz 并行通信方式, 本系统采用串行数据输入方式。AD9854 内置4~20 倍频的PLL, 外部较低频率的参考时钟可通过倍频后得到300 MHz 的系统时钟, 这样就避免了设计高频参考时钟的难度, 降低了高频时钟干扰。AD9854 参考时钟的输入有单端输入和差分输入两种方式, 为了使电路简单, 本设计选用单端输入方式。外部20 MHz 有源晶振输出经PLL 电路15 倍频到300 MHz 后作为系统时钟。

滤波器采用由3 个电感和7 个电容构成的七阶椭圆滤波器, 因为AD9854 的最高工作频率为300 MHz , 而DDS输出最高频率为系统工作频率的40%左右, 所以本方案中滤波器的截止频率设计为120 MHz, 有效滤除了高频干扰,使输出信号较为平滑。

高频功率放大器工作在丙类方式, 能够实现较高的效率。显示器采用LCM128 128×64 点字符点阵液晶显示器, 用来完成人机交互界面和信息的显示功能。电源部分采用LM2576-3.3 三端稳压片, 能够提供最高3 A 的电流输出, 完全满足本系统的要求。同时为了防止AD9854工作时对电源造成干扰, 电路设计采用了大量的滤波电容, 且对数字电源和模拟电源作了很好的隔离, 以防止数字电源对模拟电源的串扰。

1.2 接收机电路

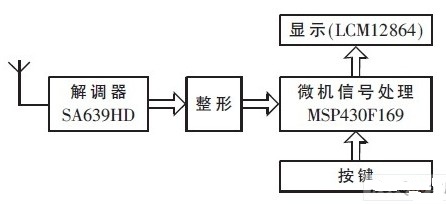

接收机硬件电路由解调电路、数据处理器、显示电路及电源部分组成, 接收机框图如图2 所示。

图2 接收机组成图

解调器以飞利浦专用FSK 解调芯SA639DH 为核心部件。它具有灵敏度高、动态范围大、传输速率快、稳定性好等特点。天线接收到的信号经输入回路取出的2FSK信号与本振信号同时送入乘法器进行混频, 再经一级带通滤波器滤除高频分量取其下变频到中频, 然后进行中频放大后经二级带通滤波送入限幅放大器进行限幅放大。限幅放大后的信号被分成两路, 一路直接送入乘法器, 另一路经移相网络移相90° 产生调相调频波再送乘法器, 两路信号进行相位比较, 乘法器输出的信号经低通滤波器取出原调制信号, 然后再把该信号送入比较器进行整形后送信号处理器进行处理。

接收机数据处理器同样采用MSP430F169 , 显示器采用与发射机相同的LCM12864 。由于接收机部分与发射机相比功耗低, 故接收机电源部分采用两节5 号干电池串联供电。

2 系统软件的实现

2.1 发射机的软件设计

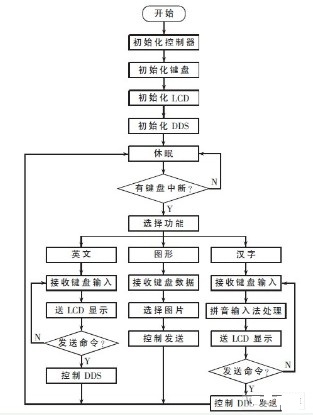

发射机上电后, 首先对系统进行初始化, 包括对控制器本身的端口配置、片内外设的配置, 以及外部的AD9854[ 6]、PS2 键盘和显示器等部件的初始化。初始化结束后系统进入休眠模式, 直到被外部键盘产生的中断唤醒。然后根据得到的按键键码进行相应处理。为了让AD9854 产生2FSK 信号, 需进行如下的初始化过程:S/PSELECT 置1 或置0 以决定输入数据是并行还是串行。1为并行,0 为串行; 本系统采用串行接口, 在SCLK 信号控制下从并行输入口D0~D1 写入48 bit 并行寄存器, 或在SCLK 控制下从串行输入口SDATA 写入48 bit 串行寄存器。发射机的软件流程图如图3 所示( 注: 在发射机内部存储有3 幅图片) 。

图3 发射机流程图

2.2 接收机的软件设计

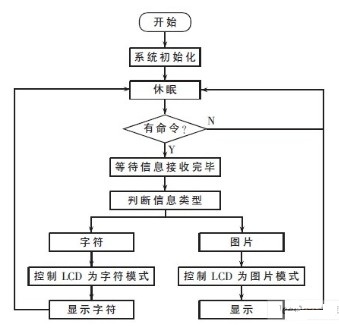

接收机不需要区分接收到的是英文字符还是汉字,故软件设计相对发射机来说较容易。同样, 开始对信号处理器以及外设进行初始化, 使其工作在等待信息接收状态, 此时, 只有接收机射频部分电路工作, 其他部件处于休眠模式。当接收机检查到有信息到来时, 通过中断唤醒控制器, 控制器再唤醒其他外设进行数据接收和处理。接收到的信息经信号处理器判断, 如果为字符( 包括英文字符和汉字) , 则控制LCD 进入字符模式, 进行字符的显示; 如果为图片, 则控制LCD 进入图片模式, 进行图片显示。接收机的软件流程如图4 所示。

图4 接收机流程图

3 系统测试结果

(1) 载波中心频率:发射机在2FSK 模式时,1 和0 所对应的两个频率分别为fH=30.003 000 MHz 和fL=29.997 000 MHz,系统在空闲时发射频率为30.000 000 MHz , 故选取频率为30.000 000 MHz 为中心频率。

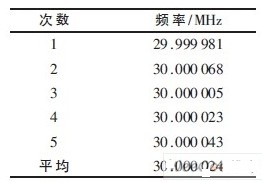

(2) 频率稳定度: 在单片机复位的前提下, 用频率计每隔2 min 测一次AD9854 的输出频率,共测5 次,如表1所示。根据测试结果计算:

表1 AD9854 输出频率测量值

频率稳定度=最大频率偏差/中心频率=(30.000 068-29.999 981)÷30.000 024=0.000 087÷30.000 024=2.9×10-6(3) 发射功率: 在发射功率级末端接50 Ω 假负载,用100 MHz 数字示波器测得发射信号的输出电压峰峰值VP-P, 据公式P=V2P-P/8RL, 得到发射功率值, 实验测得VP-P=2.98 V,P=V2P-P/8RL=22.2 mW。

(4) 传输速率: 发射机、接收机在通信距离为10 m 的情况下, 分别以1.2 kb/s 、9.6 kb/s 、57.6 kb/s 、115.2 kb/s的波特率传送5 次20 个汉字, 汉字错误率均为零。

(5) 图形传送功能: 发射机、接收机。发射机调用机内自带的三幅图形( 分别为公鸡、小兔及西工大校徽) 以点阵的形式传送, 接收机能够不失真接收, 说明本系统具有图形的点阵传送功能。

本系统可以简单高效地进行无线数据传输, 是实现无线通信的一种简单可行的设计方案。经过系统测试,系统技术指标令人满意, 工作可靠。另外, 由于本系统采用DDS 来实现信号调制, 故可以比较容易地改变调制信号频率, 为实现跳频通信提供了方便。

-

基于ARM的无线数据传输系统设计与实现2015-03-26 11868

-

无线数据传输模块的实际应用2019-06-18 3995

-

无线数据传输系统的低功耗怎么实现?2019-08-01 2214

-

高性能MCU和nRF24L01怎么实现无线数据传输?2019-08-16 2022

-

如何利用DSP Builder设计一种适合于软件无线电使用的可控数字调制器2021-04-25 1233

-

如何采用FPGA和CMOS数字传感器实现图像数据传输的图像监测系统?2021-05-26 1504

-

怎么实现基于CDMA的移动无线数据传输系统的设计?2021-05-28 1496

-

如何去构建一种基于单片机的点对点无线数据传输系统2021-12-09 2516

-

采用DataSocket技术实现远程数据传输设计2010-02-26 1183

-

基于ARM的无线数据传输系统设计2010-10-27 523

-

基于AD9851型DDS的数字调制系统设计2010-12-20 645

-

基于RFID技术的矿用无线数据传输系统设计2011-12-05 947

-

基奇AD9851型DDS的数字调制系统设计和实现2016-02-19 883

-

如何实现CC2500无线数据传输?(1)2018-08-10 9004

-

无线数据传输模块的功能特点2021-07-20 2170

全部0条评论

快来发表一下你的评论吧 !