基于CPLD器件和EDA技术实现QDPSK调制解调电路的设计

描述

随着无线通信频带资源的日益紧张,无线通信主要包括微波通信和卫星通信。微波是一种无线电波,它传送的距离一般只有几十千米。但微波的频带很宽,通信容量很大。微波通信每隔几十千米要建一个微波中继站。卫星通信是利用通信卫星作为中继站在地面上两个或多个地球站之间或移动体之间建立微波通信联系。四相相移键控信号简称"QPSK".它分为绝对相移和相对相移两种。由于绝对相移方式存在相位模糊问题,所以在实际中主要采用相对移相方式QDPSK.它具有一系列独特的优点,目前已经广泛应用于无线通信中,成为现代通信中一种十分重要的调制解调方式。在数字信号的调制方式中QPSK四相移键控是目前最常用的一种卫星数字信号调制方式,它具有较高的频谱利用率、较强的抗干扰性、在电路上实现也较为简单。

基带信号是原始的电信号,一般是指基本的信号波形,在数字通信中则指相应的电脉冲。在无线遥测遥控系统和无线电技术中调制就是用基带信号控制高频载波的参数(振幅、频率和相位),使这些参数随基带信号变化。用来控制高频载波参数的基带信号称为调制信号。未调制的高频电振荡称为载波(可以是正弦波,也可以是非正弦波,如方波、脉冲序列等)。

1 QDPSK调制解调的原理

在实际的调谐解调电路中,采用的是非相干载波解调,本振信号与发射端的载波信号存在频率偏差和相位抖动,因而解调出来的模拟I、Q基带信号是带有载波误差的信号。这样的模拟基带信号即使采用定时准确的时钟进行取样判决,得到的数字信号也不是原来发射端的调制信号,误差的积累将导致抽样判决后的误码率增大,因此数字QPSK解调电路要对载波误差进行补偿,减少非相干载波解调带来的影响。此外,ADC的取样时钟也不是从信号中提取的,当取样时钟与输入的数据不同步时,取样将不在最佳取样时刻进行所得到的取样值的统计信噪比就不是最高,误码率就高,因此,在电路中还需要恢复出一个与输入符号率同步的时钟,来校正固定取样带来的样点误差,并且准确的位定时信息可为数字解调后的信道纠错解码提供正确的时钟。校正办法是由定时恢复和载波恢复模块通过某种算法产生定时和载波误差,插值或抽取器在定时和载波误差信号的控制下,对A/D转换后的取样值进行抽取或插值滤波,得到信号在最佳取样点的值,不同芯片采用的算法不尽相同,例如可以采用据辅助法(DA)载波相位和定时相位联合估计的最大似然算法。

2PSK信号与2ASK信号的时域表达式在形式上是完全相同的,所不同的只是两者基带信号s(t)的构成,一个由双极性NRZ码组成,另一个由单极性NRZ码组成。因此,求2PSK信号的功率谱密度时,也可采用与求2ASK信号功率谱密度相同的方法。

在2PSK(二进制绝对移相键控)信号相干解调过程中会产生180°相位模糊,同样,对QPSK信号相干解调也会产生相位模糊问题,并且是0°、90°、180°和270°等4个相位模糊。因此,在实际中更实用的是四相相对移相调制,即QDPSK方式。

QDPSK信号是利用前后码元之间的相对相位变化来表示数字信息。实现四相差分移相调制的方法有正交调幅法和相位选择法。相位选择法QDPSK调制器具有硬件实现简单、价格低等优点,被广泛采用,并且这种调制器非常适合数字电路实现。图1为用相位选择法产生QDPSK信号的组成框图。

图1中首先把二进制数据流经串/并变换,割裂成并列的2行,每串数据的速率是原数据速率的一半;然后对2路信号进行差分编码;四相载波发生器分别送出调相所需的4种不同相位的载波。按照串/并变换器输出的双比特码元的不同,逻辑选相电路输出相位的载波。

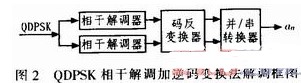

QDPSK的解调有相干解调加码反变换法(极性比较法)和差分相干解调(相位比较法)。QDPSK相干解调加码反变换法解调框图如图2所示。

图2所示解调原理是:对QDPSK信号进行相干解调,恢复出2路相对码,经过码反变换器变换为2路绝对码,再经过并/串转换器,从而恢复出发送的数字信息。在解调过程中,由于载波相位模糊性的影响,使得解调出的相对码也可能发生倒置,但经差分泽码(码反变换)得到的绝对码不会发生任何倒置的现象,从而解决了载波相位模糊性的问题。

2 基于CPLD的QDPSK调制解调电路

2.1 QDPSK调制电路

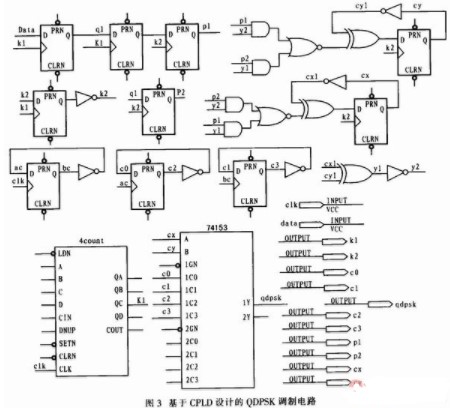

基于CPLD的QDPSK调制电路如图3所示。

图3所示QDPSK调制电路引脚关系为:引脚k1表示数据时钟clk经过计数器4count的八分频输出,引脚k2表示数据时钟k1的二分频输出,引脚ac和bc表示数据时钟clk的二分频输出和二分频反相输出,引脚c0和c2表示数据时钟ac的二分频输出和二分频反相输出,引脚c1和c3表示数据时钟bc的二分频输出和二分频反相输出,c0、c1、c2和c3组成四相载波。引脚cx和cy表示信码数据串并转换后,在同步时钟的作用下差分编码后的输出,引脚qdpsk表示输入的信码数据在同步时钟的作用下四相差分移相键控信号输出。

图3所示电路器件均可从MAX+PLUSⅡ器件库中调用。其中二分频电路涮用1个D触发器和1个非门组成;串并转换电路调用4个D触发器组成;差分编码电路调用2个二异或门、2个D触发器、4个2与门、2个或非门和2个非门组成:四相选相电路调用1个74153组成。调制电路在MAX+PLUSⅡ平台上编译、仿真通过后,打包产生qdpskb组件。

2.2 QDPSK解调电路

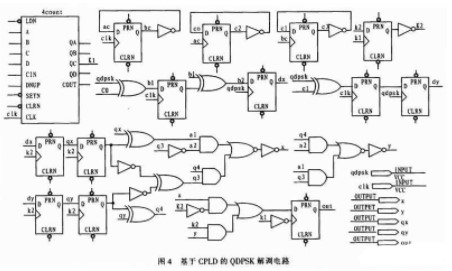

基于CPLD设计的QDPSK解调电路如图4所示。

CPLD(Complex Programmable Logic Device)复杂可编程逻辑器件,是从PAL和GAL器件发展出来的器件,相对而言规模大,结构复杂,属于大规模集成电路范围。是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆("在系统"编程)将代码传送到目标芯片中,实现设计的数字系统。

图4所示QDPSK解调电路引脚关系为:引脚clk表示恢复的数据时钟,引脚k1表示数据时钟clk经过计数器4count的八分频输出,引脚k2表示数据时钟k1的二分频输出,引脚ac和bc表示数据时钟clk的二分频输出和二分频反相输出,引脚c0和c2表示数据时钟ac的二分频输出和二分频反相输出,引脚c1和c3表示数据时钟bc的二分频输出和二分频反相输出,c0、c1、c2和c3组成四相载波。引脚qdpsk表示四相差分移相键控信号输入,引脚qx和qy表示四相差分移相键控信号的相干解调输出。引脚x和y表示相干解调输出在同步时钟的作用下差分译码后的输出,引脚out表示信码差分译码后经并串转换恢复的信码数据输出。

电路器件从MAX+PLUSⅡ器件库中调用。其中二分频电路调用1个D触发器和1个非门组成;相干解调电路调用3个异或门、6个D触发器组成;差分译码电路调用2个D触发器、3个异或门、5个非门、4个与门和2个或非门组成;并串转换电路调用2个非门、2个与门、1个或门和1个D触发器组成。

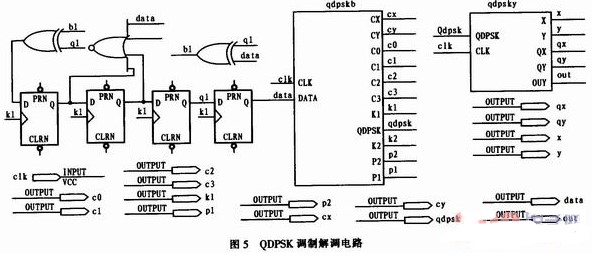

2.3 利用CPLD设计的QDPSK调制解调电路

将设计的QDPSK调制电路"qdpskb"组件和解调电路"qdpsky"组件连接在一起,为了仿真实验方便,信码数据输入采用四级伪随机码电路--从MAX+PLUSⅡ器件库中调用4个D触发器、2个异或门和1个四或非门,解调电路中位定时恢复电路产生的数据时钟直接采用qdpsk调制电路数据时钟,调制解调电路直接相连,组成的QDPSK调制解调电路如图5所示。

QDPSK调制解调电路的引脚关系为:引脚clk表示数据时钟输入,引脚k1表示数据时钟clk的八分频输出,引脚data表示四级伪随机码电路数据输出,引脚c0、c1、c2、c3表示四相载波。引脚p1和p2表示信码数据data在时钟的作用下串并转换后的输出,引脚cx和cy表示差分编码后的输出,引脚qdpsk表示四相差分移相键控信号输出。引脚qx和qy表示四相差分移相键控信号的相干解调输出,引脚x和y表示差分译码后的输出,引脚out表示信码差分译码后经并串转换恢复的信码数据输出。

3 实验结果

利用MAX+PLUSⅡ开发工具建立波形输入文件,在File菜单里面选择New打开新建文件类型对话框,选择Waveform Editor File项,单击"OK".在波形编辑器窗口的Name下单击鼠标右键,出现浮动的菜单,选择Enter Nodesfrom SNF…可以打开"从SNF文件输入观测点"的对话框。在Type区选择Input和Output,在默认的情况下是打开的,单击"List"按钮,可在Available Nodes&Groups区看到设计文件中使用的输入/输出信号,单击"=>"按钮可以将这些信号选择到Selected N0des&Groups区。单击"OK"按钮,关闭对话框即可看到波形编辑窗口,将此波形文件保存为默认名。在波形文件中添加输入/输出信号名后,就可以开始对输入信号建立波形了。QDPSK调制解调电路仿真波形如图6所示。

图6中"clk"表示输入时钟,"c0"、"c1"、"c2"、"c3"表示四相载波。"k1"表示数据时钟clk的八分频输出,"data"表示

四级伪随机码电路数据输出,"p1"、"p2"表示信码数据data串并转换后的输出,"cx"、"cy"表示信码数据串并转换后差分编码的输出,"qdpsk"表示输入的信码数据四相差分移相键控信号输出。"qx"、"qy"表示四相差分移相键控信号的相干解调输出,"x"、"y"表示相干解调输出后差分译码输出,"out"表示信码差分译码后经并串转换恢复的信码数据输出。

仿真结果表明:QDPSK调制电路能正确选相,解调电路输出数据在延时约5.2μs后,与QDPSK调制输入数据完全一致。

将综合后生成的网表文件通过ByteBlaste下载电缆,以在线配置的方式下载到CPLD器件EPM7128SLC84-15中,从而完成了器件的编程。上电后,在输入端加入数据时钟,用数字存储示波器测试调制解调电路输出,实测结果完全正确,表明达到了设计要求。

4 结论

本文利用CPLD器件,设计出的QDPSK调制解调电路,利用了EDA技术中的MAX+PLUSⅡ作为开发工具,将设计的电路图综合成网表文件写入其中,制成ASIC芯片。其突出优点是自顶向下设计,查找和修改错误方便,同时先仿真,正确后再下载测试并应用,具有较大的灵活性;调制和解调放在一块芯片上,集成度非常高;解调电路输出数据延时约5.2μs,数据速率快。本文提出的QDPSK调制解调电路,已应用于小型数据传输系统中。

-

基于VHDL方式实现了QPSK数字调制解调电路的设计2020-12-18 1988

-

如何使用软件无线电实现QDPSK调制解调算法的硬件2020-06-30 1323

-

什么是EDA技术?2019-07-30 2370

-

如何使用SystemView实现4QDPSK调制技术2018-12-29 1733

-

gmsk调制解调matlab如何实现_两种gmsk调制解调方式的实现2018-04-16 17750

-

FM调制/解调电路的设计方案分析2017-10-27 4357

-

信号调制解调电路2016-12-11 1829

-

DPPM调制解调技术的FPGA实现2016-08-08 1216

-

EDA技术应用与发展之管窥2012-09-12 2490

-

FPGA与CPLD实现UART2011-12-17 780

-

基于FPGA的QDPSK调制器的设计2011-05-05 760

-

基于CPLD的QDPSK调制解调电路设计2010-11-22 1227

-

基于F PGA的QPS K调制解调电路设计与实现2009-07-22 736

-

EDA(CPLD/FPGA)技术概述2008-09-24 3396

全部0条评论

快来发表一下你的评论吧 !