采用射频CMOS工艺技术实现肖特基二极管的设计

描述

引言

随着射频无线通信事业的发展和移动通讯技术的进步,射频微波器件的性能与速度成为人们关注的重点,市场对其的需求也日益增多。目前,CMOS工艺是数字集成电路设计的主要工艺选择,对于模拟与射频集成电路来说,选择的途径有多种,例如Si双极工艺、GaAs工艺、CMOS工艺等,在设计中,性能、价格是主要的参考依据。除此以外,工艺的成熟度及集成度也是重要的考虑范畴。

1.概述

对于射频集成电路而言,产品的设计周期与上市时间的缩短都是依赖仿真精确预测电路性能的设计环境的功能。为了使设计环境体现出高效率,精确的器件模型与互联模型是必须要具备的,在设计工具中非常重要,对于射频与模拟技术,器件模型决定了仿真的精度。

采用CMOS工艺,在射频集成电路上的应用时间还补偿,也使得在一些模型方面还不完善。对于射频CMOS集成电路而言,对其影响最大的是寄生参数,在低频环境下,由于对这些寄生参数的忽视,往往使电路的高频性能受到影响。

肖特基二极管具有自身独特的优势,例如快速开关速度和低正向压降。由于这些优异的高频性能,他们有被广泛应用在开机检测离子和微波网络电路中。肖特基二极管通常制作的款式包括n型或p型半导体金属材料,如砷GaAs和SiC.正向偏置的肖特基二极管的性能是由多数载流子器件,少数载流子主要是确定这些p型或n型二极管的属性。为了改善高频性能和集成电路的电源电压减小到现代集成电路,集成的肖特基二极管是很重要的。但可以用于集成肖特基二极管的过程常常是没有现成的,不能和CMOS电路单片集成。以往根据其设计,在标准CMOS工艺基础上制造出肖特基二极管。在本文中,主要针对集成肖特基二极管的设计及实现进行描述,并且基于成本考虑,该标准CMOS工艺基础上肖特基二极管生产工艺不需要任何修改。所测量的结果也符合要求,在SPICE仿真模型中得到验证。

2.CMOS工艺技术

近几十年,因为CMOS技术的发展,也使得在制造射频集成电路时,采用CMOS技术得以实现。但是,因为CMOS制造工艺通常是以数字电路作为导向。面向数字电路设计的CMOS首先由芯片代工厂研发出来,注重功率耗散与时速。

在数字CMOS工艺快速发展成熟以后,在其基础上,通过修改制程与添加掩膜层实现信号的混合及模拟射频CMOS工艺。传统CMOS工艺包含BJTs、MOSFETs以及各种电阻,如扩散电阻、多晶硅电阻及N阱电阻。但是,对于CMOS工艺而言,还应该涵盖各种高频无源器件,例如变容二极管、MIM电容、高Q值电杆及变压器等。

同样,作为肖特基二极管来说,也是CMOS工艺技术的重要环节。例如,需要额外高能离子注入形成深注入N阱降低程度耦合与噪声系数。

需要注意的是,尽管射频CMOS工艺是基于数字CMOS工艺而来,但其不仅仅是添加几层掩膜来实现高频无源器件,对于器件的性能而言,射频工艺与数字工艺的优化目标是不同的,在进行改进的时候,也有可能与传统的CMOS工艺发生冲突。

3.肖特基二极管的工作原理

之所以金属半导体能够形成对垒,主要原因是由于不同的功函数引起的。将金属的功函数定义为技术费米能级与真空能级间的能量差,表示一个起始能量与费米能级相等的电子由金属内部移向真空中所需要的最小能量。该能量需要克服金属晶格与被拉电子与其它电子间的作用,还有一个作用是用来克服金属表面存在的偶极矩。因此,功函数的大小在一定程度上可以表述电子在金属中被束缚的强度。和金属类似,半导体的功函数也被定义为费米能级与真空能级间的能量差,因为半导体的费米能级通常处于禁带中,禁带中一般没有电子,因此该功函数的定义就可以看做是将电子带导带或者价带移向真空能级需要的平均能量。对于半导体来说,还有一个很重要的参数,就是电子亲和能,表示板代替导带底的电子向外逸出所需要的最小能量。

对于肖特基势垒的形成而言,假设现有一块n型半导体和一块金属,两者具有相同的真空电子能级,假设半导体的功函数比金属的功函数小,同时,假设半导体表面无表面态,那么其能带到表面都是平直的。此时,两者就形成一个统一的电子系统,因为金属的费米能级比半导体的费米能级低,因此半导体中的电子就会流向金属,这样金属表面就会带负点,半导体带正电。所带电荷在数值上是等同的,因此对于整个系统来说,还是保持电中性,从而提高了半导体的电势,降低了金属的电势。如果电势发生变化,所有的电子能级及表面电子能级都会随之变化,使之趋于平衡状态,半导体和金属的费米能级在同一水平上时,电子的净流动不会出现。原来的费米能级的差异被二者之间的电势差进行补偿,半导体的费米能级下降。

4.肖特基二极管的设计和布局

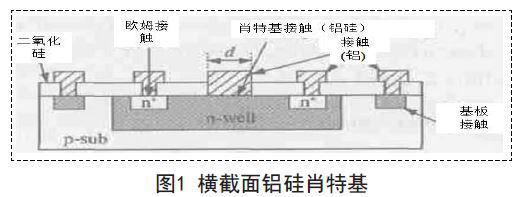

这种设计是基于标准CMOS工艺下,通过MPW在0.35μm工艺中得到实现的。当金属层直接沉积到低掺杂n型或p型半导体区域,形成一个肖特基二极管。当这两种材料彼此接触,由于电势差的存在就会产生一个势垒高度,电子必须克服的电流才能流入。低掺杂的半导体上的金属的阳极和半导体动脉插管,通过欧姆接触在阴极上。在我们的设计中只使用n型肖特基二极管。跨节的Al-Si肖特基二极管如图1所示。

在该设计中,没有出现P+有源区在n阱接触下接触材料是铝面积(等于到dxd)。因此,金属层将直接连接到低掺杂n阱区。其结果是形成了的Al-Si的肖特基二极管接触。对于铸造工艺中需要确定的参数,例如密度、功函数等,只能通过对该区域的肖特基二极管进行控制得以实现,进行二极管的I-V曲线或者其它参数的修改。

根据标准CMOS工艺基础上的肖特基二极管的布局及设计。首先,为了降低肖特基二极管的串联电阻,肖特基和欧姆接触电极之间的距离按照设计规则被设置为最小允许的距离。

其次,采用肖特基二极管布局的方法。交织式的布局为每一个串联电阻提供了并联连接的途径,这是肖特基接触的优势所在。

5.所制作的二极管的测定结果

根据MPW,对肖特基二极管的不同部位通过三种交织方法进行标准C M O S工艺下的0.35μm制造,并对测得的结果进行了讨论。

5.1 I-V的功能

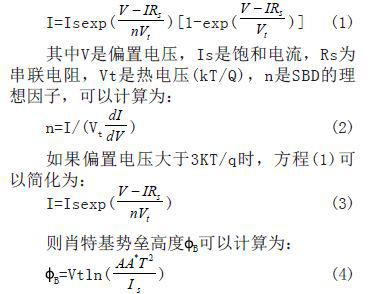

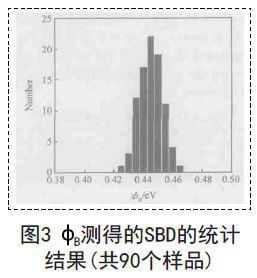

基于对串联电阻的考虑,肖特基二极管的IV功能可表示为:

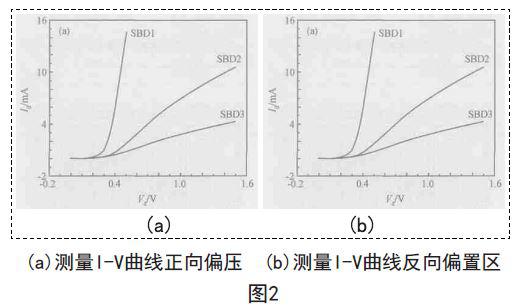

其中A*是有效的理查森常数。

所测量的I-V曲线如图2所示。

(SBD1,SBD2,SBD3分别为16,1.6,0.64μm2)通过拟合公式(3)和所测得的结果,我们可以得到实现SBD的方法,如表1的参数所示。

从表1中可以观察到,随着相互交织的树木的增多,串联电阻的阻值明显的降低。

为实现SBD的测量,势垒高度B的测量的统计结果如图3所示。在所测的90个样本中,SBD1、SBD2、SBD3各30个样本,从而求得实现SBD的势垒高度为0.44eV左右。

击穿电压是4 . 5 V左右,在今后的工作中,在正常的SBD设计与生产中,击穿电压可以延长一些方法的使用,例如在自对准保护环境与SBD的制造过程中,5.2 C-V的功能

下面给出了小信号肖特基二极管的结电容Cj:

其中,Nd为掺杂浓度的n-阱,Φn是费米能级之间的电位差和导带边缘相等于(EC-Ef)/q.

图4显示了测得的反向偏压为SBD的C-V曲线。

5.3 S参数测量和SBD高频建模

为了测量高频率的S参数设计的设备,每个SBD被放置了有三个探头焊盘。中间信号垫的大小是85μm×85μm和顶部/底部的的地面尺寸是85μm×135μm的。使用GSG探头和网络分析仪,我们可以得到S参数设计的SBD.但是,S参数的直接测量结果包括垫片、金属线和覆盖的寄生电容。对于设计的设备而言,尽管寄生参数是非常小的,但这些寄生参数是绝对不能被忽视的,在计算的时候应该将GSG探头直接测量的S参数减去。在本文所研究的设计中,我们制作两个虚拟的GSG信号垫作为测试装置,假如两个信号垫一个是伪GSG信号垫,一个是SBD信号垫,且两个信号垫同等大小。除此以外的虚拟信号垫都是开放的,这也就是我们所说的开放式信号垫。S参数由哑垫进行测量。接着就可以得到信号垫和金属线的寄生电阻和电容。将这些寄生参数减去,就能够得到S参数的无寄生电阻和电容。将这种方法称之为去嵌入技术。

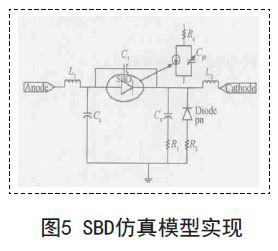

使用测得的S参数可以抽象为高频模拟SPICE模型。图5显示SBD仿真离子模型的实现。L1和L2显示出的输入和输出串联电感。Ci和Co表示阳极输入输出电容和阴极节点。C1具有相互交织的肖特基二极管的两个端口之间的寄生电容。R1和R2为连接S参数下NWLL到地面下电阻的n-阱的模型。pn二极管反映的寄生虫n阱p-次二极管。在我们的设计中,可以用得到的pn二极管的参数通过标准CMOS工艺0.35μm的SPICE模型。

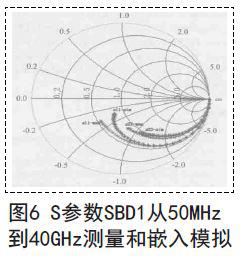

如图6所示,为S参数SBD1测量和模拟。

表2给出了仿真离子模型的参数,频率SBD1从50MHz到40GHz,该模型可以匹配到30GHz的测量结果。

6.结束语

随着无线通讯具有的灵活性和高机动性的特点,其应用越来越广泛,也顺应了市场的需求。由于CMOS工艺在诸多的工艺中最为成熟、成本最低,却功耗最小,因此得到广泛的应用,随着技术的不断成熟,CMOS工艺基础上的肖特基二极管设计及实现也成为现实。也是未来射频集成电路发展的必然趋势。通过MPW在标准CMOS工艺制造的肖特基势垒二极管中的设计应用,可知铝硅接触的势垒高度约0.44eV.

通过I-V,C-V和S参数测量可以实现SBD.通过本文所示,SBD设计的优势较为明显,最为显着的是设计成本较低,能够被广泛的应用与商业标准的CMOS工艺中。在以后的工作中,更多的重点将集中在标准CMOS工艺设计的SBD的反向击穿电压和频率范围扩展。

-

肖特基二极管常见型号 肖特基二极管和普通二极管区别2024-01-30 13064

-

肖特基二极管坏了的表现 肖特基二极管怎么测量好坏2023-09-02 7812

-

肖特基二极管的功能 肖特基二极管的作用2023-08-28 15338

-

什么是肖特基二极管?肖特基二极管的工作原理和作用2023-08-10 14627

-

肖特基二极管2021-06-26 2556

-

肖特基二极管概论2021-06-18 2355

-

肖特基二极管的元件符号_肖特基二极管的优缺点2020-03-20 19182

-

肖特基二极管原理_肖特基二极管作用2019-08-09 9754

-

为什么要选择标准CMOS工艺集成肖特基二极管?2019-08-01 2412

-

肖特基二极管怎么测量_万用表检测肖特基二极管的好坏2018-01-12 62566

-

肖特基二极管与快恢复二极管的区别2016-04-19 4806

-

肖特基二极管,什么是肖特基二极管,肖特基二极管原理2010-02-26 4417

全部0条评论

快来发表一下你的评论吧 !